## Am2960/Am2960-1/Am2960A

Devices

## Cascadable 16-Bit Error Detection and Correction Unit

## DISTINCTIVE CHARACTERISTICS

- Boosts Memory Reliability

Corrects all single-bit errors. Detects all double and some triple-bit errors.

- Very High Speed Perfect for MOS microprocessor, minicomputer, and main-frame systems.

- High performance systems can use the Am2960 EDC in check-only mode to avoid memory system slowdown.

- Handles Data Words From 8 Bits to 64 Bits

The Am2960 EDC cascades: 1 EDC for 8 bits or

16 bits, 2 for 32 bits, 4 for 64 bits.

- Easy Byte Operations

Separate byte enables on the data out latch simplify the steps and cut the time required for byte writes.

- Diagnostics Built-In

The processor may completely exercise the EDC under software control to check for proper operation of the EDC.

#### **GENERAL DESCRIPTION**

The Am2960 Error Detection and Correction Unit (EDC) contains the logic necessary to generate check bits on a 16-bit data field according to a modified Hamming Code, and to correct the data word when check bits are supplied. Operating on data read from memory, the Am2960 will correct any single-bit error and will detect all double and some triple-bit errors. For 16-bit words, 6 check bits are used. The Am2960 is expandable to operate on 32-bit

words (7 check bits) and 64-bit words (8 check bits). In all configurations, the device makes the error syndrome available on separate outputs for data logging.

The Am2960 also features two diagnostic modes, in which diagnostic data can be forced into portions of the chip to simplify device testing and to execute system diagnostic functions.

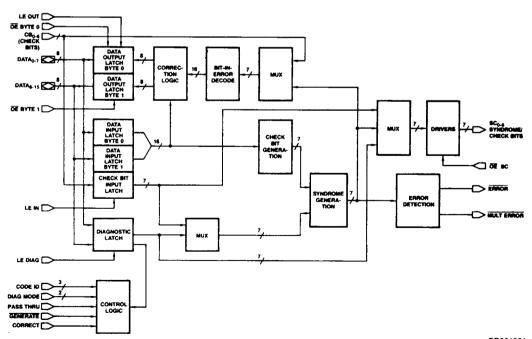

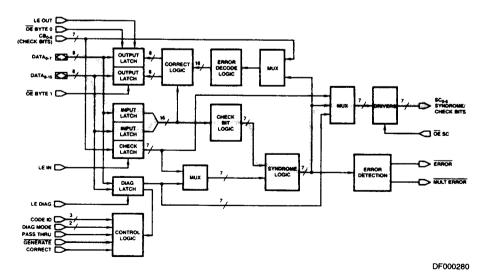

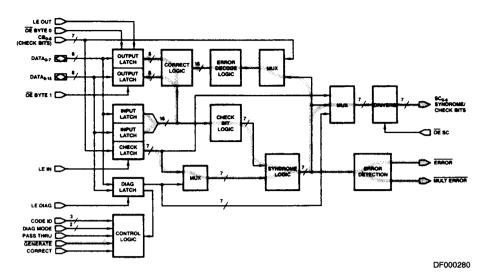

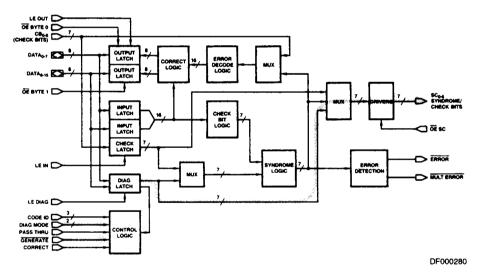

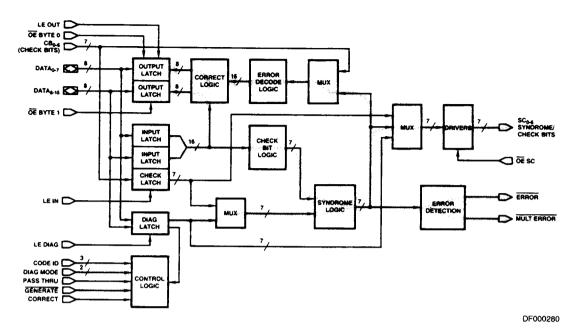

#### **BLOCK DIAGRAM**

BD001261

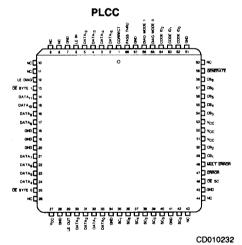

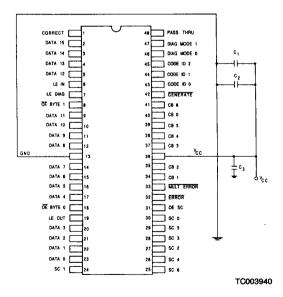

# CONNECTION DIAGRAMS Top View

DIPs\*

\*Also available in Flatpack. Pinout is identical to DIPs.

Note: Pin 1 is marked for orientation.

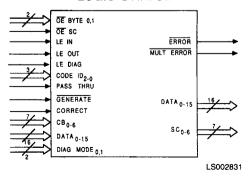

## LOGIC SYMBOL

#### RELATED AMD PRODUCTS

| Part No. | Description                                            |

|----------|--------------------------------------------------------|

| Am29368  | 1M Dynamic Memory Controller                           |

| Am29C60A | 16-Bit CMOS EDC                                        |

| Am2968A  | 256K Dynamic Memory Controller                         |

| Am2969   | Memory Timing Controller w/EDC Control                 |

| Am2971A  | Programmable Event Generator                           |

| Am29C660 | 32-Bit CMOS EDC                                        |

| Am29C668 | 4M - 64K Configurable Dynamic Memory Controller/Driver |

| Am29C983 | 9-Bit x 4-Port Multiple Bus Exchange                   |

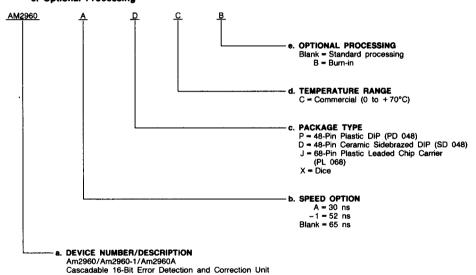

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- - b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Co | ombinations                      |

|----------|----------------------------------|

| AM2960   |                                  |

| AM2960A  | DC, DCB, PC, PCB,<br>XC, JC, JCB |

| AM2960-1 |                                  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

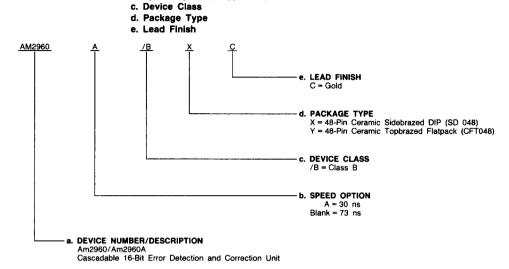

#### **MILITARY ORDERING INFORMATION**

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

b. Speed Option (if applicable)

| Valid Co | mbinations |

|----------|------------|

| AM2960   | /BXC, /BYC |

| AM2960A  | /BAC, /BTC |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### Group A Tests

Group A tests consists of Subgroups: 1, 2, 3, 7, 8, 9, 10, 11

#### PIN DESCRIPTION

#### DATA<sub>0 - 15</sub> Data (Input/Output (16))

These bidirectional data lines provide input to the Data Input Latch and Diagnostic Latch, and receive output from the Data Output Latch. DATA<sub>0</sub> is the least significant bit; DATA<sub>15</sub> the most significant.

#### CBo\_6 Check Bits (Input (7))

The check bit lines are used to input check bits for error detection. Also used to input syndrome bits for error correction in 32 and 64-bit configurations.

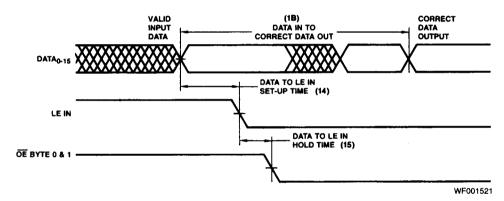

#### LE IN Latch Enable - Data Input Latch (Input)

Controls latching of the input data. When HIGH, the Data Input Latch and Check Bit Input Latch follow the input data and input check bits. When LOW, the Data Input Latch and Check Bit Input Latch are latched to their previous state.

#### GENERATE Generate Check Bits (Input)

When this input is LOW, the EDC is in the Check Bit Generate Mode. When HIGH, the EDC is in the Detect Mode or Correct Mode.

In the Generate Mode the circuit generates the check bits or partial check bits specific to the data in the Data Input Latch. The generated check bits are placed on the SC outputs.

In the Detect or Correct Modes the EDC detects single and multiple errors, and generates syndrome bits based upon the contents of the Data Input Latch and Check Bit Input Latch. In Correct Mode, single-bit errors are also automatically corrected – corrected data is placed at the inputs of the Data Output Latch. The syndrome result is placed on the SC outputs and indicates in a coded form the number of errors and the bit-in-error.

#### SC<sub>0-6</sub> Syndrome/Check Bits (Output (7))

These seven lines hold the check/partial-check bits when the EDC is in Generate Mode, and will hold the syndrome/partial syndrome bits when the device is in Detect or Correct Modes. These are 3-state outputs.

#### OE SC Output Enable, Syndrome/Check Bits (Input) Syndrome/Check Bits. When LOW, the 3-state output lines SC<sub>0-6</sub> are enabled. When HIGH, the SC outputs are in the high impedance state.

#### **ERROR** Error Detected (Output)

When the EDC is in Detect or Correct Mode, this output will go LOW if one or more syndrome bits are asserted, meaning there are one or more bit errors in the data or check bits. If no syndrome bits are asserted, there are no errors detected and the output will be HIGH. In Generate Mode, ERROR is forced HIGH. (In a 64-bit configuration, ERROR must be externally implemented.)

#### MULT ERROR Multiple Errors Detected (Output)

When the EDC is in Detect or Correct Mode, this output if LOW indicates that there are two or more bit errors that have been detected. If HIGH, this indicates that either one or no errors have been detected. In Generate mode. MULT

ERROR is forced HIGH. (In a 64-bit configuration, MULT ERROR must be externally implemented.)

#### CORRECT Correct (Input)

When HIGH, this signal allows the correction network to correct any single-bit error in the Data Input Latch (by complementing the bit-in-error) before putting it into the Data Output Latch. When LOW, the EDC will drive data directly from the Data Input Latch to the Data Output Latch without correction.

#### LE OUT Latch Enable - Data Output Latch (Input)

Controls the latching of the Data Output Latch. When LOW, the Data Output Latch is latched to its previous state. When HIGH, the Data Output Latch follows the output of the Data Input Latch as modified by the correction logic network. In Correct Mode, single-bit errors are corrected by the network before loading into the Data Output Latch. In Detect Mode, the contents of the Data Input Latch are passed through the correction network unchanged into the Data Output Latch. The inputs to the Data Output Latch are unspecified if the EDC is in Generate Mode.

#### OE BYTE 0, 1 Output Enable Bytes 0, 1 (Input)

These lines control the 3-state outputs for each of the two bytes of the Data Output Latch. When LOW, these lines enable the Data Output Latch, and when HIGH these lines force the Data Output Latch into the high impedance state. The two enable lines can be separately activated to enable only one byte of the Data Output Latch at a time.

#### PASS THRU Pass Thru (Input)

This line, when HIGH, forces the contents of the Check Bit Input Latch onto the Syndrome/Check Bit outputs ( $SC_{0-6}$ ) and the unmodified contents of the Data Input Latch onto the inputs of the Data Output Latch.

#### DIAG MODE<sub>0 - 1</sub> Diagnostic Mode Select (Input)

These two lines control the initialization and diagnostic operation of the EDC.

#### CODE ID<sub>2-0</sub> Code Identification (Input)

These three bits identify the size of the total data word to be processed and which 16-bit slice of larger data words a particular EDC is processing. The three allowable data word sizes are 16, 32 and 64 bits and their respective modified Hamming codes are designated 16/22, 32/39 and 64/72. Special CODE ID input 001 (ID2, ID1, ID0) is also used to instruct the EDC that the signals CODE ID2 $_{\rm O}$ , DIAG MODE0 $_{\rm O}$ 1, CORRECT and PASS THRU are to be taken from the Diagnostic Latch, rather than from the input control lines.

#### LE DIAG Diagnostic Latch Enable (Input)

Diagnostic Latch. When HIGH, the Diagnostic Latch follows the 16-bit data on the input lines. When LOW, the outputs of the Diagnostic Latch are latched to their previous states. The Diagnostic Latch holds diagnostic check bits, and internal control signals for CODE ID $_{2-0}$ , DIAG MODE $_{0-1}$ , CORRECT and PASS THRU.

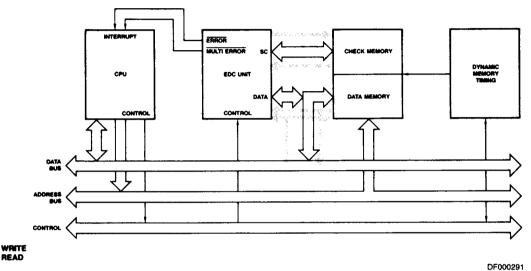

# FUNCTIONAL DESCRIPTION EDC Architecture

The EDC Unit is a powerful 16-bit cascadable slice used for check bit generation, error detection, error correction and diagnostics.

As shown in the block diagram, the device consists of the following:

- Data Input Latch

- Check Bit Input Latch

- Check Bit Generation Logic

- Syndrome Generation Logic

- Error Detection Logic

- Error Correction Logic

- Data Output Latch

- Diagnostic LatchControl Logic

#### Data Input Latch

16 bits of data are loaded from the bidirectional DATA lines under control of the Latch Enable input, LE IN. Depending on the control mode, the input data is either used for check bit generation or error detection/correction.

#### Check Bit Input Latch

Seven check bits are loaded under control of LE IN. Check bits are used in the Error Detection and Error Correction modes.

#### Check Bit Generation Logic

This block generates the appropriate check bits for the 16 bits of data in the Data Input Latch. The check bits are generated according to a modified Hamming code.

#### Syndrome Generation Logic

In both Error Detection and Error Correction modes, this logic block compares the check bits read from memory against a newly generated set of check bits produced for the data read in from memory. If both sets of check bits match, then there are no errors. If there is a mismatch, then one or more of the data or check bits is in error.

The syndrome bits are produced by an exclusive-OR of the two sets of check bits. If the two sets of check bits are identical (meaning there are no errors) the syndrome bits will be all zeroes. If there are errors, the syndrome bits can be decoded to determine the number of errors and the bit-in-error.

#### **Error Detection Logic**

This section decodes the syndrome bits generated by the Syndrome Generation Logic. If there are no errors in either the input data or check bits, the ERROR and MULT ERROR outputs remain HIGH. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, both ERROR and MULT ERROR go LOW.

#### **Error Correction Logic**

For single errors, the Error Correction Logic complements (corrects) the single data bit in error. This corrected data is loadable into the Data Output Latch, which can then be read onto the bidirectional data lines. If the single error is one of the check bits, the correction logic does not place corrected check bits on the syndrome/check bit outputs. If the corrected check bits are needed, the EDC must be switched to Generate Mode.

#### **Data Output Latch**

The Data Output Latch is used for storing the result of an error correction operation. The latch is loaded from the correction logic under control of the Data Output Latch Enable, LE OUT. The Data Output Latch may also be loaded directly from the Data Input Latch under control of the PASS THRU control input.

The Data Output Latch appears as two 8-bit (byte) latches which may be enabled independently for reading onto the bidirectional data lines.

#### **Diagnostic Latch**

This is a 16-bit latch loadable from the bidirectional data lines under control of the Diagnostic Latch Enable, LE DIAG. The Diagnostic Latch contains check bit information in one byte and control information in the other byte. The Diagnostic Latch is used for driving the device when in Internal Control Mode, or for supplying check bits when in one of the Diagnostic Modes.

#### **Control Logic**

The control logic determines the specific mode the device operates in. Normally the control logic is driven by external control inputs. However, in Internal Control Mode, the control signals are instead read from the Diagnostic Latch.

#### **GENERAL OPERATION**

The EDC contains the logic necessary to generate check bits on a 16-bit data field according to a modified Hamming code. Operating on data read from memory, the EDC will correct any single-bit error, and will detect all double and some triple-bit errors. The Am2960 may be configured to operate on 16-bit data words (with 6 check bits), 32-bit data words (with 7 check bits) and 64-bit data words (with 8 check bits). In fact the EDC can be configured to work on data words from 8 to 64 bits. In all configurations, the device makes the error syndrome bits available on separate outputs for error data logging.

#### Code and Byte Specification

The EDC may be configured in several different ways and operates differently in each configuration. It is necessary to indicate to the device what size data word is involved and which bytes of the data word it is processing. This is done with input lines CODE ID<sub>2-0</sub>, as shown in Table I. The three modified Hamming codes referred to in Table I are:

- 16/22 16 data bits

- 6 check bits

- 22 bits in total.

- 32/39 code 32 data bits

- 7 check bits

- 39 bits in total.

- 64/72 code 64 data bits

- 8 check bits

- 72 bits in total.

CODE ID input 001 (ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>) is a special code used to operate the device in Internal Control Mode (described later in this section).

#### **Control Mode Selection**

The device control lines are  $\overline{\text{GENERATE}}$ , CORRECT, PASS THRU, DIAG MODE<sub>0-1</sub> and CODE ID<sub>2-0</sub>. Table 3 indicates the operating modes selected by various combinations of the control line inputs.

#### **Diagnostics**

Table 2 shows specifically how DIAG MODE<sub>0-1</sub> select between normal operation, initialization, and one of two diagnostic modes.

The Diagnostic Modes allow the user to operate the EDC under software control in order to verify proper functioning of the device.

#### Check and Syndrome Bit Labeling

The check bits generated in the EDC are designated as follows:

- 16-bit configuration CX, C0, C1, C2, C4, C8;

- 32-bit configuration CX, C0, C1, C2, C4, C8, C16;

- 64-bit configuration CX, C0, C1, C2, C4, C8, C16, C32.

Syndrome bits are similarly labeled SX through S32. There are only 6 syndrome bits in the 16-bit configuration, 7 for 32 bits, and 8 syndrome bits in the 64-bit configuration.

#### Initialize Mode

The outputs of the Data Input Latch are forced to zero (and the Data Input Latches are latched in zero upon removal of the Initialized mode).

The inputs of the Data Output Latch are forced to zeroes. The check bit outputs (SC) are generated to correspond to the all-zero data. ERROR and MULT ERROR are forced HIGH in the Initialize Mode.

Initialize Mode is useful after power up when RAM contents are random. The EDC may be placed in initialize mode and its' outputs written in to all memory locations by the processor.

TABLE 1. HAMMING CODE AND SLICE IDENTIFICATION

| CODE<br>ID <sub>2</sub> | CODE<br>ID <sub>1</sub> | CODE<br>ID <sub>0</sub> | Hamming Code and Slice Selected |

|-------------------------|-------------------------|-------------------------|---------------------------------|

| 0                       | 0                       | 0                       | Code 16/22                      |

| 0                       | 0                       | 1                       | Internal Control Mode           |

| 0                       | 1                       | 0                       | Code 32/39, Bytes 0 and 1       |

| 0                       | 1                       | 1                       | Code 32/39, Bytes 2 and 3       |

| 1                       | 0                       | 0                       | Code 64/72, Bytes 0 and 1       |

| 1                       | 0                       | 1                       | Code 64/72, Bytes 2 and 3       |

| 1                       | 1                       | 0                       | Code 64/72, Bytes 4 and 5       |

| 1                       | 1                       | 1                       | Code 64/72, Bytes 6 and 7       |

TABLE 2. DIAGNOSTIC MODE CONTROL

| DIAG<br>MODE <sub>1</sub> | DIAG<br>MODE <sub>0</sub> | Diagnostic Mode Selected                                                                                                                                                                                                                                                         |

|---------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                         | 0                         | Non-diagnostic mode. The EDC functions normally in all modes.                                                                                                                                                                                                                    |

| 0                         | 1                         | Diagnostic Generate. The contents of the Diagnostic Latch are substituted for the normally generated check bits when in the Generate Mode. The EDC functions normally in the Detect or Correct modes.                                                                            |

| 1                         | 0                         | Diagnostic Detect/Correct. In the Detect or Correct Mode, the contents of the Diagnostic Latch are substituted for the check bits normally read from the Check Bit Input Latch. The EDC functions normally in the Generate Mode.                                                 |

| 1                         | 1                         | Initialize. The outputs of the Data Input Latch are forced to zeroes (and the Data Input Latches are latched in zero upon removal of the Initialize Mode), inputs of the Data Output Latches are forced to zeroes, and the check bits generated correspond to the all-zero data. |

### HAMMING CODE SELECTION

The Am2960 EDC uses a modified Hamming Code that allows 1) the EDC to be cascaded; 2) all double errors to be detected; 3) the gross error conditions of all 0s or 1s to be detected.

The error correction code can be selected independently of the processor with the exception of diagnostics software.

Diagnostic software run by a processor to check out the EDC system must know specifically which code is being used. This

is only a problem when the EDC replaces an existing MSI implementation on an existing computer. In this case, the computer's software must first determine which of two codes (the old one used by the MSI implementation or the new one used by the EDC) is used by the computer's memory system.

This is easily determined by writing a test data word into memory and then examining whether the generated check bits are typical of the old or the new code. From then on the software runs only the diagnostic appropriate for the code used on that particular computer's memory system.

#### **TABLE 3. OPERATING MODES**

| Operating              | Diagnosti       | c Mode**        | GENERATE               |                        |  |  |

|------------------------|-----------------|-----------------|------------------------|------------------------|--|--|

| Mode                   | DM <sub>1</sub> | DM <sub>0</sub> | 0                      | 1                      |  |  |

| Normal                 | 0               | 0               | Generate               | Correct*               |  |  |

| Diagnostic<br>Generate | 0               | 1               | Diagnostic<br>Generate | Correct*               |  |  |

| Diagnostic<br>Correct  | 1               | 0               | Generate               | Diagnostic<br>Correct* |  |  |

| Initialize             | 1               | 1               | Initialize             | Initialize             |  |  |

| Pass Thru              |                 |                 | is asserted, the       |                        |  |  |

<sup>\*</sup>Correct if the CORRECT Input is HIGH, Detect if the CORRECT Input is LOW.

## **FUNCTIONAL EQUATIONS**

The following equations and tables describe in detail how the output values of the AM2960 EDC are determined as a function of the value of the inputs and the internal states. Be sure to carefully read the following definitions of symbols before examining the tables.

#### **Definitions**

- D<sub>i</sub> ←(DATA<sub>i</sub> if LE IN is HIGH or the output of bit i of the Data Input Latch if LE IN is LOW)

- C<sub>i</sub> —(CB<sub>i</sub> if LE IN is HIGH or the output of bit i of the Check Bit Latch if LE IN is LOW)

- DLi -Output of bit i of the Diagnostic Latch

- S<sub>i</sub> ←Internally generated syndromes (same as outputs of SC<sub>i</sub> if outputs enabled)

- PA -D0+D1+D2+D4+D6+D8+D10+D12

- PB -D0 +D1 +D2 +D3 +D4 +D5 +D6 +D7

- PC ~D8 +D9 +D10 +D11 +D12 +D13 +D14 +D15

- PD +D0+D3+D4+D7+D9+D10+D13+D15

- PE -D0 +D1 +D5 +D6 +D7 +D11 +D12 +D13

- PF -D2+D3+D4+D5+D6+D7+D14+D15

- $PG_1 \leftarrow D0 \oplus D4 \oplus D6 \oplus D7$

- PG<sub>2</sub> ←D1 ⊕D2 ⊕D3 ⊕D5

- PG<sub>3</sub> ← D8 ⊕ D9 ⊕ D11 ⊕ D14

- PG4 D10 + D12 + D13 + D15

#### **Error Signals**

ERROR - (S6 · (ID<sub>1</sub> + ID<sub>2</sub>)) · S5 · S4 · S3 · S2 · S1 · S0 + GENERATE + INITIALIZE + PASSTHRU

MULT ERROR (16 and 32-Bit Modes) ← ((S6 · ID₁) ⊕ S5 ⊕ S4 ⊕ S3 ⊕ S2 ⊕ S1 ⊕ S0) (ERROR) + TOME + GENERATE + PASSTHRU + INITIALIZE

MULT ERROR (64-Bit Modes) - TOME + GENERATE + PASSTHRU + INITIALIZE

<sup>\*\*</sup>In Code ID<sub>2-0</sub>001(ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>) DM<sub>1</sub> and DM<sub>0</sub> are taken from the Diagnostic Latch.

### TABLE 4. TOME (Three or More Errors)\*

|    |            |    |                            |         |             |                  |       |                  | •                |                  |                  |         |                  |         |       |         |         |         |       |

|----|------------|----|----------------------------|---------|-------------|------------------|-------|------------------|------------------|------------------|------------------|---------|------------------|---------|-------|---------|---------|---------|-------|

| S1 | <b>S</b> 2 | S3 | \$0<br>**\$6<br>\$5<br>\$4 | 0 0 0 0 | 1<br>0<br>0 | 0<br>1<br>0<br>0 | 1 0 0 | 0<br>0<br>1<br>0 | 1<br>0<br>1<br>0 | 0<br>1<br>1<br>0 | 1<br>1<br>1<br>0 | 0 0 0 1 | 1<br>0<br>0<br>1 | 0 1 0 1 | 1 0 1 | 0 0 1 1 | 1 0 1 1 | 0 1 1 1 | 1 1 1 |

| 0  | 0          | 0  |                            | 0       | 0           | 0                | 1     | 0                | 1                | 1                | 1                | 0       | 1                | 1       | 1     | 0       | 0       | 0       | 0     |

| 0  | 0          | 1  |                            | 0       | 1           | 1                | 1     | 0                | 0                | 0                | 0                | 0       | 0                | 0       | 0     | 1       | 1       | 1       | 1     |

| 0  | 1          | 0  |                            | 0       | 1           | 1                | 1     | 0                | 0                | 0                | 0                | 0       | 0                | 0       | 0     | 0       | 0       | 0       | 0     |

| 0  | 1          | 1  |                            | 1       | 1           | 1                | 1     | 0                | 0                | 0                | 0                | 0       | 0                | 0       | 0     | 1       | 1       | 1       | 1     |

| 1  | 0          | 0  |                            | 0       | 1           | -                | 1     | 0                | 0                | 0                | ٥                | 0       | 0                | 0       | 0     | 1       | 1       | 1       | 1     |

| 1  | 0          | 1  |                            | 0       | 0           | 0                | 0     | 0                | 0                | 0                | 0                | 0       | 0                | 0       | 0     | 1       | 1       | 1       | 1     |

| 1  | 1          | 0  |                            | 1       | 1           | 1                | 1     | 0                | 0                | 0                | 0                | 0       | 0                | 0       | 0     | 1       | 1       | 1       | 1     |

| 1  | 1          | 1  |                            | 0       | 0           | 0                | 0     | 1                | 1                | 1                | 1                | 1       | 1                | 1       | 1     | 1       | 1       | 1       | 1     |

<sup>\*(</sup>S6, S5,...S0 are internal syndromes except in Modes 010, 100, 101, 110, 111 (CODE ID2, ID1, ID0). In these modes the syndromes are input over the Check-Bit lines. S6-C6, S5-C5, ...S1-C1, S0-C0. \*\*The S6 internal syndrome is always forced to 0 in CODE ID 000.

## **SC Outputs**

Tables 5 to 9 show how outputs  $SC_{0-6}$  are generated in each control mode for various CODE IDs (internal control mode not applicable).

TABLE 5. GENERATE MODE (Check Bits)

| GENERATE<br>Mode (Check Bits) | CODE ID <sub>2-0</sub> |         |                    |                                  |                                  |                                  |                                  |  |  |  |

|-------------------------------|------------------------|---------|--------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--|--|--|

|                               | 000                    | 010     | 011                | 100                              | 101                              | 110                              | 111                              |  |  |  |

| SC <sub>0</sub> ←             | PG2⊕PG3                | PG₁⊕PG₃ | PG₂⊕PG₄⊕CB0        | PG <sub>2</sub> ⊕PG <sub>3</sub> | PG <sub>2</sub> ⊕PG <sub>3</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> |  |  |  |

| SC <sub>1</sub> ←             | PA                     | PA      | PA⊕CB <sub>1</sub> | PA                               | PA                               | PA                               | PA                               |  |  |  |

| SC <sub>2</sub> ←             | PD                     | PD      | PD⊕CB <sub>2</sub> | PD                               | PD                               | PD                               | PD                               |  |  |  |

| SC <sub>3</sub> ←             | PE                     | PE      | PE⊕CB <sub>3</sub> | PE                               | PE                               | PE                               | PE                               |  |  |  |

| SC <sub>4</sub> ←             | PF                     | PF      | PF⊕CB <sub>4</sub> | PF                               | PF                               | PF                               | PF                               |  |  |  |

| SC <sub>5</sub> ←             | PC                     | PC      | PC⊕CB <sub>5</sub> | PC                               | PC                               | PC                               | PC                               |  |  |  |

| SC <sub>6</sub> ←             | 1                      | PB      | PC⊕CB <sub>6</sub> | PB                               | PB                               | PB                               | PB                               |  |  |  |

TABLE 6. DETECT AND CORRECT MODES (Syndromes)

| Detect and Correct |                                         |                                         |                                                      | CODE ID2-0                              |                                  |                                  |                                  |

|--------------------|-----------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------|----------------------------------|----------------------------------|----------------------------------|

| Modes (Syndromes)  | 000                                     | 010                                     | 011*                                                 | 100                                     | 101                              | 110                              | 111                              |

| SC <sub>0</sub> ←  | PG <sub>2</sub> ⊕PG <sub>3</sub><br>⊕C0 | PG <sub>1</sub> ⊕PG <sub>3</sub><br>⊕C0 | PG <sub>2</sub> ⊕PG <sub>4</sub><br>⊕CB <sub>0</sub> | PG <sub>2</sub> ⊕PG <sub>3</sub><br>⊕C0 | PG <sub>2</sub> ⊕PG <sub>3</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> |

| SC <sub>1</sub> ←  | PA⊕C1                                   | PA⊕C1                                   | PA⊕CB <sub>1</sub>                                   | PA⊕C1                                   | PA                               | PA                               | PA                               |

| SC <sub>2</sub> ←  | PD ⊕C2                                  | PD⊕C2                                   | PD⊕CB <sub>2</sub>                                   | PD⊕C2                                   | PD                               | PD                               | PD                               |

| SC <sub>3</sub> ←  | PE⊕C3                                   | PE⊕C3                                   | PE⊕CB <sub>3</sub>                                   | PE⊕C3                                   | PE                               | PE                               | PE                               |

| SC <sub>4</sub> ←  | PF⊕C4                                   | PF⊕C4                                   | PF⊕CB4                                               | PF⊕C4                                   | PF                               | PF                               | PF                               |

| SC <sub>5</sub> ←  | PC⊕C5                                   | PC⊕C5                                   | PC⊕CB <sub>5</sub>                                   | PC⊕C5                                   | PC                               | PC                               | PC                               |

| SC <sub>6</sub> ←  | 1                                       | PB⊕C6                                   | PC ⊕CB <sub>6</sub>                                  | PB                                      | PB                               | PB⊕C6                            | PB⊕C6                            |

<sup>\*</sup>In CODE ID2-0 011 the Check-Bit Latch is forced transparent; the Data Latch operates normally.

TABLE 7. DIAGNOSTIC READ MODE

| Diagnostic        | CODE ID <sub>2-0</sub>                               |                    |                                                      |                    |                                  |                                  |                                  |  |  |  |  |

|-------------------|------------------------------------------------------|--------------------|------------------------------------------------------|--------------------|----------------------------------|----------------------------------|----------------------------------|--|--|--|--|

| Read Mode         | 000                                                  | 010                | 011*                                                 | 100                | 101                              | 110                              | 111                              |  |  |  |  |

| SC <sub>0</sub> ← | PG <sub>2</sub> ⊕PG <sub>3</sub><br>⊕DL <sub>0</sub> | PG₁⊕PG₃<br>⊕DL₀    | PG <sub>2</sub> ⊕PG <sub>4</sub><br>⊕CB <sub>0</sub> | PG2⊕PG3<br>⊕DL0    | PG <sub>2</sub> ⊕PG <sub>3</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> | PG <sub>1</sub> ⊕PG <sub>4</sub> |  |  |  |  |

| SC <sub>1</sub> ← | PA⊕DL <sub>1</sub>                                   | PA⊕DL <sub>1</sub> | PA⊕CB <sub>1</sub>                                   | PA⊕DL <sub>1</sub> | PA                               | PA                               | PA                               |  |  |  |  |

| SC <sub>2</sub> ← | PD⊕DL <sub>2</sub>                                   | PD⊕DL <sub>2</sub> | PD⊕CB <sub>2</sub>                                   | PD⊕DL <sub>2</sub> | PD                               | PD                               | PD                               |  |  |  |  |

| SC <sub>3</sub> ← | PE⊕DL3                                               | PE⊕DL <sub>3</sub> | PE⊕CB <sub>3</sub>                                   | PE⊕DL3             | PE                               | PE                               | PE                               |  |  |  |  |

| SC <sub>4</sub> ← | PF⊕DL4                                               | PF⊕DL <sub>4</sub> | PF⊕CB <sub>4</sub>                                   | PF⊕DL4             | PF                               | PF                               | PF                               |  |  |  |  |

| SC <sub>5</sub> ← | PC⊕DL <sub>5</sub>                                   | PC⊕DL <sub>5</sub> | PC⊕CB <sub>5</sub>                                   | PC⊕DL <sub>5</sub> | PC                               | PC                               | PC                               |  |  |  |  |

| SC <sub>6</sub> ← | 1                                                    | PB⊕DL <sub>6</sub> | PC⊕CB <sub>6</sub>                                   | PB                 | PB                               | PB⊕DL <sub>6</sub>               | PB⊕DL <sub>7</sub>               |  |  |  |  |

<sup>\*</sup>In CODE ID2-0 011 the Check-Bit Latch is forced transparent; the Data Latch operates normally.

TABLE 8. DIAGNOSTIC WRITE MODE

| Diagnostic        | CODE ID <sub>2-0</sub> |                 |                 |                 |     |     |                 |  |  |

|-------------------|------------------------|-----------------|-----------------|-----------------|-----|-----|-----------------|--|--|

| Write Mode        | 000                    | 010             | 011*            | 100             | 101 | 110 | 111             |  |  |

| SC <sub>0</sub> ← | DLo                    | DL₀             | CB <sub>0</sub> | DLo             | 1   | 1   | 1               |  |  |

| SC <sub>1</sub> ← | DL <sub>1</sub>        | DL <sub>1</sub> | CB <sub>1</sub> | DL <sub>1</sub> | 1   | 1   | 1               |  |  |

| SC <sub>2</sub> ⊷ | DL <sub>2</sub>        | DL <sub>2</sub> | CB <sub>2</sub> | DL <sub>2</sub> | 1   | 1   | 1               |  |  |

| SC <sub>3</sub> ← | DL <sub>3</sub>        | DL <sub>3</sub> | CB <sub>3</sub> | DL <sub>3</sub> | 1   | 1   | 1               |  |  |

| SC <sub>4</sub> ← | DL <sub>4</sub>        | DL <sub>4</sub> | CB <sub>4</sub> | DL <sub>4</sub> | 1   | 1   | 1               |  |  |

| SC <sub>5</sub> ⊷ | DL <sub>5</sub>        | DL <sub>5</sub> | CB <sub>5</sub> | DL <sub>5</sub> | 1   | 1   | 1               |  |  |

| SC <sub>6</sub> ← | 1                      | DL <sub>6</sub> | CB <sub>6</sub> | 1               | 1   | DL6 | DL <sub>7</sub> |  |  |

<sup>\*</sup>In CODE ID2-0 011 the Check-Bit Latch is forced transparent; the Data Input Latch operates normally.

TABLE 9. PASS THRU MODE

| PASS THRU         | CODE ID <sub>2-0</sub> |     |                 |     |     |     |     |  |  |

|-------------------|------------------------|-----|-----------------|-----|-----|-----|-----|--|--|

| Mode              | 000                    | 010 | 011*            | 100 | 101 | 110 | 111 |  |  |

| SC <sub>0</sub> ← | C0                     | C0  | CB <sub>0</sub> | C0  | 1   | 1   | 1   |  |  |

| SC <sub>1</sub> ← | C1                     | C1  | CB <sub>1</sub> | C1  | 1   | 1   | 1   |  |  |

| SC <sub>2</sub> ← | C2                     | C2  | CB <sub>2</sub> | C2  | 1   | 1   | 1   |  |  |

| SC <sub>3</sub> ← | C3                     | C3  | CB <sub>3</sub> | C3  | 1   | 1   | 1   |  |  |

| SC <sub>4</sub> ← | C4                     | C4  | CB <sub>4</sub> | C4  | 1   | 1   | 1   |  |  |

| SC <sub>5</sub>   | C5                     | C5  | CB <sub>5</sub> | C5  | 1   | 1   | 1   |  |  |

| SC <sub>6</sub> ⊷ | 1                      | C6  | CB <sub>6</sub> | 1   | 1   | C6  | C6  |  |  |

<sup>\*</sup>In CODE ID2-0 011 the Check-Bit Latch is forced transparent; the Data Input Latch operates normally.

#### **Data Correction**

Tables 10 to 16 shows which data output bits are corrected (inverted) depending upon the syndromes and the CODE ID position. Note that the syndromes that determine data correction are in some cases syndromes input externally via the CB

inputs and in some cases syndromes generated internally by that EDC ( $S_i$  are the internal syndromes and are the same as the value of the  $SC_i$  output of that EDC if enabled).

The tables show the number of data bit inverted (corrected) if any for the CODE ID and syndrome combination.

TABLE 10. CODE ID2-0 = 000\*

| <b>S</b> 2 | S1 | S5<br>S4<br>S3 | 0 0 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1 1 1 |

|------------|----|----------------|-----|-------------|-------------|-------------|-------------|-------------|-------------|-------|

| 0          | 0  |                | -   | -           | -           | 5           | -           | 11          | 14          | _     |

| 0          | 1  |                | -   | 1           | 2           | 6           | 8           | 12          | -           | -     |

| 1          | 0  |                | 1   | -           | 3           | 7           | 9           | 13          | 15          | -     |

| 1          | 1  |                | -   | 0           | 4           | -           | 10          | -           | -           | _     |

<sup>\*</sup>Unlisted S combinations are no correction.

TABLE 11. CODE ID2-0 = 010\*

| СВ | <sub>2</sub> CB | CB <sub>6</sub><br>CB <sub>5</sub><br>CB <sub>4</sub><br>CB <sub>3</sub> | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>0<br>1 | 1<br>0<br>1<br>0 | 1<br>0<br>1<br>1 |

|----|-----------------|--------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-------------|------------------|------------------|------------------|

| 0  | 0               |                                                                          | 1                | 11               | 14               | -                | -           | -                | -                | 5                |

| 0  | 1               |                                                                          | 8                | 12               | -                | -                | -           | 1                | 2                | 6                |

| 1  | 0               |                                                                          | 9                | 13               | 15               | 1                | -           | -                | 3                | 7                |

| 1  | 1               |                                                                          | 10               | -                | -                | _                | _           | 0                | 4                | -                |

<sup>\*</sup>Unlisted CB combinations are no correction.

## TABLE 12. CODE ID2-0 = 011\*

|    |    | S6        | 0 | 0 | 0 | 0 | 1   | 1  | 1  | 1 |

|----|----|-----------|---|---|---|---|-----|----|----|---|

|    |    | S5        | 0 | 0 | 0 | 0 | 1 1 | 1  | 1  | 1 |

|    |    | S4        | 0 | 0 | 1 | 1 | 0   | 0  | 1  | 1 |

|    |    | <b>S3</b> | 0 | 1 | 0 | 1 | 0   | 1  | 0  | 1 |

| S2 | S1 |           |   |   |   |   |     |    |    |   |

| 0  | 0  |           | - | - | - | 5 | -   | 11 | 14 | 1 |

| 0  | 1  |           | - | 1 | 2 | 6 | 8   | 12 | -  | - |

| 1  | 0  |           | - | - | 3 | 7 | 9   | 13 | 15 | _ |

|    |    |           |   |   |   |   |     |    |    |   |

<sup>\*</sup>Unlisted S combinations are no correction.

## TABLE 13. CODE $ID_{2-0} = 100^*$

|                 |     | CB <sub>0</sub> | 0  | 0  | 0  | 0 | 1 | 1 | 1 | 1 |

|-----------------|-----|-----------------|----|----|----|---|---|---|---|---|

|                 |     | CB <sub>6</sub> | 0  | 0  | 0  | 0 | 1 | 1 | 1 | 1 |

|                 |     | CB <sub>5</sub> | 1  | 1  | 1  | 1 | 0 | 0 | 0 | 0 |

|                 |     | CB <sub>4</sub> | 0  | 0  | 1  | 1 | 0 | 0 | 1 | 1 |

|                 |     | CB <sub>3</sub> | 0  | 1  | 0  | 1 | 0 | 1 | 0 | 1 |

| CB <sub>2</sub> | CB. | 1               |    |    |    |   |   |   |   |   |

| 0               | 0   |                 | 1  | 11 | 14 | - | - | - | _ | 5 |

| 0               | 1   |                 | 8  | 12 | -  | _ | - | 1 | 2 | 6 |

| 1               | 0   |                 | 9  | 13 | 15 | - | 1 | - | 3 | 7 |

| 1               | 1   |                 | 10 | -  |    | - | _ | 0 | 4 | - |

<sup>\*</sup>Unlisted CB combinations are no correction.

TABLE 14. CODE ID<sub>2-0</sub> = 101\*

|                 |     | CB <sub>0</sub><br>CB <sub>6</sub><br>CB <sub>5</sub><br>CB <sub>4</sub><br>CB <sub>3</sub> | 00000 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>1 | 0<br>0<br>0<br>1<br>1 | 1<br>1<br>1<br>0<br>0 | 1<br>1<br>1<br>0 | 1<br>1<br>1<br>1<br>0 | 1 1 1 1 |

|-----------------|-----|---------------------------------------------------------------------------------------------|-------|------------------|------------------|-----------------------|-----------------------|------------------|-----------------------|---------|

| CB <sub>2</sub> | CB. | 1                                                                                           |       |                  | l                |                       |                       |                  |                       |         |

| 0               | 0   |                                                                                             | -     | -                | _                | 5                     | -                     | 11               | 14                    | _       |

| 0               | 1   |                                                                                             | -     | 1                | 2                | 6                     | 8                     | 12               | _                     | -       |

| 1               | 0   |                                                                                             | -     | -                | 3                | 7                     | 9                     | 13               | 15                    | -       |

| 1               | 1   |                                                                                             | -     | 0                | 4                | _                     | 10                    | -                | -                     | -       |

<sup>\*</sup>Unlisted CB combinations are no correction.

## TABLE 15. CODE ID2-0 = 110\*

| CB <sub>2</sub> CB | CB <sub>0</sub><br>CB <sub>6</sub><br>CB <sub>5</sub><br>CB <sub>4</sub><br>CB <sub>3</sub> | 1 1 | 0<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0 | 0<br>1<br>0<br>1 | 1<br>0<br>1<br>0<br>0 | 1<br>0<br>1<br>0<br>1 | 1<br>0<br>1<br>1<br>0 | 1<br>0<br>1<br>1 |

|--------------------|---------------------------------------------------------------------------------------------|-----|------------------|-----------------------|------------------|-----------------------|-----------------------|-----------------------|------------------|

| 0 0                | 1                                                                                           | _   |                  | _                     | 5                | _                     | 11                    | 14                    | _                |

| 0 1                | •                                                                                           | _   | 1                | 2                     | 6                | 8                     | 12                    | _                     | -                |

| 1 0                |                                                                                             | _   | -                | 3                     | 7                | 9                     | 13                    | 15                    | -                |

| 1 1                |                                                                                             | -   | 0                | 4                     | _                | 10                    | -                     | -                     | _                |

<sup>\*</sup>Unlisted CB combinations are no correction.

## TABLE 16. CODE ID2-0 = 111\*

| 0.0                    |         | CB <sub>0</sub><br>CB <sub>6</sub><br>CB <sub>5</sub><br>CB <sub>4</sub><br>CB <sub>3</sub> | 0<br>1<br>1<br>0<br>0 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>1<br>0 | 0<br>1<br>1<br>1 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>0 | 1<br>0<br>0<br>1 | 1<br>0<br>0<br>1 |

|------------------------|---------|---------------------------------------------------------------------------------------------|-----------------------|------------------|-----------------------|------------------|------------------|------------------|------------------|------------------|

| <b>CB</b> <sub>2</sub> | O<br>CB | 1                                                                                           | _                     | 11               | 14                    | -                |                  |                  | _                | 5                |

| 0                      | 1       |                                                                                             | 8                     | 12               | -                     | _                | -                | 1                | 2                | 6                |

| 1                      | 0       |                                                                                             | 9                     | 13               | 15                    | -                | -                | _                | 3                | 7                |

| 1                      | 1       |                                                                                             | 10                    | -                | _                     | _                | -                | 0                | 4                | _                |

<sup>\*</sup>Unlisted CB combinations are no correction.

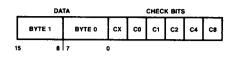

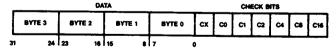

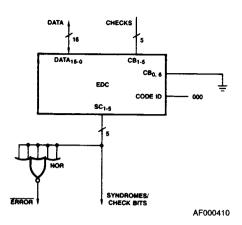

#### 16-BIT DATA WORD CONFIGURATION

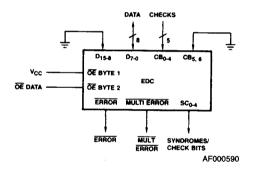

The 16-bit format consists of 16 data bits, 6 check bits and is referred to as 16/22 code (see Figure 5.)

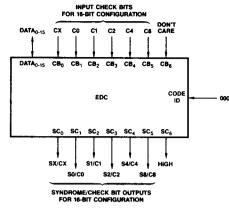

The 16-bit configuration is shown in Figure 6.

#### Generate Mode

In this mode, check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated are placed on the outputs SC<sub>0-5</sub> (SC<sub>6</sub> is a logical one, or high).

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table 17. Each check bit is generated as either an XOR or XNOR of eight of the 16 data bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR is an odd parity check bit.

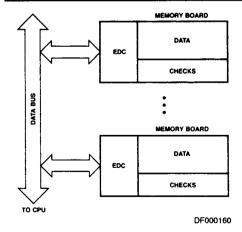

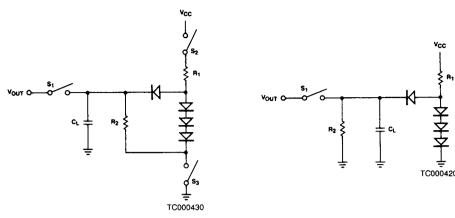

Figure 1 shows the data flow in the Generate Mode.

#### **Detect Mode**

In this mode the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors and some triple-bit errors. If one or more errors are detected, ERROR goes LOW. If two or more errors are detected, MULT ERROR goes LOW. Both error indicators are HIGH if there are no errors.

Also available on device outputs  $SC_{0.5}$  are the syndrome bits generated by the error detection step. The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table 18 gives the chart for decoding the syndrome bits generated by the 16-bit configuration (as an example, if the syndrome bits SX/SO/S1/S2/S4/S8 were 101001, this would be decoded to indicate that there is a single-bit error at data bit 9). If no error is detected, the syndrome bits will all be zeroes.

In Detect Mode, the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without correction.

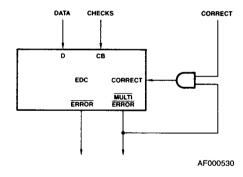

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it onto the inputs of the Data Output Latch. (See Figure 2.) If multiple errors are detected, the output of the correction network is unspecified. If the single-bit error is a check bit, there is no automatic correction. If check bit correction is desired, this can be done by placing the device in Generate Mode to produce a correct check bit sequence for the data in the Data Input Latch.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch, and the contents of the Check Bit Input Latch are placed on outputs  $SC_{0-5}$ . ERROR and MULT ERROR are forced HIGH in this mode.

### **Diagnostic Latch**

The Diagnostic Latch serves both for diagnostic uses and internal control uses. It is loaded from the DATA lines under the control of LE DIAG. Table 19 shows the loading definitions for the DATA lines.

## Diagnostic Generate/Diagnostic Detect/ Diagnostic Correct

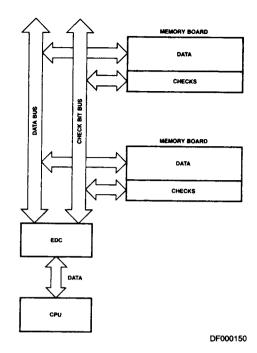

These are special diagnostic modes selected by DIAG MODE<sub>0-1</sub> where either normal check bit inputs or outputs are substituted for by check bits loaded into the Diagnostic Latch (see Table 3 for details). Figures 3 and 4 illustrate the flow of data during the two diagnostic modes.

#### **Internal Control Mode**

This mode is selected by CODE  $ID_{2-0}$  input 001 ( $ID_2$ ,  $ID_1$ ,  $ID_0$ ). When in Internal Control Mode, the EDC takes the CODE  $ID_{2-0}$ , DIAG MODE $_{0-1}$ , CORRECT and PASS THRU control signals from the internal Diagnostic Latch rather than from the external input lines.

Table 19 gives the format for loading the Diagnostic Latch.

Figure 1. Check Bit Generation Data Path

Figure 2. Error Detection and Correction Data Path

Figure 3. Diagnostic Check Bit Generation Data Path

Figure 4. Diagnostic Detect and Correct Data Path

DF000220

Uses Modified Hamming Code 16/22

- 16 data bits

- 6 check bits

- 22 bits in total

Figure 5. 16-Bit Data Format

DF000210

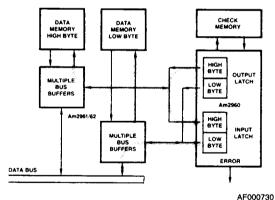

Figure 6. 16-Bit Configuration

#### SYNDROME DECODE TO BIT-IN-ERROR 8-BIT MODE

| Synd<br>Bi | rome<br>its | S4<br>S2 | 0  | 1 0 | 0  | 1 1 |

|------------|-------------|----------|----|-----|----|-----|

| S0         | S1          |          |    |     |    |     |

| 0          | 0           |          | *  | C4  | C2 | 5   |

| 0          | 1           |          | C1 | 3   | ТМ | 7   |

| 1          | 0           |          | CO | 2   | 1  | 6   |

| 1          | 1           |          | ТМ | 4   | 0  | ТМ  |

\* - no errors detected TM - two or more errors

TABLE 17. 16-BIT MODIFIED HAMMING CODE - CHECK BIT ENCODE CHART

| Generated  |            |   |   |   |   |   | Par | ticip | atin | g Da | ata | Bits |    |    |    |    |    |

|------------|------------|---|---|---|---|---|-----|-------|------|------|-----|------|----|----|----|----|----|

| Check Bits | Parity     | 0 | 1 | 2 | 3 | 4 | 5   | 6     | 7    | 8    | 9   | 10   | 11 | 12 | 13 | 14 | 15 |

| СХ         | Even (XOR) |   | Х | Х | Х |   | Х   |       |      | Х    | Х   |      | Х  |    |    | Х  |    |

| C0         | Even (XOR) | Х | Х | Х |   | Х |     | Х     |      | х    |     | Х    |    | x  |    |    |    |

| C1         | Odd (XNOR) | × |   |   | Х | Х |     |       | Х    |      | х   | Х    |    |    | Х  |    | Х  |

| C2         | Odd (XNOR) | X | Х |   |   |   | Х   | Х     | Х    |      |     |      | Х  | X  | х  |    |    |

| C4         | Even (XOR) |   |   | Х | Х | Х | Х   | Х     | Х    |      |     |      |    |    |    | Х  | Х  |

| C8         | Even (XOR) |   |   |   |   |   |     |       |      | X    | X   | Х    | Х  | х  | Х  | Х  | Х  |

The check bit is generated as either an XOR or XNOR of the eight data bits noted by an "X" in the table.

TABLE 18.

SYNDROME DECODE TO BIT-IN-ERROR

| Syı | ndro<br>Bits |    | S8<br>S4<br>S2 | 0 0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1 0 | 0 1 1 | 1 1 1 |

|-----|--------------|----|----------------|-----|-------------|-------------|-------------|-------------|-----|-------|-------|

| SX  | S0           | S1 |                |     | Ĭ           | Ŭ           | ľ           | '           | ·   | '     | '     |

| 0   | 0            | 0  |                | *   | C8          | C4          | Т           | C2          | Т   | Т     | М     |

| 0   | 0            | 1  |                | C1  | T           | Т           | 15          | T           | 13  | 7     | Т     |

| 0   | 1            | 0  |                | CO  | ۲           |             | М           | T           | 12  | 6     | Т     |

| 0   | 1            | 1  |                | Τ   | 10          | 4           | Т           | 0           | Т   | Т     | М     |

| 1   | 0            | 0  |                | СХ  | Т           | T           | 14          | Т           | 11  | 5     | Т     |

| 1   | 0            | 1  |                | Т   | 9           | 3           | Т           | М           | Т   | T     | М     |

| 1   | 1            | 0  |                | Т   | 8           | 2           | Т           | 1           | Т   | Т     | м     |

| 1   | 1            | 1  |                | М   | Т           | Т           | М           | Т           | М   | М     | Т     |

<sup>\* -</sup> no errors detected

Number - location of the single bit-in-error

T - two errors detected

M - three or more errors detected

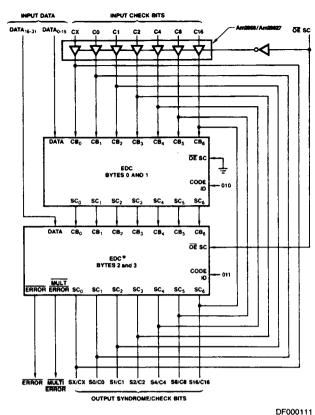

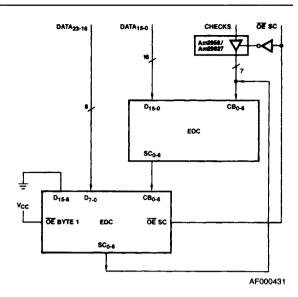

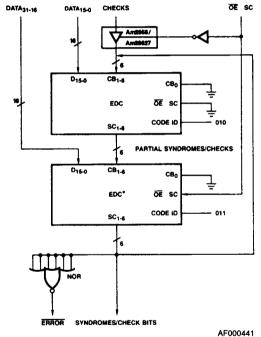

32-BIT DATA WORD CONFIGURATION

The 32-bit format consists of 32 data bits and 7 check bits and is referred to as 32/39 code (see Figure 7).

The 32-bit configuration is shown in Figure 8.

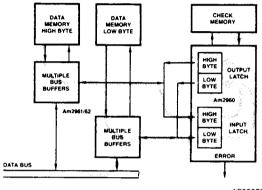

The upper EDC (Slice 0/1) handles the least significant bytes 0 and 1 – the external DATA lines 0 to 15 are connected to the same numbered inputs of the upper device. The lower EDC (Slice 2/3) handles the most significant bytes 2 and 3–the external DATA lines for bits 16 to 31 are connected to inputs DATA<sub>0</sub> through DATA<sub>15</sub> respectively.

The valid syndrome and check bit outputs are those of Slice 2/3 as shown in the diagram. In Correct Mode these must be read into Slice 0/1 via the CB inputs and are selected by the MUX as inputs to the bit-in-error decoder (see block diagram). This requires external buffering and output enabling of the check bit lines, as shown. The OE SC signal can be used to control enabling of check bit inputs – when syndrome outputs are enabled, the external check bit inputs will be disabled.

The valid ERROR and MULT ERROR outputs are those of the Slice 2/3. The ERROR and MULT ERROR outputs of Slice 0/1 are unspecified. All of the latch enables and control signals must be input to both of the devices.

TABLE 19.

16-BIT DIAGNOSTIC LATCH LOADING FORMAT

| Data Bit | Internal Function      |

|----------|------------------------|

| 0        | Diagnostic Check Bit X |

| 1        | Diagnostic Check Bit 0 |

| 2        | Diagnostic Check Bit 1 |

| 3        | Diagnostic Check Bit 2 |

| 4        | Diagnostic Check Bit 4 |

| 5        | Diagnostic Check Bit 8 |

| 6, 7     | Don't Care             |

| 8        | CODE ID 0              |

| 9        | CODE 1D 1              |

| 10       | CODE ID 2              |

| 11       | DIAG MODE 0            |

| 12       | DIAG MODE 1            |

| 13       | CORRECT                |

| 14       | PASS THRU              |

| 15       | Don't Care             |

#### Generate Mode

In this mode, check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated are placed on the outputs SC<sub>0-6</sub> of Slice 2/3.

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table 23. Check bits are generated as either an XOR or XNOR of 16 of the 32 data bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

#### **Detect Mode**

In this mode, the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors, and some triple-bit errors. If one or more errors are defected, ERROR goes LOW. If two or more errors are detected, MULT ERROR goes LOW. Both error indicators are HIGH if there are no errors. The valid ERROR and MULT ERROR signals are those of Slice 2/3 – those of Slice 0/1 are undefined.

Also available on Slice 2/3 outputs  $SC_{0-6}$  are the syndrome bits generated by the error detection step. The syndrome bits may be decoded to determine if a bit error was detected and,

Also available on Slice 2/3 outputs  $SC_{0-6}$  are the syndrome bits generated by the error detection step. The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table 20 gives the chart for decoding the syndrome bits generated for the 32-bit configuration (as an example, if the syndrome bits SX/SO/S1/S2/S4/S8/S16 were 0010011, this would be decoded to indicate that there is a single-bit error at data bit 25). If no error is detected, the syndrome bits will be all zeroes

In Detect Mode, the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without corrections.

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it onto the inputs of the Data Output Latch. If multiple errors are detected, the output of the correction network is unspecified. If the single-bit error is a check bit, there is no automatic correction; if desired, this would be done by placing the device in Generate Mode to produce a correct check bit sequence for the data in the Data Input Latch.

For data correction, both Slices 0/1 and 2/3 require access to the syndrome bits on Slice 2/3's outputs SC<sub>0-6</sub>. Slice 2/3 has access to these syndrome bits through internal data paths, but for Slice 0/1 they must be read through the inputs CB<sub>0-6</sub>. The device connections for this are shown in Figure 8. When in Correct Mode, the SC outputs must be enabled so that they are available for reading in through the CB inputs.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output latch, and the contents of the Check Bit Input Latch are placed on outputs SC<sub>0-6</sub> of Slice 2/3. ERROR and MULT ERROR are forced HIGH in this mode.

#### Internal Control Mode

This mode is selected by CODE ID<sub>2-0</sub> input 001 (ID<sub>2</sub>, ID<sub>1</sub>, ID<sub>0</sub>). When in Internal Control Mode, the EDC takes the CODE ID<sub>2-0</sub> DIAG MODE<sub>0-1</sub>, CORRECT and PASS THRU control signals from the Internal Diagnostic Latch rather than from the external input lines.

Table 22 gives the format for loading the Diagnostic Latch.

#### TABLE 20. SYNDROME DECODE TO BIT-IN-ERROR

| S  | ynd<br>Bi |            | e  | S16<br>S8<br>S4 | 0<br>0<br>0 | 1<br>0<br>0 | 0<br>1<br>0 | 1<br>1<br>0 | 0<br>0<br>1 | 1<br>0<br>1 | 0<br>1<br>1 | 1 1 1 |

|----|-----------|------------|----|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------|

| sx | S0        | <b>S</b> 1 | S2 |                 |             |             |             |             |             |             |             |       |

| 0  | 0         | 0          | 0  |                 | *           | C16         | C8          | Т           | C4          | Т           | T           | 30    |

| 0  | 0         | 0          | 1  |                 | Ç2          | Т           | Т           | 27          | Т           | 5           | м           | Т     |

| 0  | 0         | 1          | 0  |                 | Cī          | Т           | T           | 25          | T           | 3           | 15          | Т     |

| 0  | 0         | 1          | 1  |                 | ۲           | М           | 13          | Т           | 23          | Т           | Т           | М     |

| 0  | 1         | 0          | 0  |                 | CO          | _           | T           | 24          | Т           | 2           | М           | Т     |

| 0  | 1         | 0          | 1  |                 | ۲           | 1           | 12          | T           | 22          | Т           | Т           | М     |

| 0  | 1         | 1          | 0  |                 | Т           | М           | 10          | Т           | 20          | Т           | Т           | М     |

| 0  | 1         | 1          | 1  |                 | 16          | -           | Ť           | М           | T           | М           | М           | Т     |

| 1  | 0         | 0          | 0  |                 | СХ          | Т           | Т           | М           | Т           | М           | 14          | T     |

| 1  | 0         | 0          | 1  |                 | Т           | М           | 11          | 1           | 21          | Т           | Т           | М     |

| 1  | 0         | 1          | 0  |                 | Т           | М           | 0           | Т           | 19          | Т           | Т           | 31    |

| 1  | 0         | 1          | 1  |                 | М           | Т           | _           | 29          | T           | 7           | М           | Т     |

| 1  | 1         | 0          | 0  |                 | T           | М           | 8           | Т           | 18          | Т           | Т           | М     |

| 1  | 1         | 0          | 1  |                 | 17          | Т           | Т           | 28          | Т           | 6           | М           | Т     |

| 1  | 1         | 1          | 0  |                 | М           | Т           | Т           | 26          | Т           | 4           | М           | T     |

| 1  | 1         | 1          | 1  |                 | Т           | 0           | М           | Τ           | М           | T           | T           | М     |

<sup>\* -</sup> no errors detected

Number - number of the single bit-in-error

T - two errors detected

M - three or more errors detected

#### **Diagnostic Latch**

The Diagnostic Latch serves both for diagnostic uses and internal control uses. It is loaded from the DATA lines under the control of LE DIAG. Table 22 shows the loading definitions for the DATA lines.

## Diagnostic Generate/Diagnostic Detect/ Diagnostic Correct

These are special diagnostic modes selected by DIAG MODE<sub>0-1</sub> where either normal check bit inputs or outputs are substituted for by check bits from the Diagnostic Latch (see Table 2 for details). Figures 3 and 4 illustrate the flow of data during the two diagnostic modes.

- 32 data bits

Uses Modified Hamming Code 32/39

- 7 check bits

- 39 bits in total

Figure 7. 32-Bit Data Format

DF000460

\*Check Bit Latch is Forced Transparent in this Code ID Combination for this Slice.

Figure 8. 32-Bit Configuration

TABLE 21.

KEY AC CALCULATIONS FOR THE 32-BIT CONFIGURATION

| Propa   | 32-Bit<br>gation Delay    | Component Delay from Am2960                                        |

|---------|---------------------------|--------------------------------------------------------------------|

| From    | То                        | AC Specifications                                                  |

| DATA    | Check Bits<br>Out         | (Data to SC) + (CB to SC, CODE ID 011)                             |

| DATA in | Corrected<br>DATA Out     | (DATA to SC) + (CB to SC, CODE ID 011) + (CB to DATA, CODE ID 010) |

| DATA    | Syndromes<br>Out          | (DATA to SC) + (CB to SC, CODE ID 011)                             |

| DATA    | ERROR<br>for 32 Bits      | (DATA to SC) + (CB to ERROR,<br>CODE ID 011)                       |

| DATA    | MULT ERROR<br>for 32 Bits | (DATA to SC) + (CB to MULT ERROR,<br>CODE ID 011)                  |

TABLE 22. 32-BIT DIAGNOSTIC LATCH LOADING FORMAT

| Data Bit | Internal Function       |

|----------|-------------------------|

| 0        | Diagnostic Check Bit X  |

| 1        | Diagnostic Check Bit 0  |

| 2        | Diagnostic Check Bit 1  |

| 3        | Diagnostic Check Bit 2  |

| 4        | Diagnostic Check Bit 4  |

| 5        | Diagnostic Check Bit 8  |

| 6        | Diagnostic Check Bit 16 |

| 7        | Don't Care              |

| 8        | Slice 0/1 - CODE ID 0   |

| 9        | Slice 0/1 - CODE ID 1   |

| 10       | Slice 0/1 - CODE ID 2   |

| 11       | Slice 0/1 - DIAG MODE 0 |

| 12       | Slice 0/1 - DIAG MODE 1 |

| 13       | Slice 0/1 ~ CORRECT     |

| 14       | Slice 0/1 - PASS THRU   |

| 15       | Don't Care              |

| 16-23    | Don't Care              |

| 24       | Slice 2/3 - CODE ID 0   |

| 25       | Slice 2/3 - CODE ID 1   |

| 26       | Slice 2/3 - CODE ID 2   |

| 27       | Slice 2/3 - DIAG MODE 0 |

| 28       | Slice 2/3 - DIAG MODE 1 |

| 29       | Slice 2/3 - CORRECT     |

| 30       | Slice 2/3 - PASS THRU   |

| 31       | Don't Care              |

TABLE 23.

32-BIT MODIFIED HAMMING CODE - CHECK BIT ENCODE CHART

| Generated<br>Check |            | Participating Data Bits |   |   |   |   |   |   |   |   |   |    |    |               |    |    |    |

|--------------------|------------|-------------------------|---|---|---|---|---|---|---|---|---|----|----|---------------|----|----|----|

| Bits               | Parity     | 0                       | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12            | 13 | 14 | 15 |

| CX                 | Even (XOR) | ×                       |   |   |   | X |   | Х | х | × | х |    | х  |               |    | Х  |    |

| C0                 | Even (XOR) | х                       | Х | Х |   | × |   | Х |   | × |   | х  |    | X             |    |    | _  |

| C1                 | Odd (XNOR) | х                       |   |   | Х | × |   |   | Х |   | х | х  |    |               | х  |    | ×  |

| C2                 | Odd (XNOR) | х                       | Х |   |   | Г | Х | Х | х |   |   |    | ×  | х             | х  |    | _  |

| C4                 | Even (XOR) |                         |   | Х | Х | х | х | х | х |   | _ |    |    |               |    | х  | ×  |

| C8                 | Even (XOR) |                         |   |   |   |   |   |   |   | х | Х | X  | х  | х             | х  | х  | _x |

| C16                | Even (XOR) | х                       | х | Х | × | х | Х | Х | X |   | - |    |    | $\overline{}$ |    |    | _  |

| Generated<br>Check |            | Participating Data Bits |    |   |      |    |    |          |    |    |    |    |    |    |    |    |    |    |

|--------------------|------------|-------------------------|----|---|------|----|----|----------|----|----|----|----|----|----|----|----|----|----|

| Bits               | Parity     | 16                      | 17 | 1 | 8 19 | 20 | 2  | 1        | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| СХ                 | Even (XOR) | Γ                       | Х  | > | X    | 1  | `` | (        |    |    |    |    | Х  |    | Х  | Х  | •  | х  |

| C0                 | Even (XOR) | x                       | Х  | > |      | ×  |    |          | Х  |    | х  |    | Х  |    | x  |    |    |    |

| C1                 | Odd (XNOR) | х                       |    |   | Х    | ×  |    |          |    | Х  |    | Х  | Х  |    |    | Х  |    | ×  |

| C2                 | Odd (XNOR) | х                       | Х  |   |      |    | `  | <u> </u> | х  | Х  |    |    |    | х  | x  | Х  |    |    |

| C4                 | Even (XOR) |                         |    | × | X    | X  | )  | (        | Х  | Х  |    |    | -  |    | Т  |    | Х  | Х  |

| C8                 | Even (XOR) | Γ                       |    |   |      | 1  |    |          |    |    | х  | Х  | Х  | Х  | x  | х  | х  | х  |

| C16                | Even (XOR) |                         |    |   |      | 1  |    |          |    |    | X  | х  | Х  | Х  | x  | Х  | Х  | ×  |

The check bit is generated as either an XOR or XNOR of the sixteen data bits noted by an "X" in the table.

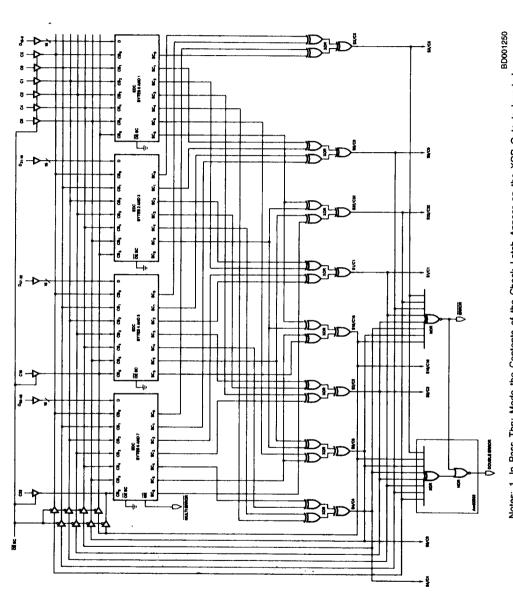

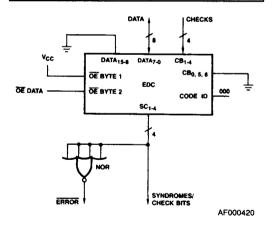

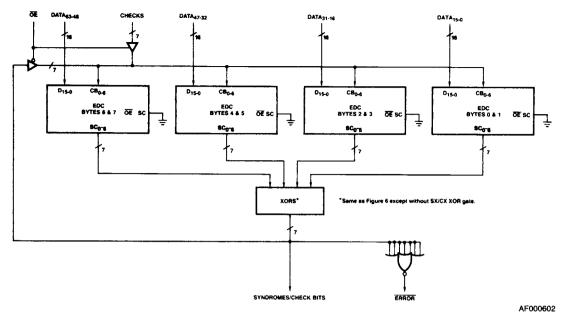

#### 64-BIT DATA WORD CONFIGURATION

The 64-bit format consists of 64 data bits, 8 check bits and is referred to as 64/72 code (see Figure 9.).

The configuration to process 64-bit format is shown in Figure 6. In this configuration, a portion of the syndrome generation and error detection is implemented externally of the EDCs in MSI. For error correction, the syndrome bits generated must be read back into all four EDCs through the CB inputs. This necessitates the check bit buffering shown in the connection diagram of Figure 10. The  $\overline{OE}$  SC signal can control the check bit enabling; when syndrome bit outputs are enabled, the external check bit lines will be disabled so that the syndrome bits may be read onto the CB inputs.

The error detection signals for the 64-bit configuration differ from the 16- and 32-bit configurations. The ERROR signal functions the same: it is LOW if one or more errors are detected, and HIGH if no errors are detected. The DOUBLE ERROR signal is HIGH if and only if a double-bit error is detected; it is LOW otherwise. All of the MULT ERROR outputs of the four devices are valid. MULT ERROR is LOW of all three ERROR cases and some DOUBLE ERROR combinations. (See TOME definition in Functional Equations section.) It is HIGH if either zero or one errors are detected.

This is a different meaning for MULT ERROR than in other configurations.

#### Generate Mode

In this mode, check bits will be generated that correspond to the contents of the Data Input Latch. The check bits generated appear at the outputs of the XOR gates as indicated in Figure 10.

Check bits are generated according to a modified Hamming code. Details of the code for check bit generation are contained in Table 25. Check bits are generated as either an XOR or XNOR of 32 of the 64 bits as indicated in the table. The XOR function results in an even parity check bit, the XNOR in an odd parity check bit.

#### **Detect Mode**

In this mode, the device examines the contents of the Data Input Latch against the Check Bit Input Latch, and will detect all single-bit errors, all double-bit errors and some triple-bit errors. If one or more errors are detected, ERROR goes LOW. If exactly two errors are detected, DOUBLE ERROR goes HIGH. If three or more errors are detected, MULT ERROR goes LOW – the MULT ERROR output of any of the four EDCs may be used.

Available as XOR gate outputs are the generated syndrome bits (see Figure 10). The syndrome bits may be decoded to determine if a bit error was detected and, for single-bit errors, which of the data or check bits is in error. Table 26 gives the chart for encoding the syndrome bits generated for the 64-bit configuration (as an example, if the syndrome bits SX/S1/S2/

- 64 data bits

S4/S8/S16/S32 were 00100101, this would be decoded to indicate that there is a single-bit error at data bit 41). If no error is detected, the syndrome bits will all be zeroes.

In Detect Mode, the contents of the Data Input Latch are driven directly to the inputs of the Data Output Latch without corrections.

#### **Correct Mode**

In this mode, the EDC functions the same as in Detect Mode except that the correction network is allowed to correct (complement) any single-bit error of the Data Input Latch before putting it onto the inputs of the Data Output Latch. If multiple errors are detected, the output of the correction network is unspecified. If the single-bit error is a check bit, there is no automatic correction. Check bit correction can be done by placing the device in generate mode to produce a correct check bit sequence for the data in the Data Input Latch.

To perform the correction step, all four slices require access to the syndrome bits which are generated externally of the devices. This access is provided by reading the syndrome bits in through the CB inputs, where they are selected as inputs to the bit-in-error decoder by the multiplexer (see Block Diagram). The device connections for this are shown in Figure 10. When in Correct Mode, the SC outputs must be enabled so that the syndrome bits are available at the CB inputs.

#### Pass Thru Mode

In this mode, the unmodified contents of the Data Input Latch are placed on the inputs of the Data Output Latch, and the contents of Check Bit Input Latch are passed through the external XOR network and appear inverted at the XOR gate outputs labeled CX to C32 (see Figure 10).

#### Diagnostic Latch

The Diagnostic Latch serves both for diagnostic uses and internal control uses. It is loaded from the DATA lines under the control of LE DIAG. Table 27 shows the loading definitions for the DATA lines.

## Diagnostic Generate/Diagnostic Detect/ Diagnostic Correct

These are special diagnostic modes selected by DIAG MODE<sub>0-1</sub> where either normal check bit inputs or outputs are substituted for by check bits from the Diagnostic Latch. See Table 2 for details.

#### Internal Control Mode

This mode is selected by CODE  $ID_{2-0}$ , input 001 ( $ID_2$ ,  $ID_1$ ,  $ID_0$ ).

When in Internal Control Mode, the EDC takes the CODE ID<sub>2-0</sub>, DIAG MODE<sub>0-1</sub>, CORRECT and PASS THRU signals from the internal Diagnostic Latch rather than from the external control lines. Table 27 gives format for loading the Diagnostic Latch.

Uses Modified Hamming Code 64/72

– 8 check bits

- 72 bits in total

Figure 9. 64-Bit Data Format

Notes: 1. In Pass Thru Mode the Contents of the Check Latch Appear on the XOR Outputs Inverted.

2. In Diagnostic Generate Mode the Contents of the Diagnostic Latch Appear on the XOR Outputs Inverted.

Figure 10. 64-Bit Data Configuration

TABLE 24.

KEY AC CALCULATIONS FOR THE 64-BIT CONFIGURATION

|         | 64-Bit<br>Propagation Delay | Component Delays from Am2960                                                  |

|---------|-----------------------------|-------------------------------------------------------------------------------|

| From    | То                          | AC Specifications, plus MSI                                                   |

| DATA    | Check Bits Out              | (DATA to SC) + (XOR Delay)                                                    |