## **POWER MANAGEMENT**

# 18V, 3A, 350kHz Step-Down Switching Regulator

#### **Features**

- Input Voltage Range: 3V to 18V

- 3A Output Current

- 350kHz Fixed Switching Frequency

- Precision 1V Feedback Voltage

- Peak Current-Mode Control

- Cycle-by-Cycle Current Limiting

- Hiccup Overload Protection with Frequency Foldback

- Soft-Start and Enable

- Thermal Shutdown

- Thermally Enhanced 8-pin SOIC Package

- Fully RoHS and WEEE Compliant

### Description

The SC4525F is a 350kHz constant frequency peak current-mode step-down switching regulator capable of producing 3A output current from an input ranging from 3V to 18V. The SC4525F is suitable for next generation XDSL modems, high-definition TVs and various point of load applications.

Peak current-mode PWM control employed in the SC4525F achieves fast transient response with simple loop compensation. Cycle-by-cycle current limiting and hiccup overload protection reduces power dissipation during output overload. Soft-start function reduces input start-up current and prevents the output from overshooting during power-up.

The SC4525F is available in SOIC-8 EDP package.

## Applications

- XDSL and Cable Modems

- Set Top Boxes

- Point of Load Applications

- CPE Equipment

- DSP Power Supplies

- LCD and Plasma TVs

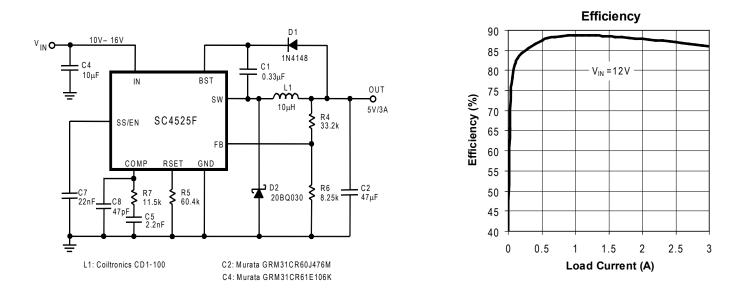

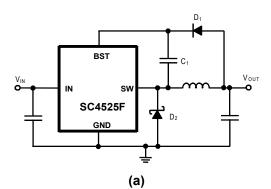

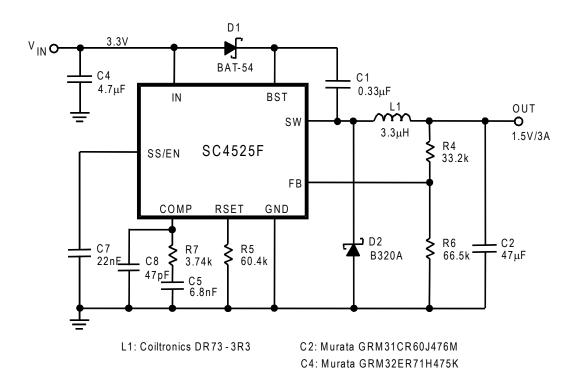

# **Typical Application Circuit**

Figure 1 — 350kHz 10V - 16V to 5V/3A Step-down Converter

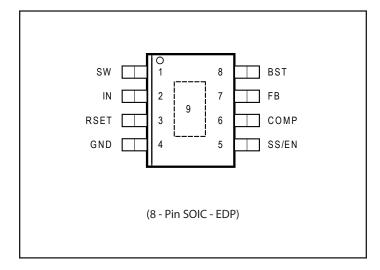

# **Pin Configuration**

# **Marking Information**

# **Ordering Information**

| Device                         | Package          |

|--------------------------------|------------------|

| SC4525FSETRT <sup>(1)(2)</sup> | SOIC-8 EDP       |

| SC4525FEVB                     | Evaluation Board |

Notes:

(1) Available in tape and reel only. A reel contains 2,500 devices.(2) Available in lead-free package only. Device is fully WEEE and RoHS compliant and halogen-free.

# **Absolute Maximum Ratings**

| $\rm V_{_{\rm IN}}$ Supply Voltage $\hfill \ldots \hfill $ -0.3 to 24 | V               |

|-----------------------------------------------------------------------|-----------------|

| BST Voltage 40                                                        | V               |

| BST Voltage above SW 24                                               | 4V              |

| SS Voltage0.3 to 3                                                    | 3V              |

| FB Voltage0.3 to 2                                                    | 7V              |

| SW Voltage                                                            | V <sub>IN</sub> |

| SW Transient Spikes (10ns Duration)2.5V to $V_{IN}$ +1.5              | δV              |

| Peak IR Reflow Temperature                                            | )°C             |

| ESD Protection Level <sup>(2)</sup>                                   | 0V              |

|                                                                       |                 |

# **Thermal Information**

| Junction to Ambient <sup>(1)</sup>  | 36°C/W    |

|-------------------------------------|-----------|

| Junction to Case (1)                | 5.5°C/W   |

| Maximum Junction Temperature        | 150°C     |

| Storage Temperature                 | :o +150°C |

| Lead Temperature (Soldering) 10 sec | 300°C     |

# **Recommended Operating Conditions**

| Input Voltage Range            | 3V to 18V     |

|--------------------------------|---------------|

| Maximum Output Current         | 3A            |

| Operating Ambient Temperature  | -40 to +105°C |

| Operating Junction Temperature | -40 to +125°C |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

NOTES-

(1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

(2) Tested according to JEDEC standard JESD22-A114-B.

# Electrical Characteristics \_

Unless otherwise noted,  $V_{_{IN}} = 12V$ ,  $V_{_{BST}} = 15V$ ,  $V_{_{SS}} = 2.2V$ ,  $-40^{\circ}C < T_{_A} = T_{_J} < 125^{\circ}C$ ,  $R_{_{SET}} = 60.4k\Omega$ .

| Parameter                                     | Conditions                       | Min   | Тур   | Мах   | Units |

|-----------------------------------------------|----------------------------------|-------|-------|-------|-------|

| Input Supply                                  |                                  |       | 1     |       |       |

| Input Voltage Range                           |                                  | 3     |       | 18    | V     |

| V <sub>IN</sub> Start Voltage                 | V <sub>IN</sub> Rising           | 2.70  | 2.82  | 2.95  | V     |

| V <sub>IN</sub> Start Hysteresis              |                                  |       | 225   |       | mV    |

| V <sub>IN</sub> Quiescent Current             | $V_{COMP} = 0$ (Not Switching)   |       | 2     | 2.6   | mA    |

| V <sub>IN</sub> Quiescent Current in Shutdown | $V_{ss/en} = 0, V_{in} = 12V$    |       | 40    | 52    | μΑ    |

| Error Amplifier                               |                                  |       |       |       |       |

| Feedback Voltage                              |                                  | 0.980 | 1.000 | 1.020 | V     |

| Feedback Voltage Line Regulation              | $V_{IN} = 3V \text{ to } 18V$    |       | 0.005 |       | %/V   |

| FB Pin Input Bias Current                     | $V_{FB} = 1V, V_{COMP} = 0.8V$   |       | -170  | -340  | nA    |

| Error Amplifier Transconductance              |                                  |       | 300   |       | μΩ-1  |

| Error Amplifier Open-loop Gain                |                                  |       | 60    |       | dB    |

| COMP Pin to Switch Current Gain               |                                  |       | 15.2  |       | A/V   |

| COMP Maximum Voltage                          | V <sub>FB</sub> = 0.9V           |       | 2.35  |       | V     |

| COMP Source Current                           | $V_{FB} = 0.8V, V_{COMP} = 0.8V$ |       | 17    |       |       |

| COMP Sink Current                             | $V_{FB} = 1.2V, V_{COMP} = 0.8V$ |       | 25    |       | μΑ    |

| Internal Power Switch                         |                                  |       |       |       |       |

| Switch Current Limit                          | (Note 1) 3.9 5.1                 |       | 6.6   | A     |       |

| Switch Saturation Voltage                     | I <sub>sw</sub> = -3.9A          |       | 380   | 600   | mV    |

# SEMTECH

# **Electrical Characteristics (Cont.)**

Unless otherwise noted,  $V_{_{\rm IN}} = 12V$ ,  $V_{_{\rm BST}} = 15V$ ,  $V_{_{\rm SS}} = 2.2V$ ,  $-40^{\circ}C < T_{_{\rm A}} = T_{_{\rm J}} < 125^{\circ}C$ ,  $R_{_{\rm SET}} = 60.4k\Omega$ .

| Parameter                          | Conditions                                          | Min  | Тур  | Max | Units |

|------------------------------------|-----------------------------------------------------|------|------|-----|-------|

| Minimum Switch On-time             | $V_{IN} = 10 \text{ V}, \text{ R}_{SW} = 10 \Omega$ | 70   | 120  | 230 | ns    |

| Minimum Switch Off-time            | $V_{IN} = 6 V, R_{SW} = 6 \Omega$                   | 30   | 75   | 130 | ns    |

| Switch Leakage Current             |                                                     |      |      | 10  | μΑ    |

| Minimum Bootstrap Voltage          | I <sub>sw</sub> = -3.9A                             |      | 1.8  | 2.3 | V     |

| BST Pin Current                    | I <sub>sw</sub> = -3.9A                             |      | 100  | 150 | mA    |

| Oscillator                         |                                                     | ·    |      |     |       |

| Switching Frequency                | $R_{set} = 60.4k\Omega$                             | 275  | 350  | 425 | kHz   |

| Foldback Frequency                 | $R_{SET} = 60.4 k\Omega, V_{FB} = 0$                | 35   | 65   | 100 | kHz   |

| Soft Start and Overload Protection |                                                     | ·    |      |     |       |

| SS/EN Shutdown Threshold           |                                                     | 0.2  | 0.3  | 0.4 | V     |

| SS/EN Switching Threshold          | $V_{FB} = 0 V$                                      | 0.95 | 1.2  | 1.4 | V     |

| Soft start Charging Concept        | $V_{SS/EN} = 0 V$                                   |      | 1.9  |     |       |

| Soft-start Charging Current        | V <sub>SS/EN</sub> = 1.5 V                          | 1.6  | 2.4  | 3.2 | μA    |

| Soft-start Discharging Current     |                                                     |      | 1.5  |     | μΑ    |

| Hiccup Arming SS/EN Voltage        | V <sub>ss/EN</sub> Rising                           |      | 2.15 |     | V     |

| Hiccup SS/EN Overload Threshold    | V <sub>ss/en</sub> Falling                          |      | 1.9  |     | V     |

| Hiccup Retry SS/EN Voltage         | V <sub>ss/en</sub> Falling                          | 0.6  | 1.0  | 1.2 | V     |

| Over Temperature Protection        |                                                     |      |      |     |       |

| Thermal Shutdown Temperature       |                                                     |      | 165  |     | °C    |

| Thermal Shutdown Hysteresis        |                                                     |      | 10   |     | °C    |

Note 1: Switch current limit does not vary with duty cycle.

# **Pin Descriptions**

| SO-8 | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | SW          | Emitter of the internal NPN power transistor. Connect this pin to the inductor, the freewheeling diode and the bootstrap capacitor.                                                                                                                                                                                                                                                   |

| 2    | IN          | Power supply to the regulator. It is also the collector of the internal NPN power transistor. It must be closely by-<br>passed to the ground plane with a capacitor.                                                                                                                                                                                                                  |

| 3    | RSET        | Connect a 60.4k $\Omega$ resistor from this pin to ground.                                                                                                                                                                                                                                                                                                                            |

| 4    | GND         | Ground pin                                                                                                                                                                                                                                                                                                                                                                            |

| 5    | SS/EN       | Soft-start and regulator enable pin. A capacitor from this pin to ground provides soft-start and overload hiccup functions. Hiccup can be disabled by overcoming the internal soft-start discharging current with an external pull-up resistor connected between the SS/EN and the IN pins. Pulling the SS/EN pin below 0.2V completely shuts off the regulator to low current state. |

| 6    | COMP        | The output of the internal error amplifier. The voltage at this pin controls the peak switch current. A RC compensa-<br>tion network at this pin stabilizes the regulator.                                                                                                                                                                                                            |

| 7    | FB          | The inverting input of the error amplifier. If $V_{_{FB}}$ falls below 0.8V, then the switching frequency will be reduced to improve short-circuit robustness (see Applications Information for details).                                                                                                                                                                             |

| 8    | BST         | Supply pin to the power transistor driver. Tie to an external diode-capacitor bootstrap circuit to generate drive voltage higher than $V_{_{IN}}$ in order to fully enhance the internal NPN power transistor.                                                                                                                                                                        |

| 9    | Exposed Pad | The exposed pad serves as a thermal contact to the circuit board. While the exposed pad is electrically isolated, it is suggested to be soldered to the ground plane of the PC board.                                                                                                                                                                                                 |

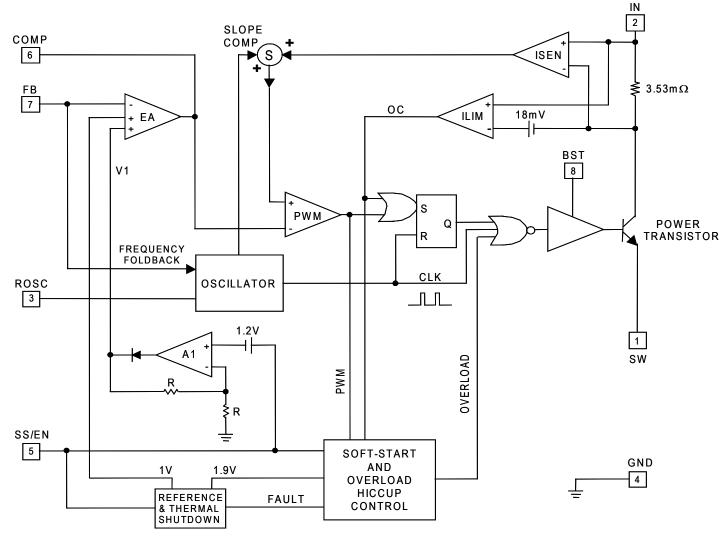

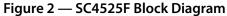

# **Block Diagram**

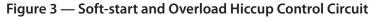

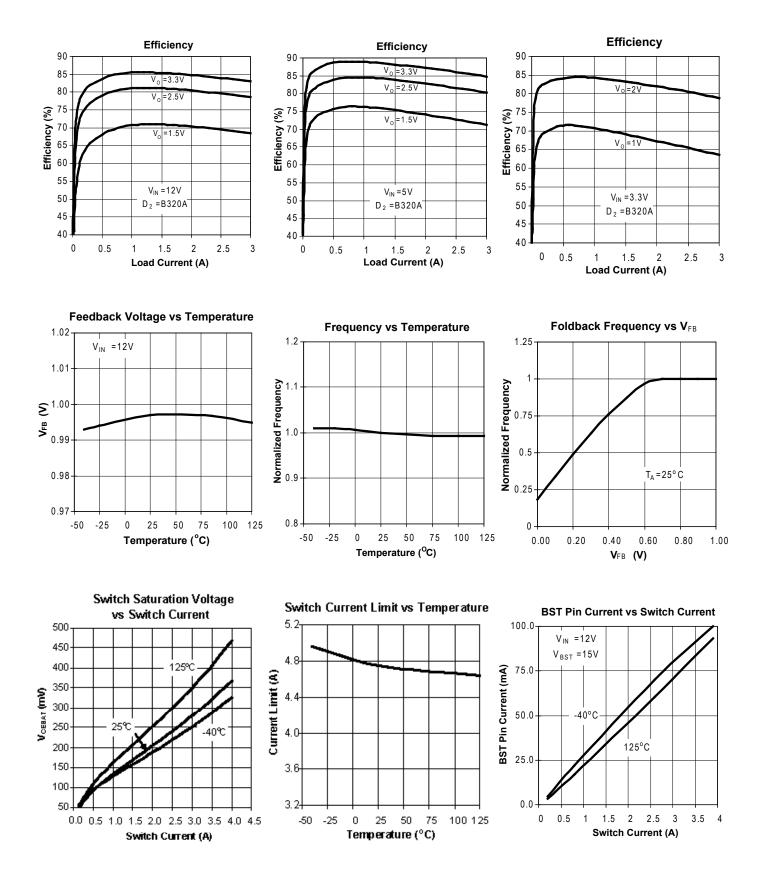

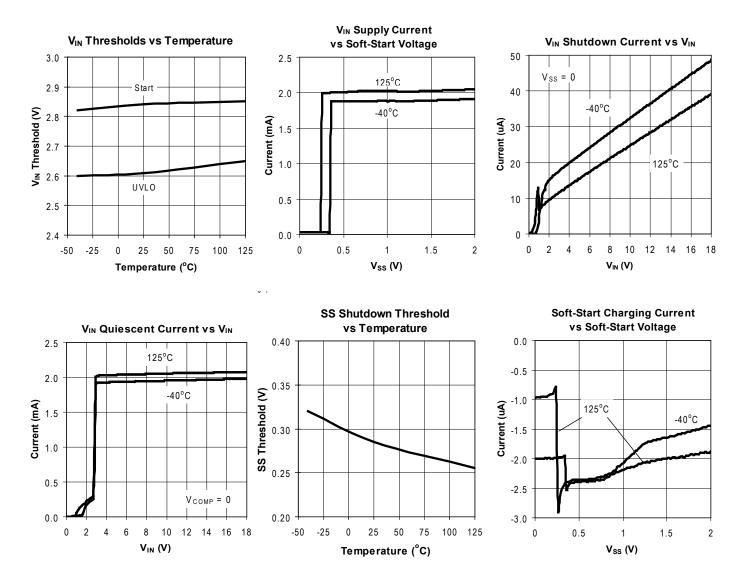

# **Typical Characteristics**

# **Typical Characteristics (Cont.)**

## **Applications Information**

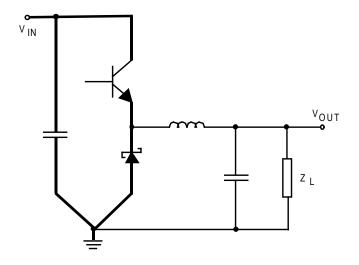

#### Operation

The SC4525F is a 350kHz fixed frequency, peak currentmode, step-down switching regulator with an integrated 3.9A power NPN transistor. With the peak current-mode control, the double reactive poles of the output LC filter are reduced to a single real pole by the inner current loop. This simplifies loop compensation and achieves fast transient response with a simple Type-2 compensation network.

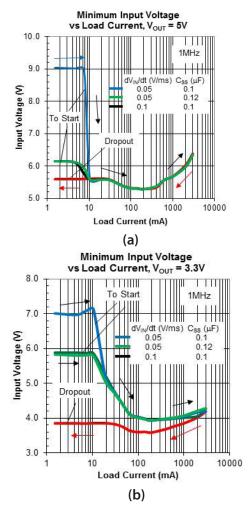

As shown in Figure 2, the switch collector current is sensed with an integrated  $3.53m\Omega$  sense resistor. The sensed current is summed with a slope-compensating ramp before it is compared with the transconductance error amplifier (EA) output. The PWM comparator trip point determines the switch turn-on pulse width. The current-limit comparator ILIM turns off the power switch when the sensed signal exceeds the 18mV current-limit threshold.

Driving the base of the power transistor above the input power supply rail minimizes the power transistor saturation voltage and maximizes efficiency. An external bootstrap circuit (formed by the capacitor  $C_1$  and the diode  $D_1$  in Figure 1) generates such a voltage at the BST pin for driving the power transistor.

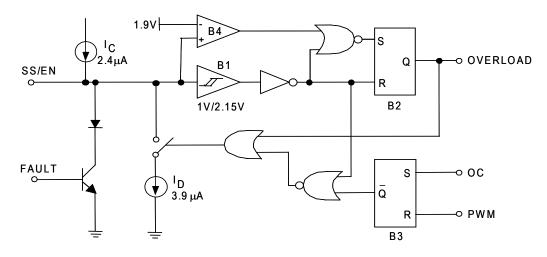

#### **Shutdown and Soft-Start**

The SS/EN pin is a multiple-function pin. An external capacitor (4.7nF to 22nF) connected from the SS pin to ground sets the soft-start and overload shutoff times of the regulator (Figure 3). The effect of  $V_{SS/EN}$  on the SC4525F is summarized in Table 1.

| SS/EN         | Mode                        | Supply Current |

|---------------|-----------------------------|----------------|

| <0.2V         | Shutdown                    | 18uA @ 5Vin    |

| 0.4V to 1.2V  | Not switching               | 2mA            |

| 1.2V to 2.15V | Switching & hiccup disabled | Load dependent |

| >2.15V        | Switching & hiccup armed    |                |

Table 1: SS/EN operation modes

Pulling the SS/EN pin below 0.2V shuts off the regulator and reduces the input supply current to  $18\mu A$  ( $V_{IN} = 5V$ ). When the SS/EN pin is released, the soft-start capacitor is charged with an internal 1.9 $\mu A$  current source (not shown in Figure 3). As the SS/EN voltage exceeds 0.4V, the internal bias circuit of the SC4525F turns on and the SC4525F draws 2mA from V<sub>IN</sub>. The 1.9µA charging current turns off and the 2.4µA current source I<sub>c</sub> in Figure 3 slowly charges the soft-start capacitor.

The error amplifier EA in Figure 2 has two non-inverting inputs. The non-inverting input with the lower voltage predominates. One of the non-inverting inputs is biased to a precision 1V reference and the other non-inverting input is tied to the output of the amplifier A, Amplifier A, produces an output  $V_1 = 2(V_{SS/EN} - 1.2V)$ .  $V_1$  is zero and COMP is forced low when  $V_{SS/EN}$  is below 1.2V. During start up, the effective non-inverting input of EA stays at zero until the soft-start capacitor is charged above 1.2V. Once V<sub>ss</sub> <sub>EN</sub> exceeds 1.2V, COMP is released. The regulator starts to switch when  $V_{COMP}$  rises above 0.4V. If the soft-start interval is made sufficiently long, then the FB voltage (hence the output voltage) will track V<sub>1</sub> during start up. V<sub>SS/EN</sub> must be at least 1.83V for the output to achieve regulation. Proper soft-start prevents output overshoot. Current drawn from the input supply is also well controlled.

#### **Overload / Short-Circuit Protection**

Table 2 lists various fault conditions and their corresponding protection schemes in the SC4525F.

| Condition           | Cause of Fault          | Protective Action         |  |  |  |

|---------------------|-------------------------|---------------------------|--|--|--|

|                     | Over current            | Cycle-by-cycle limit at   |  |  |  |

| IL>ILimit, VFB>0.8V | Over current            | programmed frequency      |  |  |  |

|                     | Ower every              | Cycle-by-cycle limit with |  |  |  |

| IL>ILimit, VFB<0.8V | Over current            | frequency foldback        |  |  |  |

| VSS/EN Falling      | Persistent over current | Shutdown, then retry      |  |  |  |

| SS/EN<1.9V          | or short circuit        | (Hiccup)                  |  |  |  |

| Tj>160C             | Over temperature        | Shutdown                  |  |  |  |

Table 2: Fault conditions and protections

As summarized in Table 1, overload shutdown is disabled during soft-start ( $V_{SS/EN}$  < 2.15V). In Figure 3, the reset input of the overload latch  $B_2$  will remain high if the SS/EN voltage is below 2.15V. Once the soft-start capacitor is charged above 2.15V, the output of the Schmitt trigger  $B_1$  goes high, the reset input of  $B_2$  goes low and hiccup becomes armed. As the load draws more current from the regulator, the current-limit comparator ILIM (Figure 2) will eventually limit the switch current on a cycle-bycycle basis. The over-current signal OC goes high, setting

the latch B<sub>3</sub>. The soft-start capacitor is discharged with  $(I_{p} - I_{c})$  (Figure 3). If the inductor current falls below the current limit and the PWM comparator instead turns off the switch, then latch B, will be reset and I<sub>c</sub> will recharge the soft-start capacitor. If over-current condition persists or OC becomes asserted more often than PWM over a period of time, then the soft-start capacitor will be discharged below 1.9V. At this juncture, comparator  $B_{a}$ sets the overload latch B<sub>2</sub>. The soft-start capacitor will be continuously discharged with  $(I_{D} - I_{C})$ . The COMP pin is immediately pulled to ground. The switching regulator is shut off until the soft-start capacitor is discharged below 1.0V. At this moment, the overload latch is reset. The soft-start capacitor is recharged and the converter again undergoes soft-start. The regulator will go through softstart, overload shutdown and restart until it is no longer overloaded.

If the FB voltage falls below 0.8V because of output overload, then the switching frequency will be reduced. Frequency foldback helps to limit the inductor current when the output is hard shorted to ground.

During normal operation, the soft-start capacitor is charged to 2.4V.

#### Setting the Output Voltage

The regulator output voltage,  $V_{o'}$  is set with an external resistive divider (Figure 1) with its center tap tied to the FB pin. For a given  $R_6$  value,  $R_4$  can be found by

$$R_4 = R_6 \left( \frac{V_0}{1.0V} - 1 \right)$$

#### **Minimum On Time Consideration**

The operating duty cycle of a non-synchronous stepdown switching regulator in continuous-conduction mode (CCM) is given by

$$D = \frac{V_{O} + V_{D}}{V_{IN} + V_{D} - V_{CESAT}}$$

where  $V_{_{\rm IN}}$  is the input voltage,  $V_{_{\rm CESAT}}$  is the switch saturation voltage, and  $V_{_{\rm D}}$  is voltage drop across the rectifying diode.

In peak current-mode control, the PWM modulating ramp is the sensed current ramp of the power switch. This current ramp is absent unless the switch is turned on. The intersection of this ramp with the output of the voltage feedback error amplifier determines the switch pulse width. The propagation delay time required to immediately turn off the switch after it is turned on is the minimum controllable switch on time ( $T_{ON(MIN)}$ ).

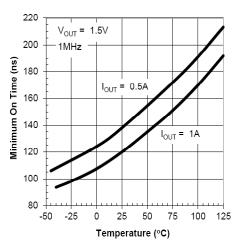

Closed-loop measurement shows that the SC4525F minimum on time is about 120ns at room temperature for 1A load current (Figure 4). If the required switch on time is shorter than the minimum on time, the regulator will either skip cycles or it will jitter.

Figure 4. Variation of Minimum On Time with Ambient Temperature

To allow for transient headroom, the minimum operating switch on time should be at least 20% to 30% higher than the worst-case minimum on time.

#### **Minimum Off Time Limitation**

The PWM latch in Figure 2 is reset every cycle by the clock. The clock also turns off the power transistor to refresh the bootstrap capacitor. This minimum off time limits the attainable duty cycle of the regulator at a given switching frequency. The measured minimum off time is 138ns typically. If the required duty cycle is higher than the attainable maximum, then the output voltage will not be able to reach its set value in continuous-conduction mode.

#### **Inductor Selection**

The inductor ripple current for a non-synchronous stepdown converter in continuous-conduction mode is

$$\Delta I_{L} = \frac{(V_{O} + V_{D}) \cdot (1 - D)}{F_{SW} \cdot L_{1}}$$

where  $\rm F_{sw}$  is the switching frequency (350kHz) and  $\rm L_{1}$  is the inductance.

An inductor ripple current between 20% to 50% of the maximum load current,  $I_o$ , gives a good compromise among efficiency, cost and size. Re-arranging the previous euqation and assuming 35% inductor ripple current, the inductor is given by

$$L_{1} = \frac{(V_{0} + V_{D}) \cdot (1 - D)}{35\% \cdot I_{0} \cdot F_{SW}}$$

If the input voltage varies over a wide range, then choose  $L_1$  based on the nominal input voltage. Always verify converter operation at the input voltage extremes.

The peak current limit of SC4525F power transistor is at least 3.9A. The maximum deliverable load current for the SC4525F is 3.9A minus one half of the inductor ripple current.

#### **Input Decoupling Capacitor**

The input capacitor should be chosen to handle the RMS ripple current of a buck converter. This value is given by

$$I_{\text{RMS}\_\text{CIN}} = I_0 \cdot \sqrt{D \cdot (1 - D)}$$

The input capacitance must also be high enough to keep input ripple voltage within specification. This is important in reducing the conductive EMI from the regulator. The input capacitance can be estimated from

$$C_{IN} > \frac{I_0}{4 \cdot \Delta V_{IN} \cdot F_{SW}}$$

where  $\Delta V_{IN}$  is the allowable input ripple voltage.

Multi-layer ceramic capacitors, which have very low ESR (a few m $\Omega$ ) and can easily handle high RMS ripple current, are the ideal choice for input filtering. A single 4.7 $\mu$ F to 10 $\mu$ F X5R ceramic capacitor is adequate for most applications. For high voltage applications, a small ceramic (1 $\mu$ F or 2.2 $\mu$ F) can be placed in parallel with a low ESR electrolytic

capacitor to satisfy both the ESR and bulk capacitance requirements.

#### **Output Capacitor**

The output ripple voltage  $\Delta V_{\rm o}$  of a buck converter can be expressed as

$$\Delta V_{\rm O} = \Delta I_{\rm L} \cdot \left( {\rm ESR} + \frac{1}{8 \cdot F_{\rm SW} \cdot C_{\rm O}} \right)$$

where C<sub>o</sub> is the output capacitance.

Since the inductor ripple current  $\Delta I_{L}$  increases as D decreases (refer to the first equation in the Inductor Selection section), the output ripple voltage is therefore the highest when  $V_{IN}$  is at its maximum.

A 22 $\mu$ F to 47 $\mu$ F X5R ceramic capacitor is found adequate for output filtering in most applications. Ripple current in the output capacitor is not a concern because the inductor current of a buck converter directly feeds C<sub>o</sub>, resulting in very low ripple current. Avoid using Z5U and Y5V ceramic capacitors for output filtering because these types of capacitors have high temperature and high voltage coefficients.

#### **Freewheeling Diode**

Use of Schottky barrier diodes as freewheeling rectifiers reduces diode reverse recovery input current spikes, easing high-side current sensing in the SC4525F. These diodes should have an average forward current rating at least 3A and a reverse blocking voltage of at least a few volts higher than the input voltage. For switching regulators operating at low duty cycles (i.e. low output voltage to input voltage conversion ratios), it is beneficial to use freewheeling diodes with somewhat higher average current ratings (thus lower forward voltages). This is because the diode conduction interval is much longer than that of the transistor. Converter efficiency will be improved if the voltage drop across the diode is lower.

The 20BQ030 (International Rectifier), B320A, B330A (Diodes Inc.), SS33 (Vishay), CMSH3-20MA and CMSH3-40MA (Central-Semi.) are all suitable.

The freewheeling diode should be placed close to the SW pin of the SC4525F on the PCB to minimize ringing due to trace inductance.

#### **Bootstrapping the Power Transistor**

To maximize efficiency, the turn-on voltage across the internal power NPN transistors should be minimized. If these transistors are to be driven into saturation, then their bases will have to be driven from a power supply higher in voltage than  $V_{IN}$ . The required driver supply voltage (at least 2.3V higher than the SW voltage) is generated with a bootstrap circuit (the diode D<sub>1</sub> and the capacitor C<sub>1</sub> in Figure 6). The bootstrapped output (the common node between D<sub>1</sub> and C<sub>1</sub>) is connected to the BST pin of the SC4525F.

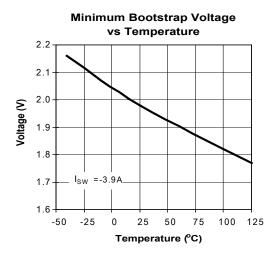

The minimum BST to SW voltage required to fully saturate the power transistor is shown in Figure 5. The minimum required  $V_{C1}$  increases as temperature decreases. The bootstrap circuit reaches equilibrium when the base charge drawn from C<sub>1</sub> during transistor on time is equal to the charge replenished during the off interval.

Figure 5. Typical Minimum Bootstrap Voltage required to Saturate the Transistor ( $I_{sw}$ = -3.9A)

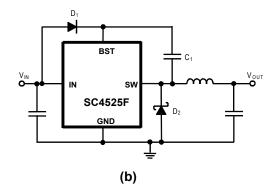

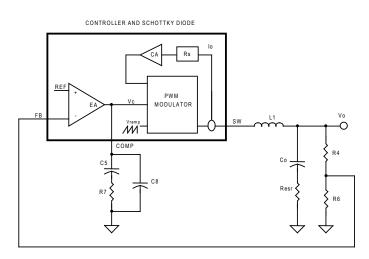

Figure 6 summarizes various ways of bootstrapping the SC4525F. A fast switching PN diode (such as 1N4148 or 1N914) and a small ( $0.33\mu F - 0.47\mu F$ ) ceramic capacitor can be used.

In Figure 6(a) the power switch is bootstrapped from the output. This is the most efficient configuration and it also results in the least voltage stress at the BST pin. The maximum BST pin voltage is about  $V_{IN} + V_{OUT}$ . The minimum  $V_{OUT}$  required for this bootstrap configuration is 2.5V. If the output voltage is between 2.5V and 3V, then use a small

Schottky diode (such as BAT54) for  $\rm D_1$  to maximize the bootstrap voltage.

The SC4525F can also be bootstrapped from the input [Figure 6(b)]. This configuration is not as efficient as Figure 6(a). However this may be the only option if the output voltage is less than 2.5V and there is no other supply with voltage higher than 2.5V. Voltage stress at the BST pin can be somewhat higher than  $2V_{IN}$ .

Figures 6(c) and (d) show how to bootstrap the SC4525F from a second independent power supply  $V_s$ .

The minimum bootstrap capacitance  $\mathrm{C}_{_1}$  can be estimated as:

$$C_1 > \frac{I_{OUT(MAX)} \cdot D}{10 \cdot f \cdot (V_s - 2.4)}$$

where  $V_s$  is the voltage applied to the anode of  $D_1$ .

The inductor current charges the bootstrap capacitor when it pulls the SW node low during the switch off time. If  $D_1$  is connected to the converter input, then  $C_1$  will be charged as soon as  $V_{IN}$  is applied.

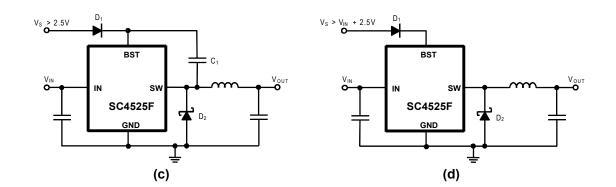

If the bootstrap diode is tied to the converter output [Fig ures 6(a)], then C<sub>1</sub> can only be charged from the regulator output through the inductor. Before the converter starts, there is no output voltage or inductor current. Hence it is necessary for the regulator to deliver some inductor current to the output before  $C_1$  can be charged. If  $V_{IN}$  is not much higher than the programmed  $V_{out}$  and it ramps up very slowly, then the inductor current will not be high enough for the bootstrap circuit to run, especially at light loads. In order to have some inductor current to charge C<sub>1</sub>, the converter output needs to be loaded or  $V_{\mbox{\tiny IN}}$  needs to be increased. Using larger soft-start capacitor C<sub>ss</sub> will also help in starting bootstrap because there will be current in the inductor over a longer period of time. Figures 7(a) and 7(b) show the minimum input voltage required to start bootstrap and to run before dropping out as a function of the load current. The minimum start-up  $V_{\mbox{\tiny IN}}$  decreases with higher  $dV_{IN}/dt$  or larger soft-start capacitor  $C_{ss}$ . The lines labeled "dropout" in these graphs show that once started, the bootstrap circuit is able to sustain itself down to zero load.

Figure 6(a)-(d). Methods of Bootstrapping the SC4525F

Figure 7. The Minimum Input Voltage to Start and to Run Before Dropout. The Regulator is Bootstrapped from its Output [Figure 6(a)].  $D_1$  is 1N4148. (a)  $V_{OUT} = 5V$  (b)  $V_{OUT} = 3.3V$

#### **Minimum Soft-start Capacitance Css**

To ensure normal operation, the minimum soft-start capacitance  $C_{ss}$  can be calculated in terms of the output capacitance  $C_o$  and output load current  $I_o$  according to the following equations.

$\frac{dV_{SS}}{dt} \!=\! \frac{I_{SS}}{C_{SS}}$

$$\frac{\mathrm{d}V_0}{\mathrm{d}t} = \frac{\mathrm{d}V_1}{\mathrm{d}t} = \frac{\mathrm{d}}{\mathrm{d}t} \left[ 2(V_{\mathrm{ss}} - 1.2V) \right]$$

Substituting the first equation into the second equation,

$$\frac{\mathrm{dV}_{0}}{\mathrm{dt}} = \frac{2\mathrm{I}_{\mathrm{SS}}}{\mathrm{C}_{\mathrm{SS}}}$$

where  $V_{ss}$  is the soft-start capacitor voltage and  $I_{ss}$  is the soft-start charging current.  $V_1$  is the voltage defined in Figure 2.

To ensure successful startup, the total current drawn from the output must be less than the maximum output capability of the part,

$$\frac{\mathrm{V}_{0}}{\mathrm{R}} + \mathrm{C}_{0} \times \frac{\mathrm{d}\mathrm{V}_{0}}{\mathrm{d}t} \le 3.5\mathrm{A}$$

Substituting the third equation of this section into the previous equation,

$$\frac{V_0}{R} + 2I_{SS} \times \frac{C_0}{C_{SS}} \le 3.5A$$

Rearranging,

$$C_{SS} \ge \frac{2I_{SS(MAX)} \times C_0}{3.5A - \left(\frac{V_0}{R}\right)}$$

Therefore the minimum  $C_{ss}$  depends on the output capacitance and the load current. Larger  $C_{ss}$  is necessary when starting into a heavy load (small R).

If the regulator is to be started by turning on a bench power supply, then  $C_{ss}$  will be best determined empirically because the rise time of a power supply can range from a few milliseconds to a few hundred milliseconds. With the maximum load applied, the output rise is observed using a 22nF for  $C_{ss}$ . Adjust  $C_{ss}$  until a linear  $V_{out}$  ramp is achieved.

#### **Loop Compensation**

The goal of compensation is to shape the frequency response of the converter so as to achieve high DC accuracy and fast transient response while maintaining loop stability.

The block diagram in Figure 8 shows the control loops of a buck converter with the SC4525F. The inner loop (current loop) consists of a current sensing resistor ( $R_s$ =3.53m $\Omega$ ) and a current amplifier (CA) with gain ( $G_{CA}$ =18.5). The outer loop (voltage loop) consists of an error amplifier (EA), a PWM modulator, and a LC filter.

Since the current loop is internally closed, the remaining task for the loop compensation is to design the voltage compensator ( $C_s$ ,  $R_7$ , and  $C_8$ ).

Figure 8 — Block diagram of control loops

For a converter with switching frequency  $F_{sw'}$  output inductance  $L_1$ , output capacitance  $C_0$  and loading R, the control ( $V_c$ ) to output ( $V_0$ ) transfer function in Figure 8 is given by:

$$\frac{V_{O}}{V_{C}} = \frac{G_{PWM}(1 + sR_{ESR}C_{O})}{(1 + s/\omega_{p})(1 + s/\omega_{n}Q + s^{2}/\omega_{n}^{2})}$$

This transfer function has a finite DC gain

$$G_{PWM} \approx \frac{R}{G_{CA} \times R_{S}}$$

an ESR zero F<sub>z</sub> at

$$\omega_{\rm Z} = \frac{1}{R_{\rm ESR}C_{\rm O}}$$

It has a dominant low-frequency pole  $F_{P}$  at

$$\omega_{\rm p} \approx \frac{1}{RC_{\rm O}}$$

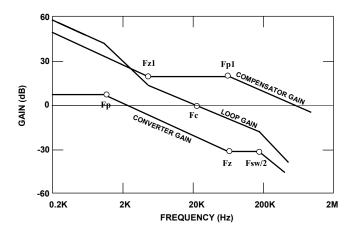

and double poles at half the switching frequency. Including the voltage divider ( $R_4$  and  $R_6$ ), the control to feedback transfer function is found and plotted in Figure

9 as the converter gain.

Since the converter gain has only one dominant pole at low frequency, a simple Type-2 compensation network is sufficient for voltage loop compensation. As shown in Figure 9, the voltage compensator has a low frequency integrator pole, a zero at  $F_{z_1}$ , and a high frequency pole at  $F_{p_1}$ . The integrator is used to boost the gain at low frequency. The zero is introduced to compensate the excessive phase lag at the loop gain crossover due to the integrator pole (-90deg) and the dominant pole (-90deg). The high frequency pole nulls the ESR zero and attenuates high frequency noise.

Figure 9 — Bode plots for voltage loop design

Therefore, the procedure of the voltage loop design for the SC4525F can be summarized as:

- 1. Plot the converter gain, i.e. control to feedback transfer function.

- 2. Select the open loop crossover frequency,  $F_{c'}$  between 10% and 20% of the switching frequency. At  $F_{c'}$  find the required compensator gain,  $A_c$ . In typical applications with ceramic output capacitors, the ESR zero is neglected and the required compensator gain at  $F_c$  can be estimated by

$$A_{C} = -20x \log \! \left( \! \frac{1}{G_{CA}R_{S}} x \frac{1}{2\pi F_{C}C_{O}} x \frac{V_{FB}}{V_{O}} \right) \label{eq:AC}$$

- 3. Place the compensator zero,  $F_{z_1}$ , between 10% and 20% of the crossover frequency,  $F_c$ .

- 4. Use the compensator pole,  $F_{P1}$ , to cancel the ESR zero,  $F_{7}$ .

- 5. Then, the parameters of the compensation network can be calculated by the following equations.

$$R_{7} = \frac{10^{\frac{A_{C}}{20}}}{g_{m}}$$

$$C_{5} = \frac{1}{2 \pi F_{Z1} R_{7}}$$

$$C_{8} = \frac{1}{2 \pi F_{P1} R_{7}}$$

where gm=0.3mA/V is the EA gain of the SC4525F.

**Example:** Determine the voltage compensator for an 350kHz, 12V to 3.3V/3A converter with 47uF ceramic output capacitor.

Choose a loop gain crossover frequency of 35kHz, and place voltage compensator zero and pole at  $F_{z_1}$ =7kHz (20% of  $F_c$ ), and  $F_{p_1}$ = 677kHz. From the equation in step 2, the required compensator gain at  $F_c$  is shown by the following equation.

$$A_{c} = -20 \cdot log \left(\frac{1}{18.5 \cdot 3.53 \cdot 10^{-3}} \cdot \frac{1}{2\pi \cdot 35 \cdot 10^{3} \cdot 47 \cdot 10^{-6}} \cdot \frac{1.0}{3.3}\right) = 7 dB$$

Then the compensator parameters are

$$R_{7} = \frac{10^{\frac{1}{20}}}{0.3 \times 10^{-3}} = 7.4k$$

$$C_{5} = \frac{1}{2\pi \times 7 \times 10^{3} \times 7.4 \times 10^{3}} = 3.1nF$$

$$C_{8} = \frac{1}{2\pi \times 677 \times 10^{3} \times 7.4 \times 10^{3}} = 32pF$$

Select  $R_7 = 7.32k$ ,  $C_5 = 3.3nF$ , and  $C_8 = 33pF$  for the design.

Compensator parameters for various typical applications are listed in Table 4.

#### **Thermal Considerations**

For the power transistor inside the SC4525F, the conduction loss  $P_{c'}$  the switching loss  $P_{sw'}$  and bootstrap circuit loss  $P_{RST}$  can be estimated using the following.

$$P_{\rm C} = \mathbf{D} \times \mathbf{V}_{\rm CESAT} \times \mathbf{I}_{\rm O}$$

$$P_{\rm SW} = \frac{1}{2} \times \mathbf{t}_{\rm S} \times \mathbf{V}_{\rm IN} \times \mathbf{I}_{\rm O} \times \mathbf{F}_{\rm SW}$$

$$P_{\rm BST} = \mathbf{D} \times \mathbf{V}_{\rm BST} \times \frac{\mathbf{I}_{\rm O}}{40}$$

where  $V_{BST}$  is the BST supply voltage and  $t_s$  is the equivalent switching time of the NPN transistor (see Table 3).

| Tuble 5 Typical Switching and |              |        |        |  |

|-------------------------------|--------------|--------|--------|--|

| Input Voltage                 | Load Current |        |        |  |

| input voltage                 | 1A           | 2A     | 3A     |  |

| 5V                            | 6.86ns       | 9.71ns | 12.5ns |  |

| 12V                           | 12.5ns       | 15.3ns | 18ns   |  |

Table 3 — Typical switching time

In addition, the quiescent current loss is

$$P_{O} = V_{IN} \times 2mA$$

The total power loss of the SC4525F is therefore

$$P_{\text{TOTAL}} = P_{\text{C}} + P_{\text{SW}} + P_{\text{BST}} = P_{\text{Q}}$$

The temperature rise of the SC4525F is the product of the total power dissipation (previous equation) and  $\theta_{JA}$  (36°C/W), which is the thermal impedance from junction to ambient for the SOIC-8 EDP package.

It is not recommended to operate the SC4525F above 125°C junction temperature.

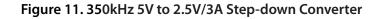

#### **PCB Layout Considerations**

In a step-down switching regulator, the input bypass capacitor, the main power switch and the freewheeling diode carry pulse currents (Figure 10). For jitter-free operation, the size of the loop formed by these components should be minimized. Since the power switch is already integrated within the SC4525F, connecting the anode of the freewheeling diode close to the negative terminal of the input bypass capacitor minimizes size of the switched current loop. The input bypass capacitor should be placed close to the IN pin. Shortening the traces of the SW and BST nodes reduces the parasitic trace inductance at these nodes. This not only reduces EMI but also decreases switching voltage spikes at these nodes.

The exposed pad should be soldered to a large ground plane as the ground copper acts as a heat sink for the device. To ensure proper adhesion to the ground plane, avoid using large vias directly under the device.

Figure 10 — Pulse Current Loop

Note: Heavy lines indicate the critical pulse current loop. The stray inductance of this loop should be minimized.

# **Recommended Component Parameters in Typical Applications**

Table 4 lists the recommended inductance (L<sub>1</sub>) and compensation network ( $R_{\gamma'} C_{s'} C_{s'}$ ) for common input and output voltages. The inductance is determined by assuming that the ripple current is 35% of load current  $I_0$ . The compensator parameters are calculated by assuming a 47µF low ESR ceramic output capacitor and a loop gain crossover frequency of  $F_{sw}$ /10.

|        | Typical Applications |       |        | Re     | ecommende | ed Paramete | ers    |

|--------|----------------------|-------|--------|--------|-----------|-------------|--------|

| Vin(V) | Vo(V)                | lo(A) | C2(uF) | L1(uH) | R7(k)     | C5(nF)      | C8(pF) |

| 3.3    | 1.0                  |       |        | 3.3    | 3.74      | 6.8         |        |

| 3.3    | 2.0                  |       |        | 2.2    | 6.49      | 3.3         | 47     |

|        | 1.5                  |       |        | 3.3    | 3.74      | 6.8         | 47     |

| 5      | 2.5                  |       | 47     | 4.7    | 6.49      | 4.7         |        |

|        | 3.3                  | 3     |        | 4.7    | 7.5       | 3.3         | 68     |

|        | 1.5                  | 0     |        | 4.7    | 3.74      | 6.8         | 82     |

|        | 2.5                  |       | -      | 6.8    | 6.98      | 4.7         | 02     |

| 12     | 3.3                  |       |        | 8.2    | 8.66      | 3.3         | 68     |

|        | 5                    |       |        | 10     | 11.5      | 2.2         | 47     |

|        | 7.5                  |       |        | 10     | 18.2      | 2.2         | יד ו   |

| Table 4. Recommended inductance | ce ( $L_1$ ) and compensator ( $R_7$ , $C_5$ , $C_8$ )                                       |

|---------------------------------|----------------------------------------------------------------------------------------------|

| Table 4. Necommended maactane   | $\mathcal{L}(\mathcal{L}_1)$ and compensator $(\mathcal{L}_7, \mathcal{L}_5, \mathcal{L}_8)$ |

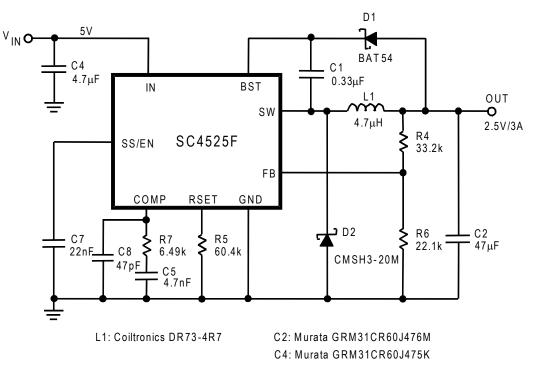

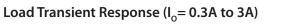

# **Typical Application Schematics**

Figure 12. 350kHz 3.3V to 1.5V/3A Step-down Converter

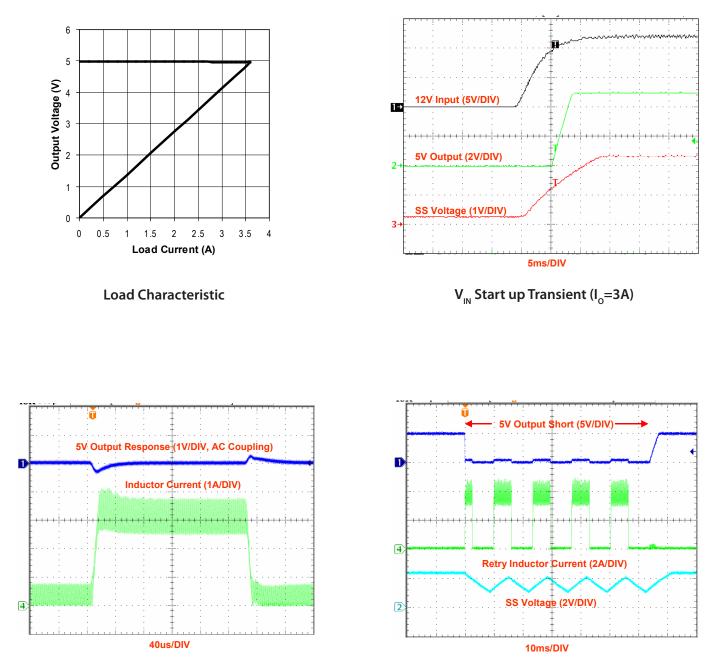

# **Typical Performance Characteristics**

(For A 12V to 5V/3A Step-down Converter with 350kHz Switching Frequency)

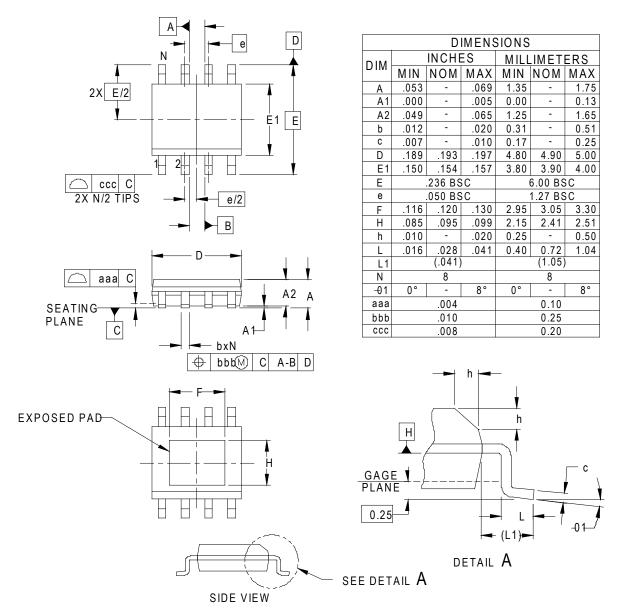

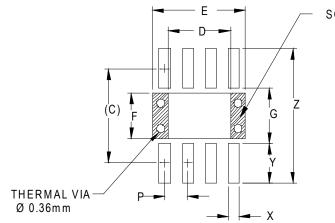

# **Outline Drawing - SOIC-8 EDP**

NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

- DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MS-012, VARIATION BA.

# Land Pattern - SOIC-8 EDP

SOLDER MASK

| DIMENSIONS |        |             |

|------------|--------|-------------|

| DIM        | INCHES | MILLIMETERS |

| С          | (.205) | (5.20)      |

| D          | .134   | 3.40        |

| E          | .201   | 5.10        |

| F          | .101   | 2.56        |

| G          | .118   | 3.00        |

| P          | .050   | 1.27        |

| Х          | .024   | 0.60        |

| Y          | .087   | 2.20        |

| Z          | .291   | 7.40        |

#### NOTES:

- 1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 2. REFERENCE IPC-SM-782A, RLP NO. 300A.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

#### © Semtech 2013

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH AP-PLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

**Contact Information**

Semtech Corporation Power Mangement Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 Fax: (805) 498-3804