# Low-Standby Power High Performance PWM Controller

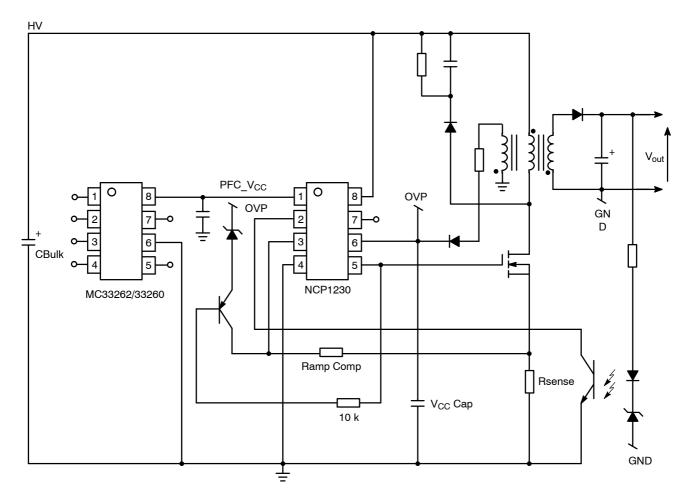

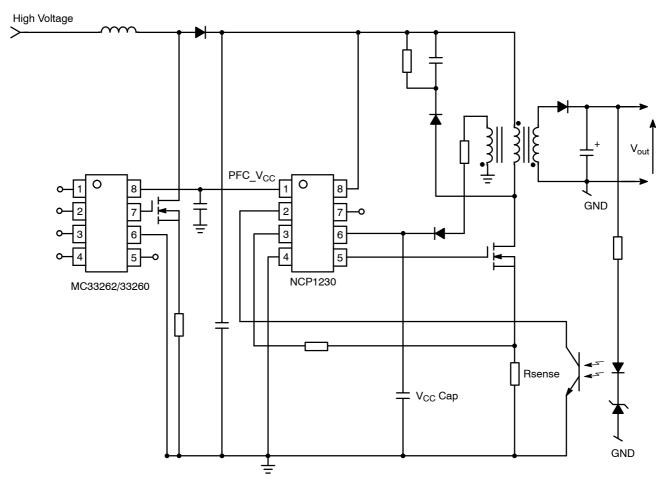

The NCP1230 represents a major leap towards achieving low standby power in medium-to-high power Switched-Mode Power Supplies such as notebook adapters, off-line battery chargers and consumer electronics equipment. Housed in a compact 8-pin package (SOIC-8, SOIC-7, or PDIP-7), the NCP1230 contains all needed control functionality to build a rugged and efficient power supply. The NCP1230 is a current mode controller with internal ramp compensation. Among the unique features offered by the NCP1230 is an event management scheme that can disable the front-end PFC circuit during standby, thus reducing the no load power consumption. The NCP1230 itself goes into cycle skipping at light loads while limiting peak current (to 25% of nominal peak) so that no acoustic noise is generated. The NCP1230 has a high-voltage startup circuit that eliminates external components and reduces power consumption.

The NCP1230 also features an internal latching function that can be used for OVP protection. This latch is triggered by pulling the CS pin above 3.0 V and can only be reset by pulling  $V_{CC}$  to ground. True overload protection, internal 2.5 ms soft-start, internal leading edge blanking, internal frequency dithering for low EMI are some of the other important features offered by the NCP1230.

### Features

- Current-Mode Operation with Internal Ramp Compensation

- Internal High-Voltage Startup Current Source for Loss-Less Startup

- Extremely Low No-Load Standby Power

- Skip-Cycle Capability at Low Peak Currents

- Direct Connection to PFC Controller for Improved No-Load Standby Power

- Internal 2.5 ms Soft-Start

- Internal Leading Edge Blanking

- Latched Primary Overcurrent and Overvoltage Protection

- Short-Circuit Protection Independent of Auxiliary Level

- Internal Frequency Jittering for Improved EMI Signature

- +500 mA/-800 mA Peak Current Drive Capability

- Available in Three Frequency Options: 65 kHz, 100 kHz, and 133 kHz

- Direct Optocoupler Connection

- SPICE Models Available for TRANsient and AC Analysis

- This is a Pb–Free Device

### **Typical Applications**

- High Power AC-DC Adapters for Notebooks, etc.

- Offline Battery Chargers

- Set-Top Boxes Power Supplies, TV, Monitors, etc.

# **ON Semiconductor®**

http://onsemi.com

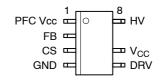

#### **PIN CONNECTIONS**

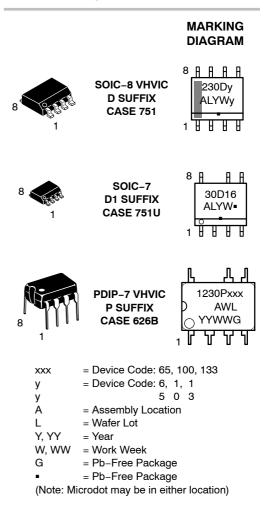

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the ordering information section on page 4 of this data sheet.

# PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name            | Function                                                        | Pin Description                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PFC V <sub>CC</sub> | This pin provides<br>the bias voltage to<br>the PFC controller. | This pin is a direct connection to the V <sub>CC</sub> pin (Pin 6) via a low impedance switch. In standby and during the startup sequence, the switch is open and the PFC V <sub>CC</sub> is shut down. As soon as the aux. winding is stabilized, Pin 1 connects to the V <sub>CC</sub> pin and provides bias to the PFC controller. It goes down in standby and fault conditions. |

| 2       | FB                  | Feedback Signal                                                 | An optocoupler collector pulls this pin low to regulate. When the current setpoint reaches 25% of the maximum peak, the controller skips cycles.                                                                                                                                                                                                                                    |

| 3       | CS/OVP              | Current Sense                                                   | This pin incorporates three different functions: the current sense function, an internal ramp compensation signal and a 3.0 V latch–off level which latches the output off until $V_{CC}$ is recycled.                                                                                                                                                                              |

| 4       | GND                 | IC Ground                                                       | -                                                                                                                                                                                                                                                                                                                                                                                   |

| 5       | DRV                 | Driver Output                                                   | With a drive capability of +500 mA / –800 mA, the NCP1230 can drive large Qg MOSFETs.                                                                                                                                                                                                                                                                                               |

| 6       | V <sub>CC</sub>     | V <sub>CC</sub> Input                                           | The controller accepts voltages up to 18 V and features a UVLO turn-off threshold of 7.7 V typical.                                                                                                                                                                                                                                                                                 |

| 7       | NC                  | -                                                               | -                                                                                                                                                                                                                                                                                                                                                                                   |

| 8       | HV                  | High–Voltage                                                    | This pin connects to the bulk voltage and offers a lossless startup sequence. The charging current is high enough to support the bias needs of a PWM controller through Pin 1.                                                                                                                                                                                                      |

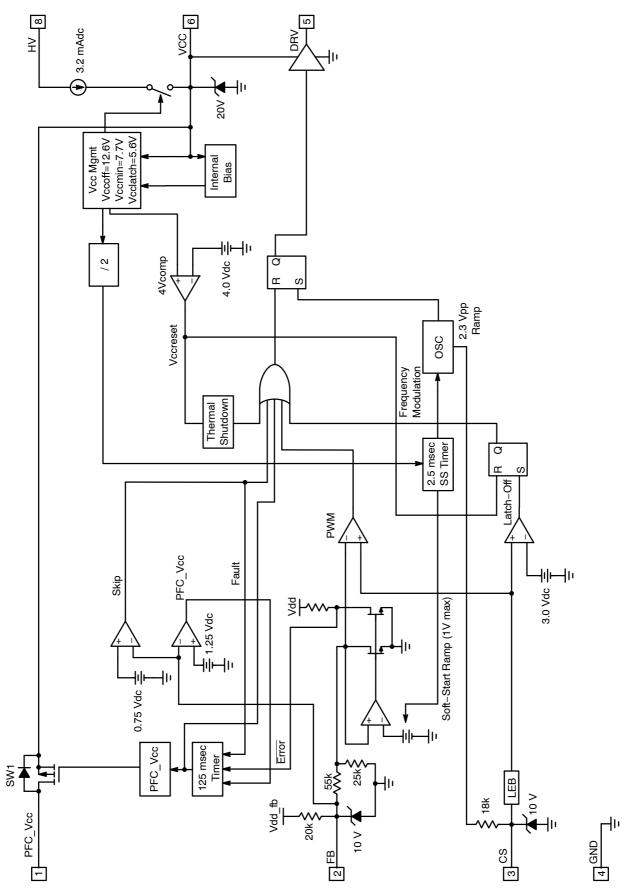

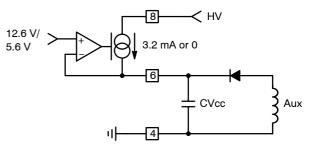

Figure 2. Internal Circuit Architecture

#### MAXIMUM RATINGS (Notes 1 and 2)

| Rating                                            |              | Symbol           | Value         | Unit |

|---------------------------------------------------|--------------|------------------|---------------|------|

| Maximum Voltage on Pin 8                          |              | V <sub>DS</sub>  | -0.3 to 500   | V    |

| Maximum Current                                   |              | I <sub>C2</sub>  | 100           | mA   |

| Power Supply Voltage, Pin 6                       |              | V <sub>CC</sub>  | –0.3 to 18    | V    |

| Current                                           |              | I <sub>CC2</sub> | 100           | mA   |

| Drive Output Voltage, Pin 5                       |              | V <sub>DV</sub>  | 18            | V    |

| Drive Current                                     |              | I <sub>o</sub>   | 1.0           | A    |

| Voltage Current Sense Pin, Pin 3                  |              | V <sub>cs</sub>  | 10            | V    |

| Current                                           |              | I <sub>cs</sub>  | 100           | mA   |

| Voltage Feedback, Pin 2                           |              | V <sub>fb</sub>  | 10            | V    |

| Current                                           |              | I <sub>fb</sub>  | 100           | mA   |

| Voltage, Pin 1                                    |              | V <sub>PFC</sub> | 18            | V    |

| Maximum Continuous Current Flowing from Pin 1     |              | I <sub>PFC</sub> | 35            | mA   |

| Thermal Resistance, Junction-to-Air, PDIP Version |              | $R_{	hetaJA}$    | 100           | °C/W |

| Thermal Resistance, Junction-to-Air, SOIC Version |              | $R_{	hetaJA}$    | 178           | °C/W |

| Maximum Power Dissipation @ T <sub>A</sub> = 25°C | PDIP<br>SOIC | P <sub>max</sub> | 1.25<br>0.702 | w    |

| Maximum Junction Temperature                      |              | TJ               | 150           | °C   |

| Storage Temperature Range                         |              | T <sub>stg</sub> | -60 to +150   | °C   |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1. This device series contains ESD protection and exceeds the following tests:

Pin 1–6: Human Body Model 2000 V per Mil–Std–883, Method 3015. Machine Model Method 200 V

Pin 8 is the HV startup of the device and is rated to the maximum rating of the part, or 500 V.

2. This device contains latchup protection and exceeds 100 mA per JEDEC Standard JESD78.

### **ORDERING INFORMATION**

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCP1230D165R2G | SOIC–7<br>(Pb–Free) | 2500 / Tape & Reel    |

| NCP1230D65R2G  | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP1230D100R2G | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

| NCP1230D133R2G | SOIC–8<br>(Pb–Free) | 2500 / Tape & Reel    |

| NCP1230P65G    | PDIP–7<br>(Pb–Free) | 50 Units/ Rail        |

| NCP1230P100G   | PDIP-7<br>(Pb-Free) | 50 Units/ Rail        |

| NCP1230P133G   | PDIP-7<br>(Pb-Free) | 50 Units/ Rail        |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

| <b>ELECTRICAL CHARACTERISTICS</b> (For typical values $T_J = 25^{\circ}C$ , for min/max values $T_J = -40^{\circ}C$ to +125°C, Max $T_J = 150^{\circ}C$ , |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CC</sub> = 13 V, V <sub>PIN8</sub> = 30 V unless otherwise noted.)                                                                                 |  |

| Characteristic                                                                                                                      | Symbol                                       | Pin | Min            | Тур        | Max            | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|----------------|------------|----------------|------|

| Supply Section (All frequency versions, otherwise noted)                                                                            |                                              |     |                |            |                |      |

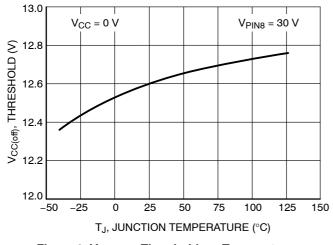

| Turn–On Threshold Level, $V_{CC}$ Going Up (V <sub>fb</sub> = 2.0 V)                                                                | V <sub>CCOFF</sub>                           | 6   | 11.6           | 12.6       | 13.6           | V    |

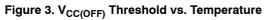

| Minimum Operating Voltage after Turn-On                                                                                             | V <sub>CC(min)</sub>                         | 6   | 7.0            | 7.7        | 8.4            | V    |

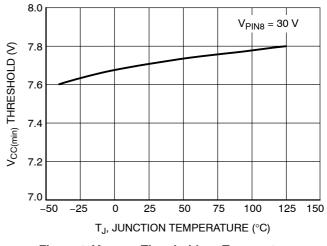

| $V_{CC}$ Decreasing Level at which the Latch–Off Phase Ends (V_{fb} = 3.5 V)                                                        | V <sub>CClatch</sub>                         | 6   | 5.0            | 5.6        | 6.2            | V    |

| V <sub>CC</sub> Level at which the Internal Logic gets Reset                                                                        | V <sub>CCreset</sub>                         | 6   | -              | 4.0        | -              | V    |

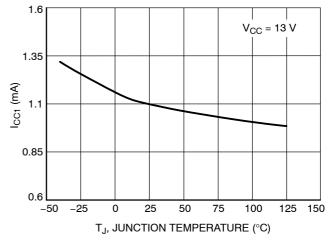

| Internal IC Consumption, No Output Load on Pin 6 ( $V_{fb}$ = 2.5 V)                                                                | I <sub>CC1</sub>                             | 6   | 0.6            | 1.1        | 1.8            | mA   |

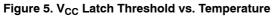

| Internal IC Consumption, 1.0 nF Output Load on Pin 6, $F_{SW}$ = 65 kHz $(V_{fb}$ = 2.5 V)                                          | I <sub>CC2</sub>                             | 6   | 1.3            | 1.8        | 2.5            | mA   |

| Internal IC Consumption, 1.0 nF Output Load on Pin 6, F <sub>SW</sub> = 100 kHz                                                     | I <sub>CC2</sub>                             | 6   | 1.3            | 2.2        | 3.0            | mA   |

| Internal IC Consumption, 1.0 nF Output Load on Pin 6, F <sub>SW</sub> = 133 kHz                                                     | I <sub>CC2</sub>                             | 6   | 1.3            | 2.8        | 3.3            | mA   |

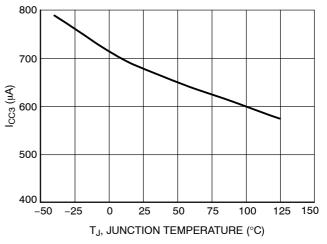

| Internal IC Consumption, Latch-Off Phase                                                                                            | I <sub>CC3</sub>                             | 6   | 400            | 680        | 1000           | μA   |

| Internal Startup Current Source                                                                                                     |                                              |     |                |            |                | -    |

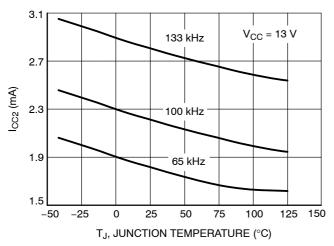

| High-Voltage Current Source, 1.0 nF Load $(V_{CCOFF}$ -0.2 V, $V_{fb}$ = 2.5 V, $V_{PIN8}$ = 30 V)                                  | I <sub>C1</sub>                              | 8   | 1.8            | 3.2        | 4.2            | mA   |

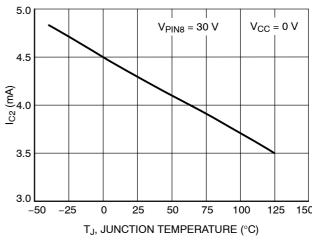

| High-Voltage Current Source (V <sub>CC</sub> = 0 V)                                                                                 | I <sub>C2</sub>                              | 8   | 1.8            | 4.4        | 5.6            | mA   |

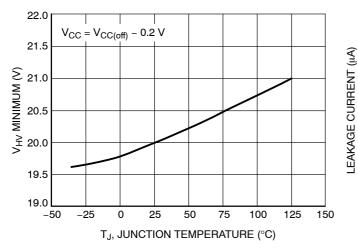

| Minimum Startup Voltage (I <sub>c</sub> = 0.5 mA, V <sub>CCOFF</sub> –0.2 V, V <sub>fb</sub> = 2.5 V)                               | V <sub>HVmin</sub>                           | 8   | -              | 20         | 23             | V    |

| Startup Leakage (V <sub>PIN8</sub> = 500 V)                                                                                         | I <sub>HVLeak</sub>                          | 8   | 10             | 30         | 80             | μA   |

| Drive Output                                                                                                                        |                                              |     |                |            |                |      |

| Output Voltage Rise-Time @ C <sub>L</sub> = 1.0 nF, 10-90% of Output Signal                                                         |                                              | 5   | -              | 40         | -              | ns   |

| Output Voltage Fall-Time @ $C_L$ = 1.0 nF, 10–90% of Output Signal                                                                  |                                              | 5   | -              | 15         | -              | ns   |

| Source Resistance, $R_{Load}$ 300 $\Omega$ (V <sub>fb</sub> = 2.5 V)                                                                |                                              | 5   | 6.0            | 12.3       | 25             | Ω    |

| Sink Resistance, at 1.0 V on Pin 5 (V <sub>fb</sub> = 3.5 V)                                                                        | R <sub>OL</sub>                              | 5   | 3.0            | 7.5        | 18             | Ω    |

| Pin 1 Output Impedance (or $R_{dson}$ between Pin 1 and Pin 6 when SW1 is closed) $R_{load}$ on Pin 1 = 680 $\Omega$                |                                              | 1   | 6.0            | 11.7       | 23             | Ω    |

| Current Comparator and Thermal Shutdown                                                                                             |                                              | •   | •              |            |                |      |

| Input Bias Current @ 1.0 V Input Level on Pin 3                                                                                     | I <sub>IB</sub>                              | 3   | -              | 0.02       | -              | μA   |

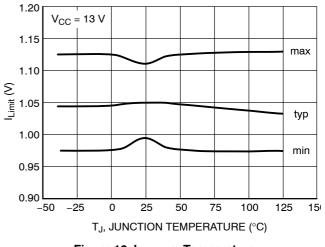

| $\label{eq:maximum lnternal Current Setpoint} \begin{array}{c} Tj = 25^\circ C \\ Tj = -40^\circ C \ to \ +125^\circ C \end{array}$ | I <sub>Limit</sub>                           | 3   | 1.010<br>0.979 | 1.063<br>- | 1.116<br>1.127 | V    |

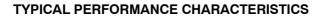

| Default Internal Setpoint for Skip Cycle Operation and Standby<br>Detection                                                         |                                              | 3   | 600            | 750        | 900            | mV   |

| Default Internal Setpoint to Leave Standby                                                                                          |                                              | -   | 1.0            | 1.25       | 1.5            | V    |

| Propagation Delay from CS Detected to Gate Turned Off ( $V_{Gate} = 10 \text{ V}$ )<br>(Pin 5 Loaded by 1.0 nF)                     | V <sub>stby-out</sub><br>T <sub>DEL CS</sub> | 3   | -              | 90         | 180            | ns   |

| Leading Edge Blanking Duration                                                                                                      | T <sub>LEB</sub>                             | 3   | 100            | 200        | 350            | ns   |

| Soft-Start Period (Note 3)                                                                                                          | SS                                           | -   | -              | 2.5        | -              | ms   |

| Temperature Shutdown, Maximum Value (Note 3)                                                                                        | T <sub>SD</sub>                              | -   | 150            | 165        | -              | °C   |

| Hysteresis while in Temperature Shutdown (Note 3)                                                                                   | T <sub>SD</sub> hyste                        | -   | -              | 25         | -              | °C   |

3. Verified by Design.

| <b>ELECTRICAL CHARACTERISTICS</b> (For typical values $T_J = 25^{\circ}$ C, for min/max values $T_J = -40^{\circ}$ C to $+125^{\circ}$ C, Max $T_J = 150^{\circ}$ C, |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{CC}$ = 13 V, $V_{PIN8}$ = 30 V unless otherwise noted.)                                                                                                          |  |

| Characteristic                                                                                                                                                                       | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin | Min               | Тур           | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|---------------|-------------------|------|

| Internal Oscillator                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | •                 |               |                   |      |

| Oscillation Frequency, 65 kHz Version (V <sub>fb</sub> = 2.5 V)<br>Tj = 25°C<br>Tj = 0°C to +125°C<br>Tj = -40°C to +125°C                                                           | fosc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -   | 60<br>58<br>55    | 65<br>-<br>-  | 70<br>72<br>72    | kHz  |

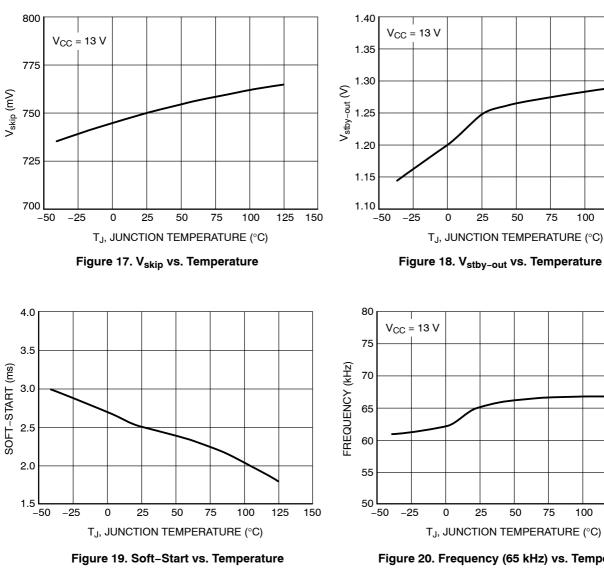

| $ \begin{array}{ll} \mbox{Oscillation Frequency, 100 kHz Version} & Tj = 25^{\circ}C \\ Tj = 0^{\circ}C \ to \ +125^{\circ}C \\ Tj = -40^{\circ}C \ to \ +125^{\circ}C \end{array} $ | fosc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -   | 93<br>90<br>85    | 100<br>-<br>- | 107<br>110<br>110 | kHz  |

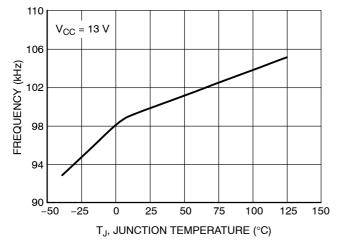

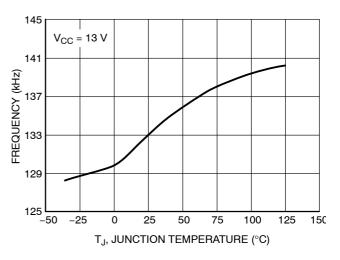

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                | fosc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -   | 123<br>120<br>113 | 133<br>-<br>- | 143<br>146<br>146 | kHz  |

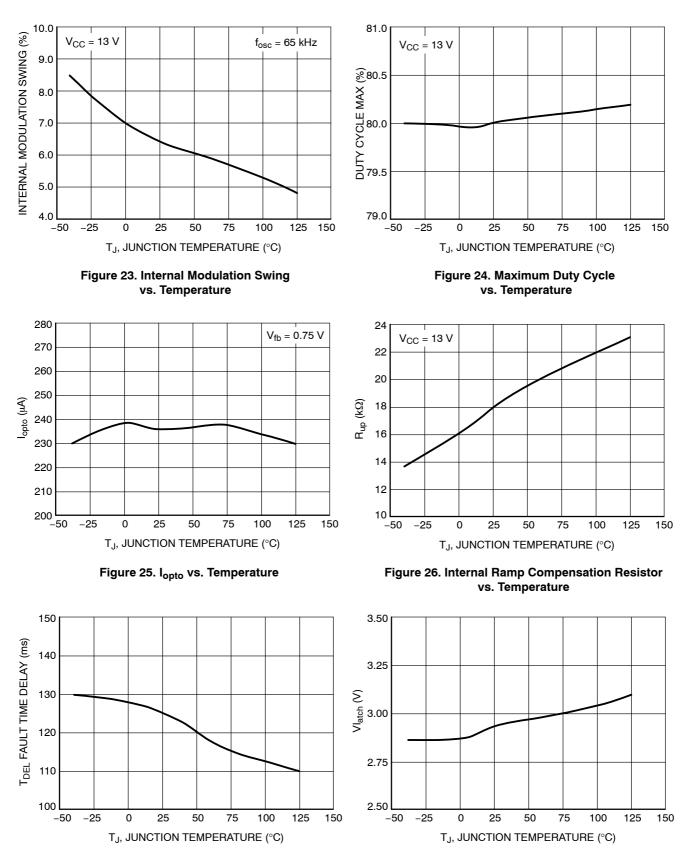

| Internal Modulation Swing, in Percentage of $F_{sw}$ (V <sub>fb</sub> = 2.5 V) (Note 4)                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | -                 | ±6.4          | -                 | %    |

| Internal Swing Period (Note 4)                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | -                 | 5.0           | -                 | ms   |

| Maximum Duty-Cycle (CS = 0, V <sub>fb</sub> = 2.5 V)                                                                                                                                 | D <sub>max</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -   | 75                | 80            | 85                | %    |

| Internal Ramp Compensation                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                   | -             | -                 |      |

| Internal Resistor (Note 4)                                                                                                                                                           | R <sub>up</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3   | 9.0               | 18            | 36                | kΩ   |

| Ramp Compensation Sawtooth Amplitude                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3   | -                 | 2.3           | -                 | Vpp  |

| Feedback Section                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |                   | -             |                   |      |

| Opto Current Source (V <sub>fb</sub> = 0.75 V)                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2   | 200               | 235           | 270               | μA   |

| Pin 3 to Current Setpoint Division Ratio (Note 4)                                                                                                                                    | I <sub>ratio</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -   | -                 | 2.8           | -                 | -    |

| Protection                                                                                                                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | -                 | -             | -                 | -    |

| Timeout before Validating Short–Circuit or PFC $V_{CC}$ (Note 4)                                                                                                                     | T <sub>DEL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -   | -                 | 125           | -                 | ms   |

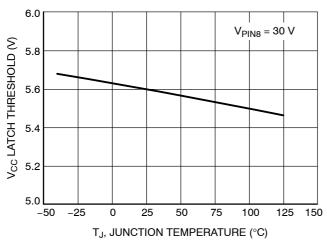

| Latch-Off Level                                                                                                                                                                      | V <sub>latch</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3   | 2.7               | 3.0           | 3.3               | V    |

| . Verified by Design.                                                                                                                                                                | Iatch  IIatch  Iatch  III  IIII  III  III  III  III  III  III  III | 5   | 2.1               | 5.0           | 0.0               | v    |

4. Verified by Design.

Figure 9. I<sub>C1</sub> Startup Current vs. Temperature

Figure 6. I<sub>CC1</sub> Internal Current Consumption, No Load vs. Temperature

Figure 8. I<sub>CC3</sub> Internal Consumption, Latch–Off Phase vs. Temperature

Figure 10. I<sub>C2</sub> Startup Current vs. Temperature

Figure 11. Minimum Startup Voltage vs. Temperature

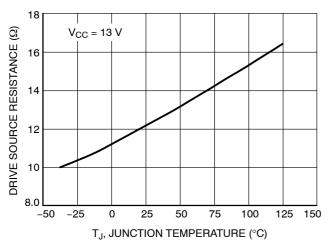

Figure 13. Drive Source Resistance vs. Temperature

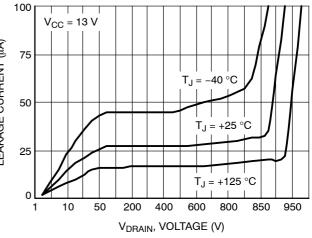

Figure 12. Leakage Current vs. Temperature

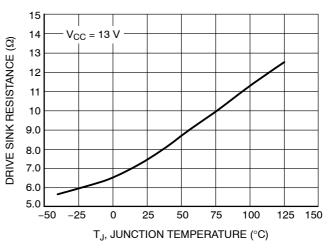

Figure 14. Drive Sink Resistance vs. Temperature

Figure 16. I<sub>Limit</sub> vs. Temperature

Figure 21. Frequency (100 kHz) vs. Temperature

Figure 20. Frequency (65 kHz) vs. Temperature

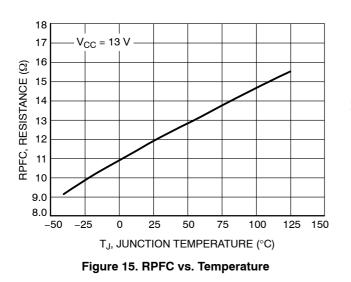

15C

Figure 22. Frequency (133 kHz) vs. Temperature

Figure 27. Fault Time Delay vs. Temperature

Figure 28. Vl<sub>atch</sub> vs. Temperature

### **OPERATING DESCRIPTION**

### Introduction

The NCP1230 is a current mode controller which provides a high level of integration by providing all the required control logic, protection, and a PWM Drive Output into a single chip which is ideal for low cost, medium to high power off-line application, such as notebook adapters, battery chargers, set-boxes, TV, and computer monitors.

The NCP1230 can be connected directly to a high voltage source providing lossless startup, and eliminating external startup circuitry. In addition, the NCP1230 has a PFC\_V<sub>CC</sub> output pin which provides the bias supply power for a Power Factor Correction controller, or other logic. The NCP1230 has an event management scheme which disables the PFC\_V<sub>CC</sub> output during standby, and overload conditions.

### $PFC_V_{CC}$

As shown on the internal NCP1230 diagram, an internal low impedance switch SW1 routes Pin 6 (V<sub>CC</sub>) to Pin 1 when the power supply is operating under nominal load conditions. The PFC\_V<sub>CC</sub> signal is capable of delivering up to 35 mA of continuous current for a PFC Controller, or other logic.

Connecting the NCP1230 PFC\_V<sub>CC</sub> output to a PFC Controller chip is very straight forward, refer to the "Typical Application Example" all that is generally required is a small decoupling capacitor  $(0.1 \ \mu F)$ .

#### Feedback

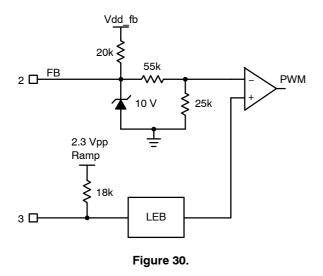

The feedback pin has been designed to be connected directly to the open-collector output of an optocoupler. The pin is pulled-up through a 20 k $\Omega$  resistor to the internal Vdd\_fb supply (5 volts nominal). The feedback input signal is divided down, by a factor of three, and connected to the negative (-) input of the PWM comparator. The positive (+) input to the PWM comparator is the current sense signal (Figure 30).

The NCP1230 is a peak current mode controller, where the feedback signal is proportional to the output power. At the beginning of the cycle, the power switch is turns–on and the current begins to increase in the primary of the transformer, when the peak current crosses the feedback voltage level, the PWM comparators switches from a logic level low, to a logic level high, resetting the PWM latching Flip–Flop, turning off the power switch until the next oscillator clock cycle begins.

The feedback pin input is clamped to a nominal 10 volt for ESD protection.

#### Skip Mode

The feedback input is connected in parallel with the skip cycle logic (Figure 31). When the feedback voltage drops below 25% of the maximum peak current (1.0 V/Rsense) the IC prevents the current from decreasing any further and starts to blank the output pulses. This is called the skip cycle mode. While the controller is in the burst mode the power transfer now depends upon the duty cycle of the pulse burst width which reduces the average input power demand.

$$V_c = I_{pk} \cdot R_s \cdot 3$$

where:

$V_c$  = control voltage (Feedback pin input),  $I_{pk}$  = Peak primary current,

$R_s$  = Current sense resistor,

3 = Feedback divider ratio.

SkipLevel =

$$3V \cdot 25\% = 0.75V$$

$$I_{pk} = \frac{0.75}{R_s \cdot 3}$$

where:

$$I_{pk} \cdot R_s = 1V$$

$$I_{pk} = \sqrt{\frac{2 \cdot P_{in}}{L_p \cdot f}}$$

where:

$P_{in}$  = is the power level where the NCP1230 will go into the skip mode

$L_p$  = Primary inductance

f = NCP1230 controller frequency

$$P_{in} = \frac{L_p \cdot f \cdot I_{pk}^2}{2}$$

$$P_{in} = \frac{P_{out}}{Eff}$$

where:

Eff = the power supply efficiency

$$R_{out} = \frac{E_{out}^2}{P_{out}}$$

### Figure 31.

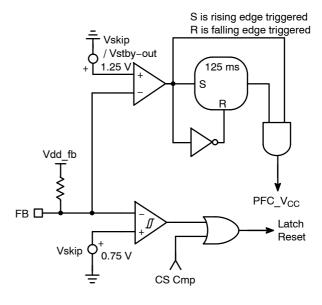

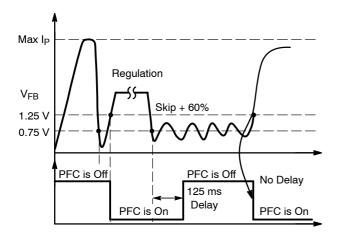

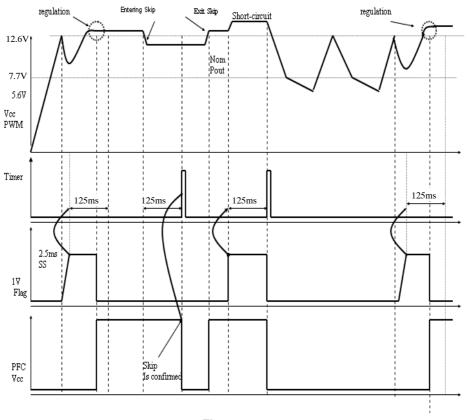

During the skip mode the PFC\_Vcc signal (pin 1) is asserted into a high impedance state when a light load condition is detected and confirmed, Figure 32 shows typical waveforms. The first section of the waveform shows a normal startup condition, where the output voltage is low, as a result the feedback signal will be high asking the controller to provide the maximum power to the output. The second phase is under normal loading, and the output is in regulation. The third phase is when the output power drops below the 25% threshold (the feedback voltage drops to 0.75 volts). When this occurs, the 125 msec timer starts, and if the conditions is still present after the time output period, the NCP1230 confirms that the low output power condition is present, and the internal SW1 opens, and the PFC\_Vcc signal output is shuts down. While the NCP1230 is in the skip mode the FB pin will move around the 750 mV threshold level, with approximately 100 mVp-p of hysteresis on the skip comparator, at a period which depends upon the (light) loading of the power supply and its various time constants. Since this ripple amplitude superimposed over the FB pin is lower than the second threshold (1.25 volt), the PFC\_Vcc comparator output stays high (PFC\_Vcc output Pin 1 is low).

In Phase four, the output power demands have increases and the feedback voltage rises above the 1.25 volts threshold, the NCP1230 exits the skip mode, and returns to normal operation.

Figure 32.

#### Leaving Standby (Skip Mode)

When the feedback voltage rises above the 1.25 volts reference (leaving standby) the skip cycle activity stops and SW1 immediately closes and restarts the PFC, there is no delay in turning on SW1 under these conditions, refer to Figure 32.

#### **Current Sense**

The NCP1230 is a peak current mode controller, where the current sense input is internally clamped to 1.0 V, so the sense resister is determined by Rsense = 1.0 V /Ipk maximum.

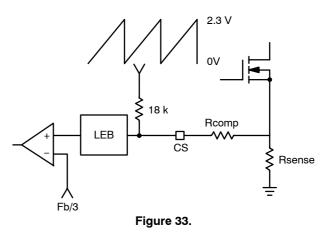

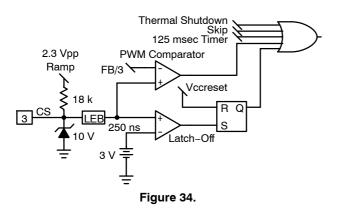

There is a 18k resistor connected to the CS pin, the other end of the 18k resistor is connect to the output of the internal oscillator for ramp compensation (refer to Figure 33).

#### Ramp Compensation

In Switch Mode Power Supplies operating in Continuous Conduction Mode (CCM) with a duty-cycle greater than 50%, oscillation will take place at half the switching frequency. To eliminate this condition, Ramp Compensation can be added to the current sense signal to cure sub harmonic oscillations. To lower the current loop gain one typically injects between 50 and 100% of the inductor down slope.

The NCP1230 provides an internal 2.3 Vpp ramp which is summed internally through a 18 k $\Omega$  resistor to the current sense pin. To implement ramp compensation a resistor needs to be connected from the current sense resistor, to the current sense pin 3.

Example:

If we assume we are using the 65 kHz version of the NCP1230, at 65 kHz the dv/dt of the ramp is 130 mV/ $\mu$ s. Assuming we are designing a FLYBACK converter which has a primary inductance, Lp, of 350  $\mu$ H, and the SMPS has a +12 V output with a Np:Ns ratio of 1:0.1. The OFF time primary current slope is given by:

$$\frac{(V_{out} + V_{f}) \cdot \frac{Ns}{Np}}{L_{p}} = 371 \text{ mA/}\mu \text{s or } 37 \text{ mV/}\mu \text{s}$$

when imposed on a current sense resistor (Rsense) of 0.1  $\Omega$ . If we select 75% of the inductor current downslope as our required amount of ramp compensation, then we shall inject 27 mV/ $\mu$ s.

With our internal compensation being of 130 mV, the divider ratio (*divratio*) between Rcomp and the 18 k $\Omega$  is 0.207. Therefore:

$$R_{comp} = \frac{18k \cdot divratio}{(1 - divratio)} = 4.69 \text{ k}\Omega$$

### Leading Edge Blanking

In Switch Mode Power Supplies (SMPS) there can be a large current spike at the beginning of the current ramp due to the Power Switch gate to source capacitance, transformer interwinding capacitance, and output rectifier recovery time. To prevent prematurely turning off the PWM drive output, a Leading Edges Blanking (LEB) (Figure 34) circuit is place is series with the current sense input, and PWM comparator. The LEB circuit masks the first 250 ns of the current sense signal.

#### **Short-Circuit Condition**

The NCP1230 is different from other controllers which use an auxiliary windings to detect events on the isolated secondary output. There maybe some conditions (for example when the leakage inductance is high) where it can be extremely difficult to implement short-circuit and overload protection. This occurs because when the power switch opens, the leakage inductance superimposes a large spike on the switch drain voltage. This spike is seen on the isolated secondary output and on the auxiliary winding. Because the auxiliary winding and diode form a peak rectifier, the auxiliary Vcc capacitor voltage can be charged up to the peak value rather than the true plateau which is proportional to the output level.

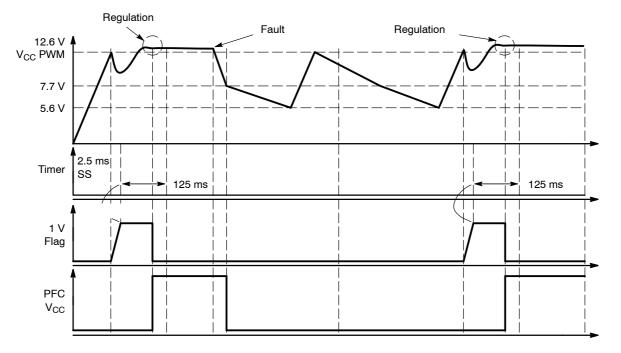

To resolve these issues the NCP1230 monitors the 1.0 V error flag. As soon as the internal 1.0 V error flag is asserted high, a 125 ms timer starts. If at the end of the 125 ms timeout period, the error flag is still asserted then the controller determines that there is a true fault condition and stops the PWM drive output, refer to Figure 35. When this occurs, Vcc starts to decrease because the power supply is locked out. When Vcc drops below UVLOlow (7.7 V typical), it enters a latch-off phase where the internal consumption is reduced down to 680 µA (typical). The voltage on the Vcc capacitor continues to drop, but at a lower rate. When Vcc reaches the latch-off level (5.6 V), the current source is turned on and pulls Vcc above UVLOhigh. To limit the fault output power, a divide-by-two circuit is connected to the Vcc pin that requires two startup sequences before attempting to restart the power supply. If the fault has gone and the error flag is low, the controller resumes normal operations.

Under transient load conditions, if the error flag is asserted, the error flag will normally drop prior to the 125 ms timeout period and the controller continues to operate normally.

If the 125 msec timer expires while the NCP1230 is in the Skip Mode, SW1 opens and the PFC\_Vcc output will shut down and will not be activated until the fault goes away and the power supply resumes normal operations.

While in the Skip Mode, to avoid any thermal runaway it is desirable for the Burst duty cycle to be kept below 20%(the burst duty-cycle is defined as Tpulse / Tfault).

The latch–off phase can also be initiated, more classically, when Vcc drops below UVLO (7.7 V typical). During this fault detection method, the controller will not wait for the

125 ms time-out, or the error flag before it goes into the latch-off phase, operating in the skip mode under these conditions, refer to Figure 36.

#### Current Sense Input Pin Latch-Off

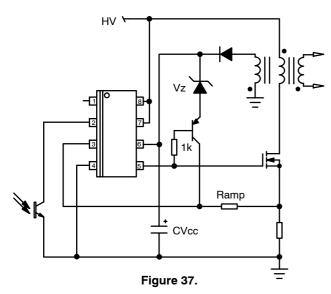

The NCP1230 features a fast comparator (Figure 34) that monitors the current sense pin during the controller off time. If for any reason the voltage on pin 3 increases above 3.0 V, the NCP1230 immediately stops the PWM drive pulses and permanently stays latched off until the bias supply to the NCP1230 is cycled down (Vcc must drop below 4.0 V, e.g. when the user unplugs the converter from the mains). This offers the designer the flexibility to implement an externally shutdown circuit (for example for overvoltage or overtemperature conditions). When the controller is latched off through pin 3 (current sense), SW1 opens and shuts off PFC Vcc output.

Figure 37 shows how to implement the external latch via a Zener diode and a simple PNP transistor. The PNP actually samples the Zener voltage during the OFF time only, hence leaving the CS information un–altered during the ON time. Various component arrangements can be made, e.g. adding a NTC device for the Over Temperature Protection (OTP).

Connecting the PNP to the drive only activates the offset generation during Toff. Here is a solution monitoring the auziliary Vcc rail.

#### **Drive Output**

The NCP1230 provides a Drive Output which can be connected through a current limiting resistor to the gate of a MOSFET. The Driver output is capable of delivering drive pulses with a rise time of 40 ns, and a fall time of 15 ns through its internal source and sink resistance of 12.3 ohms (typical), measured with a 1.0 nF capacitive load.

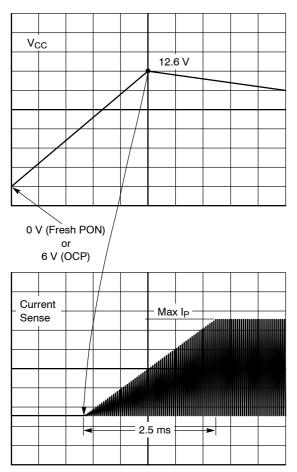

#### **Startup Sequence**

The NCP1230 has an internal High Voltage Startup Circuit (Pin 8) which is connected to the high voltage DC bus (Refer to Figure 36). When power is applied to the bus, the NCP1230 internal current source (typically 3.2 mA) is biased and charges up the external Vcc capacitor on pin 6, refer to Figure 38. When the voltage on pin 6 (Vcc) reaches Vccoff (12.6 V typically), the current source is turned off reducing the amount of power being dissipated in the chip. The NCP1230 then turns on the drive output to the external MOSFET in an attempt to increase the output voltage and charge up the Vcc capacitor through the Vaux winding in the transformer.

During the startup sequence, the controller pushes for the maximum peak current, which is reached after the 2.5 ms soft-start period. As soon as the maximum peak set point is reached, the internal 1.0 V Zener diode actively limits the current amplitude to 1.0 V/Rsense and asserts an error flag indicating that a maximum current condition is being observed. In this mode, the controller must determine if it is a normal startup period (or transient load) or is the controller is facing a fault condition. To determine the difference between a normal startup sequence, and a fault condition, the error flag is asserted, and the 125 ms timer starts to count down. If the error flag drops prior to the 125 ms time-out period, the controller resets the timer and determines that it was a normal startup sequence and enables the low impedance switch (SW1), enabling the PFC\_Vcc output.

If at the end of the 125 ms period the error flag is still asserted, then the controller assumes that it is a fault condition and the PWM controller enters the skip mode and does not enable the PFC\_Vcc output.

Figure 38.

ON Semiconductor recommends that the Vcc capacitor be at least 47  $\mu F$  to be sure that the Vcc supply voltage does not drop below Vccmin (7.7 V typical) during standby power mode and unusual fault conditions.

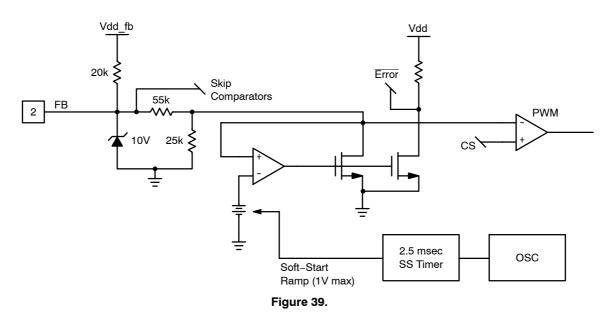

#### Soft-Start

The NCP1230 features an internal 2.5 ms soft-start circuit. As soon as Vcc reaches a nominal 12.6 V, the soft-start circuit is activated. The soft-start circuit output controls a reference on the minus (-) input to an amplifier (refer to Figure 39), the positive (+) input to the amplifier is the feedback input (divided by 3). The output of the amplifier drives a FET which clamps the feedback signal. As the soft-start circuit output ramps up, it allow the feedback pin input to the PWM comparator to gradually increased from near zero up to the maximum clamping level of 1.0 V/Rsense. This occurs over the entire 2.5 ms soft-start is also activated every time a restart is attempted. Figure 40 shows a typical soft-start up sequence.

Figure 40. Soft-Start is Activated during a Startup Sequence or an OCP Condition

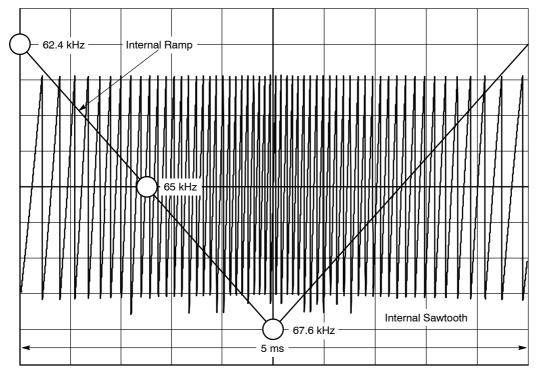

## **Frequency Jittering**

Frequency jittering is a method used to soften the EMI signature by spreading out the average switching energy around the controller operating switching frequency. The

NCP1230 offers a nominal  $\pm 6.4\%$  deviation of the nominal switching frequency. The sweep sawtooth is internally generated and modulates the clock up and down with a 5 ms period. Figure 41 illustrates the NCP1230 behavior:

Figure 41. An Internal Ramp is used to Introduce Frequency Jittering on the Oscillator Saw Tooth

## **Thermal Protection**

An internal Thermal Shutdown is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated (165°C typically) the controller turns off the PWM Drive Output. When this occurs, Vcc will drop (the rate is dependent on the NCP1230 loading and the size of the Vcc capacitor) because the controller is no longer delivering drive pulses to the auxiliary winding charging up the Vcc capacitor. When Vcc

drops below 4.0 volts and the Vccreset circuit is activated, the controller will restart. If the user is using a fixed bias supply (the bias supply is provided from a source other than from an auxiliary winding, refer to the typical application ) and Vcc is not allow to drop below 4.0 volts under a thermal shutdown condition, the NCP1230 will not restart. This feature is provided to prevent catastrophic failure from accidentally overheating the device.

# **PACKAGE DIMENSIONS**

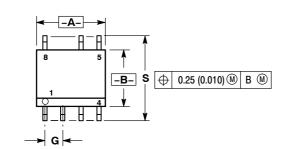

SOIC-7 **D1 SUFFIX** CASE 751U-01 **ISSUE C**

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B ARE DATUMS AND T IS A DATUM SURFACE.

DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 4.80        | 5.00  | 0.189 | 0.197 |

| В   | 3.80        | 4.00  | 0.150 | 0.157 |

| С   | 1.35        | 1.75  | 0.053 | 0.069 |

| D   | 0.33        | 0.51  | 0.013 | 0.020 |

| G   | 1.27        | 7 BSC | 0.05  | 0 BSC |

| н   | 0.10        | 0.25  | 0.004 | 0.010 |

| J   | 0.19        | 0.25  | 0.007 | 0.010 |

| ĸ   | 0.40        | 1.27  | 0.016 | 0.050 |

| М   | 0 °         | 8 °   | 0 °   | 8 °   |

| Ν   | 0.25        | 0.50  | 0.010 | 0.020 |

| S   | 5.80        | 6.20  | 0.228 | 0.244 |

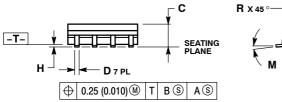

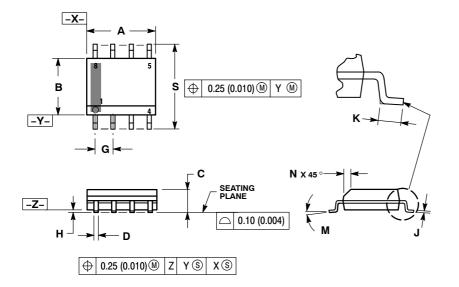

### PACKAGE DIMENSIONS

SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AJ**

NOTES:

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

751-01 THRU 751-06 ARE OBSOLETE. NEW STANDADD IS 71-07

- STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |  |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |  |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |  |

| G   | 1.27 BSC    |      | 0.050 BSC |       |  |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |  |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |  |

| к   | 0.40        | 1.27 | 0.016     | 0.050 |  |

| м   | 0 °         | 8 °  | 0 °       | 8 °   |  |

| Ν   | 0.25        | 0.50 | 0.010     | 0.020 |  |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

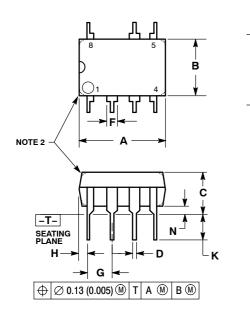

#### PACKAGE DIMENSIONS

7-LEAD PDIP P SUFFIX CASE 626B-01 ISSUE A

м

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

- DIMENSIONS IN MILLIMETERS.

DIMENSION L TO CENTER OF LEAD

- WHEN FORMED PARALLEL. 4. PACKAGE CONTOUR OPTIONAL

- (ROUND OR SQUARE CORNERS). 5. DIMENSIONS A AND B ARE DATUMS.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 9.40        | 10.16 |  |  |

| в   | 6.10        | 6.60  |  |  |

| С   | 3.94        | 4.45  |  |  |

| D   | 0.38        | 0.51  |  |  |

| F   | 1.02        | 1.78  |  |  |

| G   | 2.54        | BSC   |  |  |

| н   | 0.76        | 1.27  |  |  |

| J   | 0.20        | 0.30  |  |  |

| к   | 2.92        | 3.43  |  |  |

| L   | 7.62 BSC    |       |  |  |

| М   |             | 10 °  |  |  |

| N   | 0.76        | 1.01  |  |  |

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use patent solut. Cwas negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Dance: 041.92, 200.0010

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ON Semiconductor:

NCP1230D100R2 NCP1230D133R2 NCP1230D65R2 NCP1230P100 NCP1230P133 NCP1230P65