## **DTµL 9111**

## PARALLEL GATED-CLOCKED FLIP-FLOP

# FAIRCHILD DIODE-TRANSISTOR MICROLOGIC® INTEGRATED CIRCUITS INDUSTRIAL MICROCIRCUITS - 0°C TO +75°C TEMPERATURE RANGE

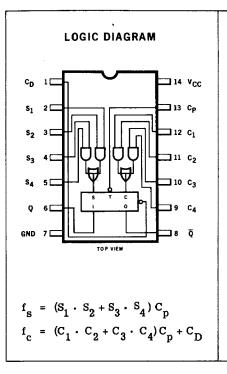

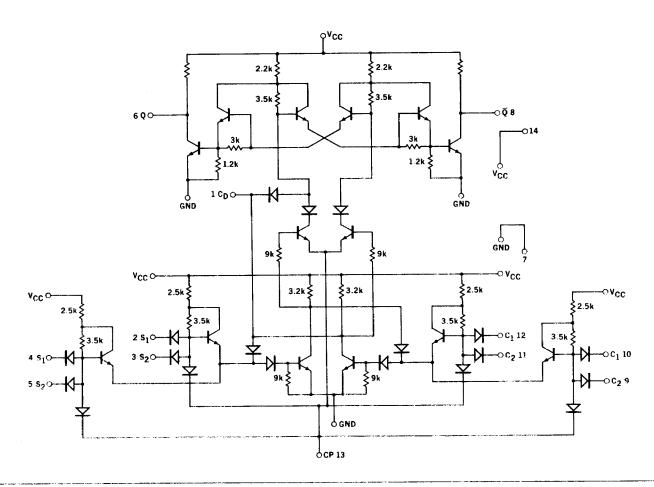

GENERAL DESCRIPTION - The  $DT\mu L9111$  is a Parallel Gated, Clocked Flip-Flop. It features directly coupled units operating on the "master-slave" principle. Operation is logically and electrically identical to the  $DT\mu L9948$  with the addition of another pair of two-input gates at the inputs of the flip-flop. This feature enhances the Logic design of some counters and shift-registers and can significantly reduce can count.

A direct clear input is provided which allows asynchronous entry irrespective of signals applied to any other inputs.

Output buffers provide isolation between the "slave" and the output load, thereby enhancing immunity to signal line noise.

The  $DT\mu L9111$  is completely compatible with all of the Fairchild 9930 Series Diode-Transistor Micrologic® integrated circuits.

#### INPUT-OUTPUT LOADING FACTORS

$$(v_{CC} = 5.0 V)$$

#### Output Drive

Pins 6 & 8 = 11

#### Input Loading

Pins 2, 3, 4, 5, 9, 10, 11, 12 = 2/3Pin 1 = 2Pin 13 = 3

#### ORDER INFORMATION:

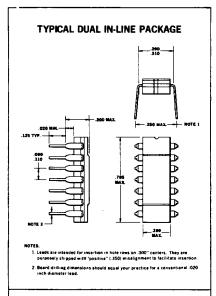

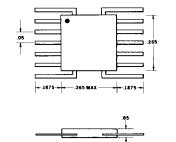

To order the DT $\mu$ L9111 element, specify the following Part Number: U31911159X for Flat Pkg. U6A911159X for Dual In-Line Pkg.

## FAIRCHILD DIODE-TRANSISTOR MICROLOGIC® I.C.

#### SCHEMATIC DIAGRAM

#### TRUTH TABLE

|     |   |   | SY | NCH  | RONO | US E | 'NTR | Υ  |                        |             |  |

|-----|---|---|----|------|------|------|------|----|------------------------|-------------|--|

|     |   |   |    | INPU |      |      |      |    | OUTI<br>t <sub>n</sub> | PUTS<br>+ 1 |  |

| Pin | 2 | 3 | 4  | 5    | 9    | 10   | 11   | 12 | 6                      | 8           |  |

|     | L | X | Ĺ  | X    | L    | X    | L    | X  | NC                     | NC          |  |

|     | X | L | X  | L    | X    | L    | X    | L  | NC                     | NC          |  |

|     | H | Н | x  | x    | L    | X    | X    | L  | н                      | L           |  |

|     | X | Х | H  | Н    | X    | L    | L    | X  | Н                      | L           |  |

|     | L | X | X  | X    | Н    | Н    | X    | X  | L                      | Н           |  |

|     | x | L | L  | X    | X    | X    | Н    | H  | L                      | H           |  |

|     | Н | Н | X  | X    | Н    | H    | X    | X  | Unde<br>mi             | ter-<br>ned |  |

|     | x | X | Н  | H    | x    | X    | Н    | H  | Unde<br>mi             | ter-<br>ned |  |

This is a partial table showing significant input-output conditions. Other conditions are similar combinations. Operation is best defined by the set and clear functions shown on Page 1.

#### For J-K Mode operation:

Connect 6 to 11 and 9; 8 to 3 and 5.

|       | ASYNCHRONOUS ENTRY*                                                                  |

|-------|--------------------------------------------------------------------------------------|

| INPUT | OUTPUTS                                                                              |

|       |                                                                                      |

| Pin 1 | 6 8                                                                                  |

| H     | NC NC                                                                                |

| L     | L H                                                                                  |

| 0     | Asynchronous entry is independent fall other inputs and overrides synchronous entry. |

#### NOTES:

- (1) Pin numbers refer to flat package or dual in-line package.

- (2) Abbreviations used in the body of tables:

- L = low, the more negative voltage level

- H = high, the more positive voltage level (In all cases, unused pins have the same effect as high.)

- X = immaterial, either H or L has equal effect

- NC = no change, the trigger-pulse has no effect on outputs

### FAIRCHILD DIODE-TRANSISTOR MICROLOGIC® I.C.

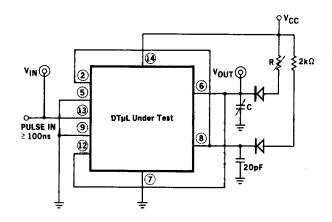

#### tpd TEST CIRCUIT

DIODES ARE FD600 OR EQUIVALENT.

ALL C's INCLUDE JIG & PROBE.

$$(V_{CC} = 5.0 \text{ V, T} = 25^{\circ}\text{C})$$

$\frac{\text{R}}{\text{t}_{pd+}} \frac{\text{C}}{2.0 \text{ k}} \frac{\text{Min.}}{30 \text{ pF}} \frac{\text{Max.}}{30 \text{ ns}} 65 \text{ ns}$   $t_{pd-}$   $330 \Omega$  50 pF 30 ns 75 ns

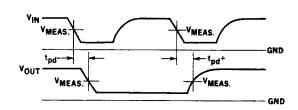

#### **WAVE FORMS**

$$V_{\text{meas.}} = 1.5 \text{ V at } +25^{\circ}\text{C}$$

#### TYPICAL APPLICATIONS

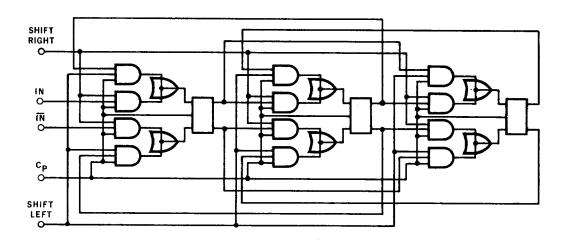

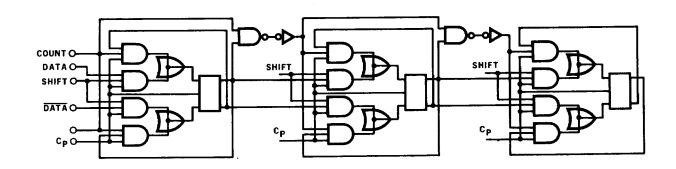

SHIFT RIGHT / SHIFT LEFT SHIFT REGISTER

## FAIRCHILD DIODE-TRANSISTOR MICROLOGIC® I.C.

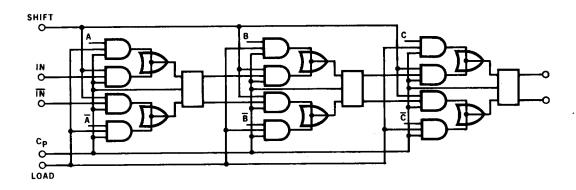

#### TYPICAL APPLICATIONS

SHIFT REGISTER WITH PARALLEL INPUT LOADING

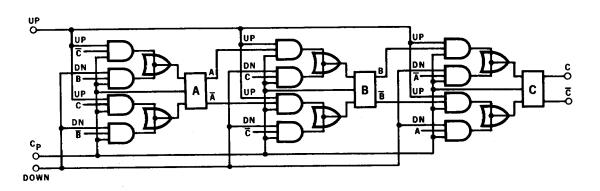

SERIAL ENTRY - BINARY COUNTER

THREE STAGE MOIBUS COUNTER