LM2775

SNVSA57 - MAY 2015

# LM2775 Switched Capacitor 5-V Boost Converter

#### **Features**

- 2.7-V to 5.5-V Input Range

- Fixed 5-V Output

- 200-mA Output Current

- Inductorless Solution: Only Requires 3 Small Ceramic Capacitors

- Shutdown Disconnects Load from V<sub>IN</sub>

- **Current Limit and Thermal Protection**

- 2-MHz Switching Frequency

- PFM Operation During Light Load Currents (PFM pin tied high)

## **Applications**

- **USB OTG**

- **HDMI** Power

- Portable Electronics

## 3 Description

The LM2775 is a regulated switched-capacitor doubler that produces a low-noise output voltage. The LM2775 can supply up to 200 mA of output current over a 3.1-V to 5.5-V input range, as well as up to 125 mA of output current when the input voltage is as low as 2.7 V. At low output currents, the LM2775 can reduce its quiescent current by operating in a pulse frequency modulation (PFM) mode. PFM mode can be enabled or disabled by driving the PFM pin to high or low. Additionally, when the LM2775 is in shutdown, the user can chose to have the output voltage pulled to GND or left in a high impedance state by setting the OUTDIS pin high or low.

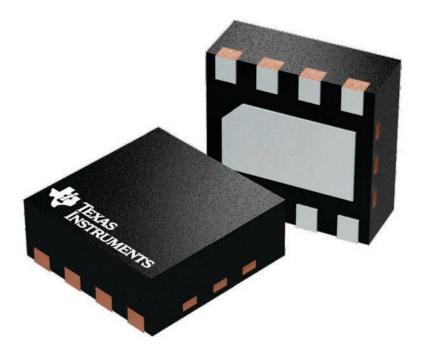

The LM2775 has been placed in TI's 8-pin WSON, a package with excellent thermal properties that keeps the part from overheating under almost all rated operating conditions.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| LM2775      | WSON (8) | 2.00 mm × 2.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

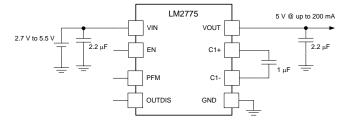

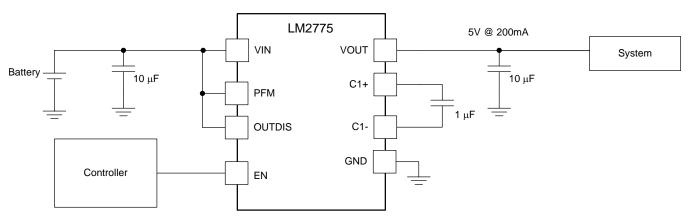

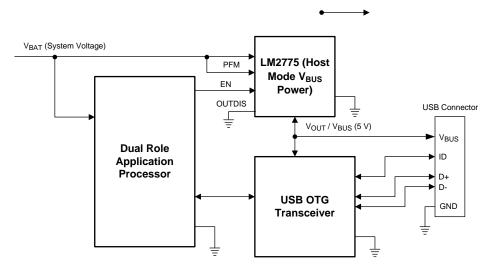

#### **Typical Application Circuit**

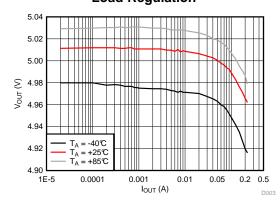

## **Load Regulation**

## **Table of Contents**

| 1 | Features 1                           | 7          | 7.2 Functional Block Diagram                    | 9  |

|---|--------------------------------------|------------|-------------------------------------------------|----|

| 2 | Applications 1                       | 7          | 7.3 Feature Description                         | 9  |

| 3 | Description 1                        | 7          | 7.4 Device Functional Modes                     | 1  |

| 4 | Revision History2                    | 8 <i>A</i> | Application and Implementation                  | 12 |

| 5 | Pin Configuration and Functions      | 8          | 3.1 Application Information                     | 1  |

| 6 | Specifications                       | 8          | 3.2 Typical Application                         | 1  |

| U | 6.1 Absolute Maximum Ratings         | 9 F        | Power Supply Recommendations                    | 17 |

|   | 6.2 ESD Ratings                      | 10 l       | _ayout                                          | 18 |

|   | 6.3 Recommended Operating Conditions | •          | 10.1 Layout Guidelines                          | 18 |

|   | 6.4 Thermal Information              | •          | 10.2 Layout Example                             | 18 |

|   | 6.5 Electrical Characteristics       | 11 [       | Device and Documentation Support                | 19 |

|   | 6.6 Switching Characteristics 5      | •          | 11.1 Trademarks                                 | 19 |

|   | 6.7 Typical Characteristics 5        | •          | 11.2 Electrostatic Discharge Caution            | 19 |

| 7 | Detailed Description9                | •          | 11.3 Glossary                                   | 19 |

| - | 7.1 Overview                         |            | Mechanical, Packaging, and Orderable nformation | 19 |

## 4 Revision History

| DATE     | REVISION                   | NOTES |

|----------|----------------------------|-------|

| May 2015 | ay 2015 * Initial release. |       |

Submit Documentation Feedback

www.ti.com

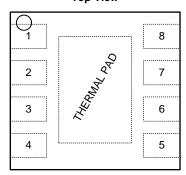

# 5 Pin Configuration and Functions

## DSG Package 8-Pin WSON with Thermal Pad Top View

## **Pin Functions**

| PIN         |        | 1/0 | DECORPTION                                                                                                                          |  |

|-------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.         | NAME   | I/O | DESCRIPTION                                                                                                                         |  |

| 1           | PFM    | I   | PFM mode enable. Allow or disallow PFM operation. 1 = PFM enabled, 0 = PWM disabled                                                 |  |

| 2           | C1-    | Р   | Flying capacitor pin                                                                                                                |  |

| 3           | C1+    | Р   | Flying capacitor pin                                                                                                                |  |

| 4           | OUTDIS | I   | Output disconnect option. 1 = Active output discharge during shutdown, 0 = High impedance output without pull-down during shutdown. |  |

| 5           | EN     | I   | Chip enable. 1 = Enabled, 0 = Disabled                                                                                              |  |

| 6           | VOUT   | 0   | Charge pump output                                                                                                                  |  |

| 7           | VIN    | Р   | Input voltage                                                                                                                       |  |

| 8           | GND    | G   | Ground                                                                                                                              |  |

| Thermal Pad | GND    | GND | Connect to GND                                                                                                                      |  |

Product Folder Links: LM2775

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                            | MIN                | MAX                                | UNIT |

|--------------------------------------------|--------------------|------------------------------------|------|

| VIN, VOUT                                  |                    | 6                                  | V    |

| EN, OUTDIS, PFM                            | -0.3               | V <sub>IN</sub> + 0.3 with 6 V Max | V    |

| Continuous power dissipation               | Internally Limited |                                    | °C   |

| Junction temperature (T <sub>J-MAX</sub> ) |                    | °C                                 |      |

| Storage temperature, T <sub>stg</sub>      | -65                | 150                                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

| .,                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±1000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                        | MIN | NOM MAX | UNIT |

|----------------------------------------|-----|---------|------|

| $V_{IN}$                               | 2.7 | 5.5     | V    |

| Junction temperature (T <sub>J</sub> ) | -40 | 125     | °C   |

| Ambient temperature (T <sub>A</sub> )  | -40 | 85      | °C   |

#### 6.4 Thermal Information

|                       |                                              | LM2775     |       |

|-----------------------|----------------------------------------------|------------|-------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DSG (WSON) | UNIT  |

|                       |                                              | 8 PINS     |       |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 71.6       |       |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 95.0       |       |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 41.5       | °C/W  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3.2        | *C/VV |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 41.8       |       |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 12.8       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: LM2775

**STRUMENTS**

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

www.ti.com

## 6.5 Electrical Characteristics

Typical limits tested at  $T_A$  = 25°C. Minimum and maximum limits apply over the full operating ambient temperature range (-40°C  $\leq T_A \leq 85$ °C).  $V_{IN}$  = 3.6 V,  $C_{IN}$  =  $C_{OUT}$  = 2.2  $\mu$ F, C1 = 1  $\mu$ F

| ( 10 0 - 14 - 00 0). T <sub>IN</sub> - 0.0 T <sub>I</sub> - 0.0 T <sub>I</sub> - 0.0 T <sub>I</sub> - 1.2 P <sub>I</sub> + 0.1 = 1 P <sub>I</sub> |                                   |                                    |     |     |                 |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|-----|-----|-----------------|------|

|                                                                                                                                                   | PARAMETER                         | TEST CONDITIONS                    | MIN | TYP | MAX             | UNIT |

| V <sub>OUT</sub>                                                                                                                                  | Output voltage regulation         | I <sub>OUT</sub> = 180 mA          | 4.8 | 5   | 5.2             | V    |

|                                                                                                                                                   | Outropent summent                 | I <sub>OUT</sub> = 0 mA, PFM = '1' |     | 75  | 150             | μΑ   |

| IQ                                                                                                                                                | Quiescent current                 | I <sub>OUT</sub> = 0 mA, PFM = '0' |     | 5   |                 | mA   |

| I <sub>SD</sub>                                                                                                                                   | Shutdown current                  | EN = '0'                           |     | 0.7 | 3               | μA   |

| I <sub>OUTDIS</sub>                                                                                                                               | Output discharge current          | OUTDIS = '1'                       |     | 500 |                 | μA   |

| I <sub>CL</sub>                                                                                                                                   | Input current limit               |                                    |     | 600 |                 | mA   |

| V <sub>IL</sub>                                                                                                                                   | Input logic low: EN, OUTDIS, PFM  |                                    | 0   |     | 0.4             | V    |

| V <sub>IH</sub>                                                                                                                                   | Input logic high: EN, OUTDIS, PFM |                                    | 1.2 |     | V <sub>IN</sub> | V    |

| UVLO                                                                                                                                              | Undervoltage lockout              | V <sub>IN</sub> falling            |     | 2.4 |                 | V    |

|                                                                                                                                                   |                                   | V <sub>IN</sub> rising             |     | 2.6 |                 | V    |

## 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER    |                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------|---------------------|-----------------|-----|-----|-----|------|

| $f_{\sf SW}$ | Switching frequency |                 | 1.7 | 2   | 2.3 | MHz  |

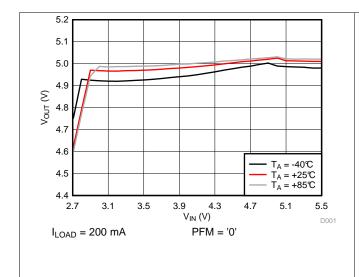

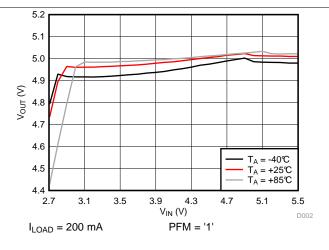

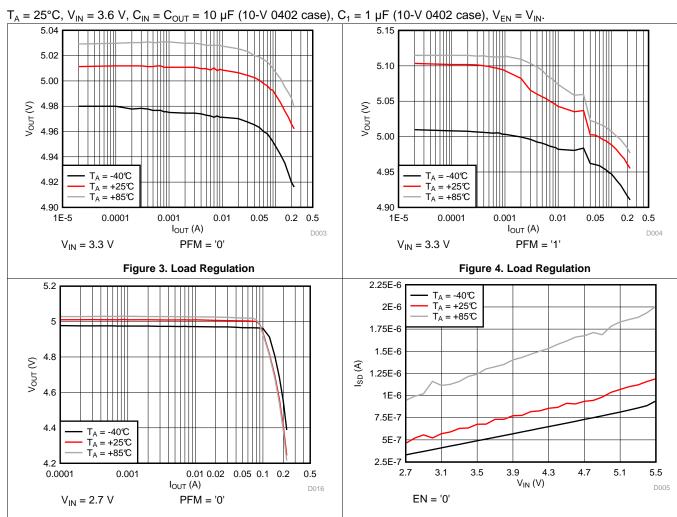

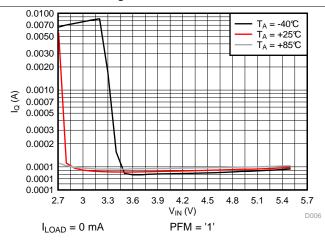

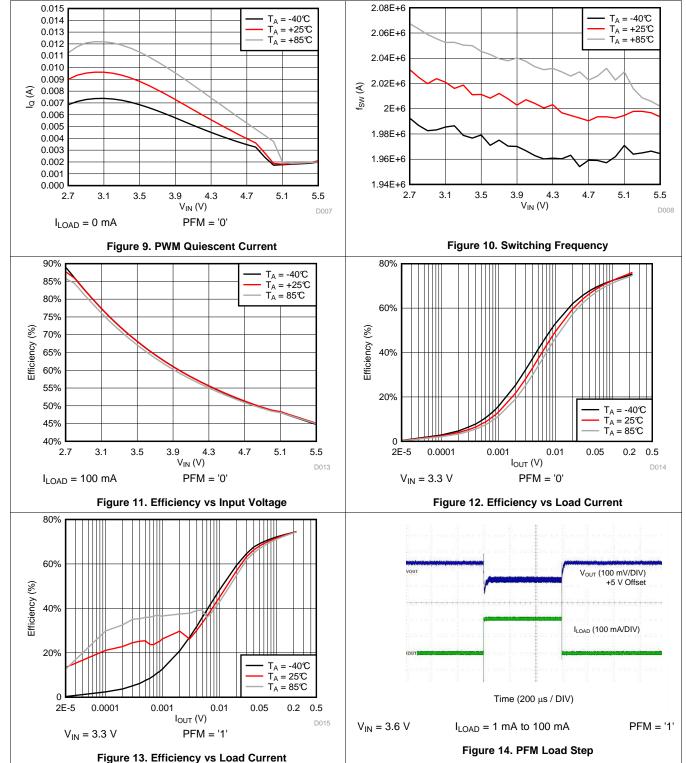

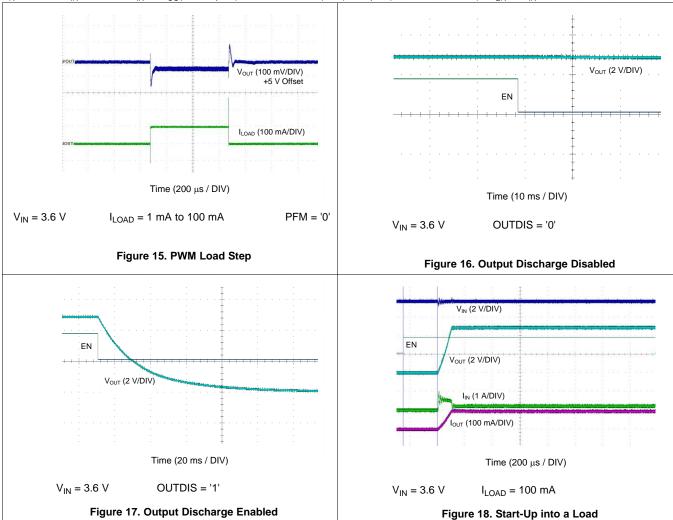

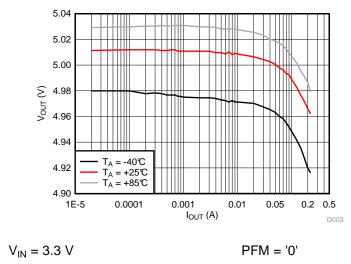

## 6.7 Typical Characteristics

$T_A = 25$ °C,  $V_{IN} = 3.6$  V,  $C_{IN} = C_{OUT} = 10$   $\mu F$  (10-V 0402 case),  $C_1 = 1$   $\mu F$  (10-V 0402 case),  $V_{EN} = V_{IN}$ .

Figure 1. PWM Output Regulation

Figure 2. PFM Output Regulation

Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback

SNVSA57 - MAY 2015 www.ti.com

# NSTRUMENTS

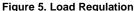

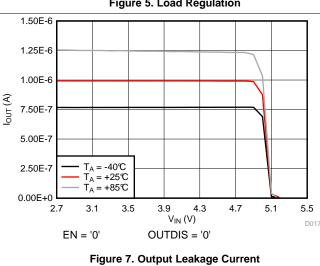

## **Typical Characteristics (continued)**

Figure 6. Shutdown Current

Figure 8. PFM Quiescent Current

www.ti.com

## **Typical Characteristics (continued)**

Copyright © 2015, Texas Instruments Incorporated

Submit Documentation Feedback

SNVSA57 –MAY 2015 www.ti.com

## **Typical Characteristics (continued)**

$T_A = 25^{\circ}C$ ,  $V_{IN} = 3.6$  V,  $C_{IN} = C_{OUT} = 10$   $\mu$ F (10-V 0402 case),  $C_1 = 1$   $\mu$ F (10-V 0402 case),  $V_{EN} = V_{IN}$ .

STRUMENTS

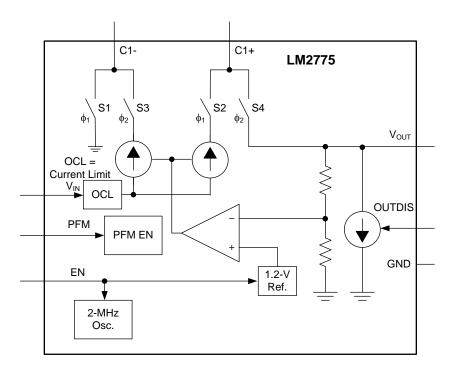

## 7 Detailed Description

#### 7.1 Overview

www.ti.com

The LM2775 is a regulated switched capacitor doubler that, by combining the principles of switched-capacitor voltage boost and linear regulation, generates a regulated output from an extended Li-lon input voltage range. A two-phase non-overlapping clock generated internally controls the operation of the doubler. During the charge phase (φ1), the flying capacitor (C1) is connected between the input and ground through internal pass transistor switches and is charged to the input voltage. In the pump phase that follows ( $\varphi$ 2), the flying capacitor is connected between the input and output through similar switches. Stacked atop the input, the charge of the flying capacitor boosts the output voltage and supplies the load current.

A traditional switched capacitor doubler operating in this manner uses switches with very low on-resistance to generate an output voltage that is 2x the input voltage. Regulation is achieved by modulating the current of the two switches connected to the VIN pin (one switch in each phase).

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Pre-Regulation

The very low input current ripple of the LM2775, resulting from internal pre-regulation, adds minimal noise to the input line. The core of the LM2775 is very similar to that of a basic switched capacitor doubler: it is composed of four switches and a flying capacitor (external). Regulation is achieved by controlling the current through the two switches connected to the VIN pin (one switch in each phase). The regulation is done before the voltage doubling, giving rise to the term "pre-regulation". It is pre-regulation that eliminates most of the input current ripple that is a typical and undesirable characteristic of a many switched capacitor converters.

## 7.3.2 Input Current Limit

Copyright © 2015, Texas Instruments Incorporated

The LM2775 contains current limit circuitry that protects the device in the event of excessive input current and/or output shorts to ground. The input current is limited to 600 mA (typical) when the output is shorted directly to ground. When the LM2775 is current limiting, power dissipation in the device is likely to be guite high. In this event, thermal cycling should be expected.

#### Feature Description (continued)

#### 7.3.3 PFM Mode

To minimize quiescent current during light load operation, the LM2775 provides a PFM operation option (selectable via the PFM pin. '1' = PFM allowed, '0' = Fixed frequency). By allowing the charge pump to only switch when the  $V_{OUT}$  voltage decays to a typical 5.05 V, the quiescent current drawn from the power source is minimized. The frequency of pulsed operation is not limited and can drop into the sub-1-kHz range when unloaded. As the load increases, the frequency of pulsing increases.

When PFM mode is disabled, the device operates in a constant frequency mode. In this mode, the quiescent current remains at normal levels even when the load current is decreased. The main advantages of fixed frequency operation include a lower output voltage ripple level due to the constant switching and a predictable switching frequency that stays at 2 MHz which can be important in noise sensitive applications.

### 7.3.4 Output Discharge

The LM2775 provides two different output discharge modes upon entering a shutdown state (EN pin = '0') after running in the on state (EN = '1'). The first mode is high impendance mode (OUTDIS = '0'). In this mode, the output remains high even when the EN pin is driven low. This enables use in applications where the LM2775 output might be tied to a system rail that has another power source connected (USBOTG). When OUTDIS = 0, the output of the LM2775 draws a minimal current from the output supply (1.6  $\mu$ A typical).

In Discharge Mode (OUTDIS pin = '1'), the LM2775 actively pulls down on the output of the device until the output voltage reaches GND. In this mode, the current drawn from the output is approximately  $450 \mu A$ .

#### 7.3.5 Thermal Shutdown

The LM2775 implements a thermal shutdown mechanism to protect the device from damage due to overheating. When the junction temperature rises to 150°C (typical), the part switches into shutdown mode. The LM2775 releases thermal shutdown when the junction temperature of the part is reduced to 130°C (typical).

Thermal shutdown is most often triggered by self-heating, which occurs when there is excessive power dissipation in the device and/or insufficient thermal dissipation. LM2775 power dissipation increases with increased output current and input voltage. When self-heating brings on thermal shutdown, thermal cycling is the typical result. Thermal cycling is the repeating process where the part self-heats, enters thermal shutdown (where internal power dissipation is practically zero), cools, turns on, and then heats up again to the thermal shutdown threshold. Thermal cycling is recognized by a pulsing output voltage and can be stopped be reducing the internal power dissipation (reduce input voltage and/or output current) or the ambient temperature. If thermal cycling occurs under desired operating conditions, thermal dissipation performance must be improved to accommodate the power dissipation of the LM2775. The WSON package is designed to have excellent thermal properties that, when soldered to a PCB designed to aid thermal dissipation, allows the LM2775 to operate under very demanding power dissipation conditions.

#### 7.3.6 Undervoltage Lockout

The LM2775 has an internal comparator that monitors the voltage at VIN and forces the LM2775 into shutdown if the input voltage drops to 2.4 V. If the input voltage rises above 2.6 V, the LM2775 resumes normal operation

Product Folder Links: LM2775

SNVSA57 - MAY 2015 www.ti.com

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown

The LM2775 enters Shutdown Mode if one of the two conditions are met.

- If  $V_{\mbox{\scriptsize IN}}$  is removed or allowed to sag to ground, the device enters shutdown.

- If the EN pin is driven low when V<sub>IN</sub> is within the normal operating range.

In Shutdown, the LM2775 typically draws less than 1 µA from the supply. Depending on the state of the OUTDIS pin, the output is pulled low when entering shutdown (OUTDIS = '1'), or it remains near the final output voltage with the output in a low leakage state (OUTDIS = '0').

#### 7.4.2 Boost Mode

The LM2775 is in Boost Mode if  $V_{\text{IN}}$  is within the normal operating range, and the EN pin is driven high. Depending on the state of the PFM pin, the LM2775 either regulates the output via a PFM burst mode (PFM = '1') or via a constant switching mode (PFM = '0').

Product Folder Links: LM2775

SNVSA57 –MAY 2015 www.ti.com

# TEXAS INSTRUMENTS

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LM2775 can create a 5-V system rail capable of delivering up to 200 mA of output current to the load. The 2-MHz switched capacitor boost allows for the use of small value discrete external components.

### 8.2 Typical Application

Figure 19. Typical LM2775 Configuration

#### 8.2.1 Design Requirements

| DESIGN PARAMETER     | EXAMPLE VALUE                                                 |

|----------------------|---------------------------------------------------------------|

| Input voltage range  | 2.7 V to 5.5 V                                                |

| Output current range | 0 mA to 200 mA (Max. current will depend on V <sub>IN</sub> ) |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Output Current Capability

Submit Documentation Feedback

The LM2775 provides 200 mA of output current when the input voltage is within 3.1 V to 5.5 V.

#### NOTE

Understanding relevant application issues is recommended and a thorough analysis of the application circuit should be performed when using the part outside operating ratings and/or specifications to ensure satisfactory circuit performance in the application. Special care should be paid to power dissipation and thermal effects. These parameters can have a dramatic impact on high-current applications, especially when the input voltage is high. (see the *Power Dissipation* section).

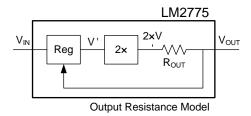

The schematic of Figure 20 is a simplified model of the LM2775 that is useful for evaluating output current capability. The model shows a linear pre-regulation block (Reg), a voltage doubler (2x), and an output resistance ( $R_{OUT}$ ). Output resistance models the output voltage droop that is inherent to switched capacitor converters. The output resistance of the LM2775 is 3.5  $\Omega$  (typical) and is approximately equal to twice the resistance of the four LM2775 switches. When the output voltage is in regulation, the regulator in the model controls the voltage V' to keep the output voltage equal to 5 V  $\pm$  4%. With increased output current, the voltage drop across  $R_{OUT}$

Draduat Folder Linker / M

SNVSA57 - MAY 2015

increases. To prevent droop in output voltage, the voltage drop across the regulator is reduced, V' increases, and V<sub>OUT</sub> remains at 5 V. When the output current increases to the point that there is zero voltage drop across the regulator, V' equals the input voltage, and the output voltage is near the edge of regulation. Additional output current causes the output voltage to fall out of regulation, and the LM2775 operation is similar to a basic openloop doubler. As in a voltage doubler, increase in output current results in output voltage drop proportional to the output resistance of the doubler. The out-of-regulation LM2775 output voltage can be approximated by:

$$V_{OUT} = 2 \times V_{IN} - I_{OUT} \times R_{OUT}$$

(1)

Again, Equation 1 only applies at low input voltage and high output current where the LM2775 is not regulating. See Output Current vs. Output Voltage curves in the Typical Characteristics section for more details.

Figure 20. LM2775 Output Resistance Model

A more complete calculation of output resistance takes into account the effects of switching frequency, flying capacitance, and capacitor equivalent series resistance (ESR) (see Equation 2).

$$R_{OUT} = 2 \cdot R_{SW} + \frac{1}{F_{SW} \times C_1} + 4 \cdot ESR_{C1} + ESR_{COUT}$$

(2)

Switch resistance component (3  $\Omega$  typical) dominates the output resistance equation of the LM2775. With a 2-MHz typical switching frequency, the  $1/(F \times C)$  component of the output resistance contributes only 0.5  $\Omega$  to the total output resistance. Increasing the flying capacitance only provides minimal improvement to the total output current capability of the LM2775. In some applications it may be desirable to reduce the value of the flying capacitor below 1 µF to reduce solution size and/or cost, but this should be done with care so that output resistance does not increase to the point that undesired output voltage droop results. If ceramic capacitors are used, ESR will be a negligible factor in the total output resistance, as the ESR of quality ceramic capacitors is typically much less than 100 m $\Omega$ .

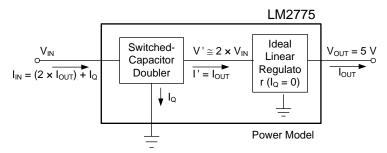

#### 8.2.2.2 Efficiency

Charge-pump efficiency is derived in Equation 3 and Equation 4 (supply current and other losses are neglected for simplicity):

$$I_{IN} = G \times I_{OUT} = (V_{OUT} \times I_{OUT}) \div (V_{IN} \times I_{IN}) = V_{OUT} \div (G \times V_{IN})$$

(3)

If one includes the quiescent current drawn by the LM2775 to operate, the following can be derived:

$$E = \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times (2 \cdot I_{OUT} + I_{Q})}$$

(4)

In Equation 3, G represents the charge pump gain. Efficiency is at its highest as G x V<sub>IN</sub> approaches V<sub>OUT</sub>. For the LM2775 device, G = 2.

#### 8.2.2.3 Power Dissipation

Copyright © 2015, Texas Instruments Incorporated

LM2775 power dissipation (P<sub>D</sub>) is calculated simply by subtracting output power from input power:

$$P_{D} = P_{IN} - P_{OUT} = [V_{IN} \times (2 \times I_{OUT} + I_{O})] - [V_{OUT} \times I_{OUT}]$$

(5)

Power dissipation increases with increased input voltage and output current, up to 1.35 W at the ends of the operating ratings ( $V_{IN} = 5.5 \text{ V}$ ,  $I_{OUT} = 200 \text{ mA}$ ). Internal power dissipation self-heats the device. Dissipating this amount power/heat so the LM2775 does not overheat is a demanding thermal requirement for a small surfacemount package. When soldered to a PCB with layout conducive to power dissipation, the excellent thermal properties of the WSON package enable this power to be dissipated from the LM2775 with little or no derating, even when the circuit is placed in elevated ambient temperatures.

SNVSA57 –MAY 2015 www.ti.com

Figure 21. Power Model

#### 8.2.2.4 Recommended Capacitor Types

The LM2775 requires 3 external capacitors for proper operation. Surface-mount multi-layer ceramic capacitors are recommended. These capacitors are small, inexpensive, and have very low ESR ( $\leq$  15 m $\Omega$  typical). Tantalum capacitors, OS-CON capacitors, and aluminum electrolytic capacitors generally are not recommended for use with the LM2775 due to their high ESR compared to ceramic capacitors.

For most applications, ceramic capacitors with an X7R or X5R temperature characteristic are preferred for use with the LM2775. These capacitors have tight capacitance tolerance (as good as ±10%) and hold their value over temperature (X7R: ±15% over –55°C to 125°C; X5R: ±15% over –55°C to 85°C).

Capacitors with a Y5V or Z5U temperature characteristic are generally not recommended for use with the LM2775. These types of capacitors typically have wide capacitance tolerance (80% to 20%) and vary significantly over temperature (Y5V: 22%, -82% over  $-30^{\circ}$ C to 85°C range; Z5U: 22%, -56% over  $10^{\circ}$ C to 85°C range). Under some conditions, a 1- $\mu$ F-rated Y5V or Z5U capacitor could have a capacitance as low as 0.1  $\mu$ F. Such detrimental deviation is likely to cause Y5V and Z5U capacitors to fail to meet the minimum capacitance requirements of the LM2775.

Net capacitance of a ceramic capacitor decreases with increased DC bias. This degradation can result in lower capacitance than expected on the input and/or output, resulting in higher ripple voltages and currents. Using capacitors at DC-bias voltages significantly below the capacitor voltage rating usually minimizes DC-bias effects. Consult capacitor manufacturers for information on capacitor DC-bias characteristics.

Capacitance characteristics can vary quite dramatically with different application conditions, capacitor types, and capacitor manufacturers. It is strongly recommended that the LM2775 circuit be thoroughly evaluated early in the design-in process with the mass-production capacitors of choice. This helps ensure that any such variability in capacitance does not negatively impact circuit performance.

The voltage rating of the output capacitor should be 10 V or more. All other capacitors should have a voltage rating at or above the maximum input voltage of the application.

#### 8.2.2.5 Output Capacitor and Output Voltage Ripple

The output capacitor in the LM2775 circuit ( $C_{OUT}$ ) directly impacts the magnitude of output voltage ripple. Other prominent factors also affecting output voltage ripple include input voltage, output current, and flying capacitance. One important generalization can be made: increasing (decreasing) the output capacitance results in a proportional decrease (increase) in output voltage ripple. A simple approximation of output ripple is determined by calculating the amount of voltage droop that occurs when the output of the LM2775 is not being driven. This occurs during the charge phase ( $\phi$ 1). During this time, the load is driven solely by the charge on the output capacitor. The magnitude of the ripple thus follows the basic discharge equation for a capacitor (I = C × dV/dt), where discharge time is one-half the switching period, or 0.5/F<sub>SW</sub> (see Equation 6).

$$RIPPLE_{Peak-Peak} = \frac{I_{OUT}}{C_{OUT}} \times \frac{0.5}{F_{SW}}$$

(6)

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

A more thorough and accurate examination of factors that affect ripple requires including effects of phase non-overlap times and output capacitor ESR. In order for the LM2775 to operate properly, the two phases of operation must never coincide. (If this were to happen all switches would be closed simultaneously, shorting input, output, and ground). Thus, non-overlap time is built into the clocks that control the phases. Since the output is not being driven during the non-overlap time, this time should be accounted for in calculating ripple. Actual output capacitor discharge time is approximately 60% of a switching period, or 0.6/F<sub>SW</sub> (see Equation 7).

$$RIPPLE_{Peak-Peak} = \left(\frac{I_{OUT}}{C_{OUT}} \times \frac{0.6}{F_{SW}}\right) + \left(2 \times I_{OUT} \times ESR_{COUT}\right)$$

(7)

#### **NOTE**

In typical high-current applications, a  $10\text{-}\mu\text{F}$ , 10-V low-ESR ceramic output capacitor is recommended. Different output capacitance values can be used to reduce ripple, shrink the solution size, and/or cut the cost of the solution. But changing the output capacitor may also require changing the flying capacitor and/or input capacitor to maintain good overall circuit performance. If a small output capacitor is used and PFM mode is enabled, the output ripple can become large during the transition between PFM mode and constant switching. To prevent toggling, a  $2\text{-}\mu\text{F}$  capacitance is recommended. For example, a  $10\text{-}\mu\text{F}$ , 10-V output capacitor in a 0402 case size will typically only have  $2\text{-}\mu\text{F}$  capacitance when biased to 5-V.

High ESR in the output capacitor increases output voltage ripple. If a ceramic capacitor is used at the output, this is usually not a concern because the ESR of a ceramic capacitor is typically very low and has only a minimal impact on ripple magnitudes. If a different capacitor type with higher ESR is used (tantalum, for example), the ESR could result in high ripple. To eliminate this effect, the net output ESR can be significantly reduced by placing a low-ESR ceramic capacitor in parallel with the primary output capacitor. The low ESR of the ceramic capacitor is in parallel with the higher ESR, resulting in a low net ESR based on the principles of parallel resistance reduction.

#### 8.2.2.6 Input Capacitor and Input Voltage Ripple

The input capacitor  $(C_{IN})$  is a reservoir of charge that aids a quick transfer of charge from the supply to the flying capacitor during the charge phase of operation. The input capacitor helps to keep the input voltage from drooping at the start of the charge phase when the flying capacitor is connected to the input. It also filters noise on the input pin, keeping this noise out of sensitive internal analog circuitry that is biased off the input line.

Much like the relationship between the output capacitance and output voltage ripple, input capacitance has a dominant and first-order effect on input ripple magnitude. Increasing (decreasing) the input capacitance results in a proportional decrease (increase) in input voltage ripple. Input voltage, output current, and flying capacitance also affect input ripple levels to some degree.

In typical high-current applications, a 10-µF low-ESR ceramic capacitor is recommended on the input. Different input capacitance values can be used to reduce ripple, shrink the solution size, and/or cut the cost of the solution. But changing the input capacitor may also require changing the flying capacitor and/or output capacitor to maintain good overall circuit performance.

#### 8.2.2.7 Flying Capacitor

The flying capacitor (C1) transfers charge from the input to the output. Flying capacitance can impact both output current capability and ripple magnitudes. If flying capacitance is too small, the LM2775 may not be able to regulate the output voltage when load currents are high. On the other hand, if the flying capacitance is too large, the flying capacitor might overwhelm the input and output capacitors, resulting in increased input and output ripple.

In typical high-current applications,  $1-\mu F$  low-ESR ceramic capacitors are recommended for the flying capacitor. Polarized capacitors (tantalum, aluminum electrolytic, etc.) must not be used for the flying capacitor, as they could become reverse-biased during LM2775 operation.

Product Folder Links: LM2775

SNVSA57 - MAY 2015 www.ti.com

# TEXAS INSTRUMENTS

#### 8.2.3 Application Curve

Figure 22. Load Regulation

## 8.2.4 USB OTG / Mobile HDMI Power Supply

Figure 23. USB OTG Configuration

#### 8.2.4.1 Design Requirements

| DESIGN PARAMETER     | EXAMPLE VALUE                                                 |  |

|----------------------|---------------------------------------------------------------|--|

| Input voltage range  | 2.7 V to 5.5 V                                                |  |

| Output current range | 0 mA to 200 mA (Max. current will depend on V <sub>IN</sub> ) |  |

#### 8.2.4.2 Detailed Design Procedure

The 5-V output mode is normally used for the USB OTG / Mobile HDMI application. Therefore, the LM2775 can be enabled/disabled by applying a logic signal on only the EN pin while grounding the OUTDIS pin. Depending on the USB/HDMI mode of the application, the LM2775 can be enabled to drive the power bus line (Host), or disabled to put its output in high impedance allowing an external supply to drive the bus line (Slave). In addition to the high impedance-backdrive protection, the output current limit protection is 250 mA (typical), well within the USB OTG and HDMI requirements.

Submit Documentation Feedback

www.ti.com

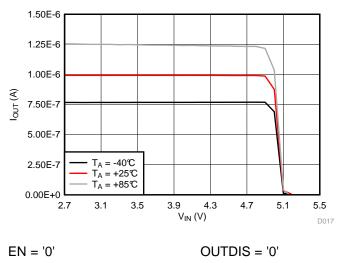

#### 8.2.4.3 Application Curve

Figure 24. Output Leakage Current High Z

## 9 Power Supply Recommendations

The LM2775 is designed to operate from an input voltage supply range between 2.7 V and 5.5 V. This input supply must be well regulated and capable to supply the required input current. If the input supply is located far from the LM2775 additional bulk capacitance may be required in addition to the ceramic bypass capacitors.

Copyright © 2015, Texas Instruments Incorporated

SNVSA57 –MAY 2015 www.ti.com

# TEXAS INSTRUMENTS

## 10 Layout

## 10.1 Layout Guidelines

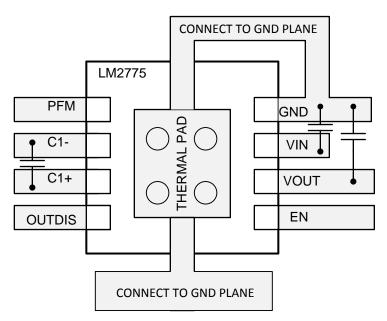

Proper board layout helps to ensure optimal performance of the LM2775 circuit. The following guidelines are recommended:

- Place capacitors as close to the LM2775 as possible, and preferably on the same side of the board as the

device.

- Use short, wide traces to connect the external capacitors to the LM2775 to minimize trace resistance and inductance.

- Use a low resistance connection between ground and the GND pin of the LM2775. Using wide traces and/or

multiple vias to connect GND to a ground plane on the board is most advantageous.

## 10.2 Layout Example

Figure 25. Example LM2775 Layout

Submit Documentation Feedback

SNVSA57 - MAY 2015 www.ti.com

## 11 Device and Documentation Support

#### 11.1 Trademarks

All trademarks are the property of their respective owners.

#### 11.2 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Product Folder Links: LM2775

## PACKAGE OPTION ADDENDUM

8-Jun-2015

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | _       | Pins | _    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| LM2775DSGR       | ACTIVE | WSON         | DSG     | 8    | 3000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 2775           | Samples |

| LM2775DSGT       | ACTIVE | WSON         | DSG     | 8    | 250  | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 2775           | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

8-Jun-2015

| n no event shall TI's liabili | ty arising out of such information | exceed the total purchase | price of the TI part(s) | at issue in this document sold by | TI to Customer on an annual basis. |

|-------------------------------|------------------------------------|---------------------------|-------------------------|-----------------------------------|------------------------------------|

|                               |                                    |                           |                         |                                   |                                    |

PACKAGE MATERIALS INFORMATION

www.ti.com 22-Sep-2019

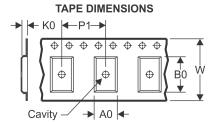

## TAPE AND REEL INFORMATION

| Α0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

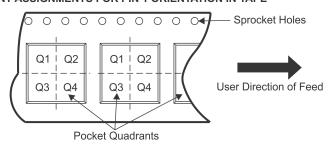

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM2775DSGR | WSON            | DSG                | 8 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| LM2775DSGT | WSON            | DSG                | 8 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

www.ti.com 22-Sep-2019

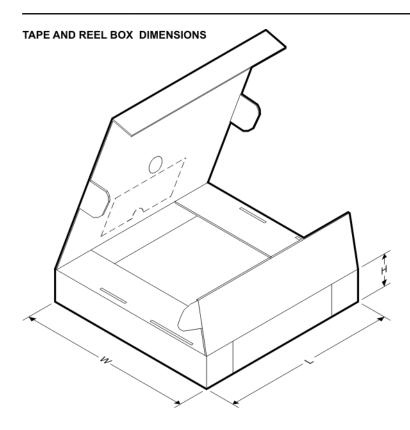

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM2775DSGR | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| LM2775DSGT | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

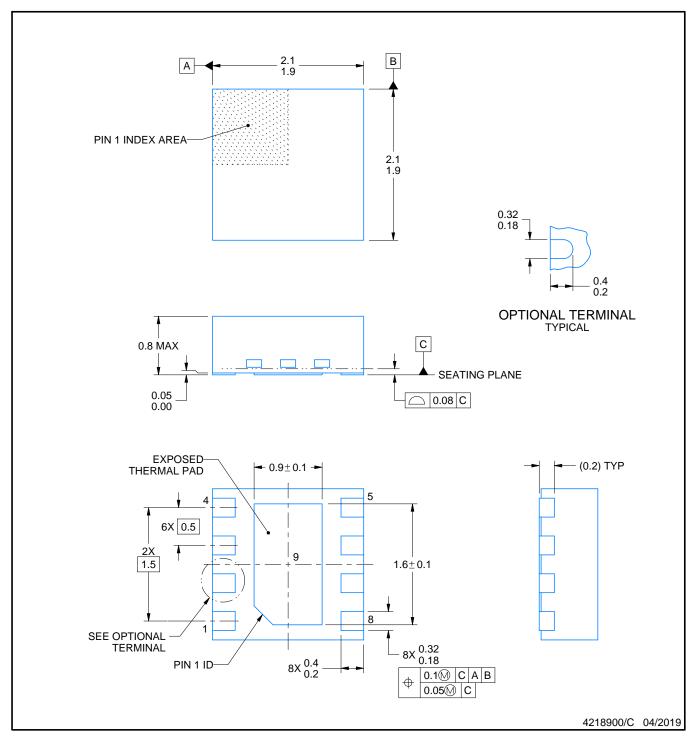

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

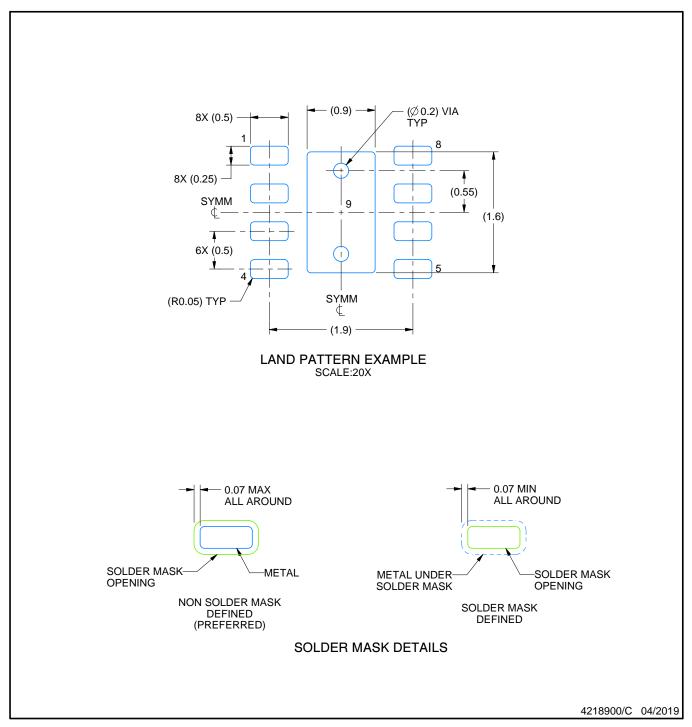

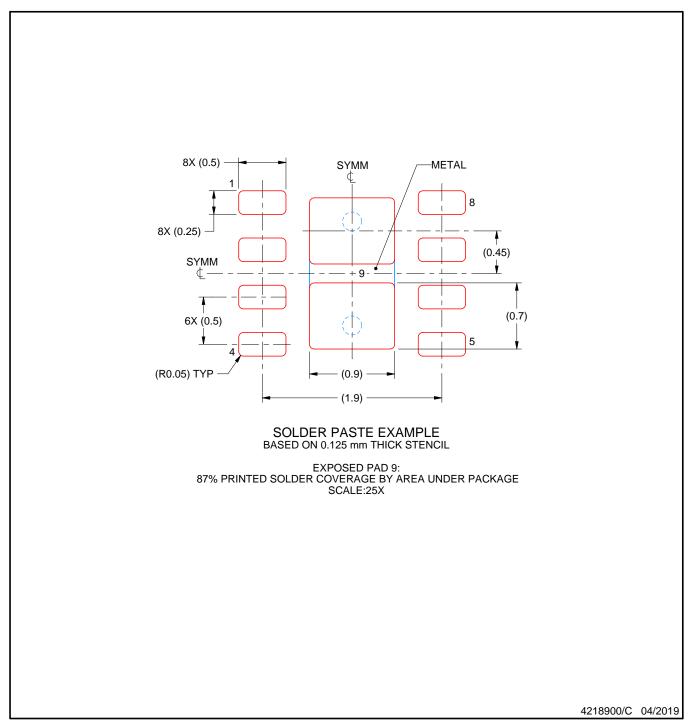

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated