## **Current-Mode PWM Controllers**

#### **Features**

- 8-V to 30-V Operation

- Low Start-up Current: <1mA</p>

- 5.1-V Reference Trimmed to 1%

- Current Mode Operation up to 500KHz

- Automatic Feed-forward Compensation

- Under-voltage Lockout With Hysteresis

- Latching PWM for Cycle-by-Cycle Current Limit

- Double-Pulse Suppression

- High Current Output Driver

- Optimized for off-line and DC-to-DC

Converters

- Available Packaging: SOP8/TSSOP8/DIP8

## **Applications**

- Solar Inverters

- Switching Regulators of Any Polarity

- Motor Control

- Battery Chargers

- DC/DC Power Supplies

Rev1.0 Copyright@2018 Cosine Nanoelectronics Inc. All rights reserved The information provided here is believed to be accurate and reliable. Cosine Nanoelectronics assumes no reliability for inaccuracies and omissions. Specifications described and contained here are subjected to change without notice on the purpose of improving the design and performance. All of this information described herein should not be implied or granted for any third party.

#### **General Description**

The COS384x series of controllers are peak current mode pulse width modulators. They are designed to offer improved performance and lowered external parts count when used in designing off-line or DC-to-DC switching power supplies. The internally implemented circuits include an under-voltage lockout (UVLO), featuring a start-up current of less than 1mA, and a precision reference trimmed for accuracy at the error amplifier input. Other internal circuits include logic to ensure latched operation, a pulse-width modulation (PWM) comparator that also provides current-limit control, and a totem-pole output stage that is designed to source or sink high-peak current. The output stage, suitable for driving N-channel MOSFETs, is low when it is in the off state.

The differences between COS384x family member are the under-voltage lockout thresholds and the maximum duty cycle ranges.

| Model   | UVLO<br>Threshold       | Max. Duty<br>Cycle |

|---------|-------------------------|--------------------|

| COS3842 | 16V(Von)<br>10V(Voff)   | 100%               |

| COS3843 | 8.4V(Von)<br>7.6V(Voff) | 100%               |

| COS3844 | 16V(Von)<br>10V(Voff)   | 50%                |

| COS3845 | 8.4V(Von)<br>7.6V(Voff) | 50%                |

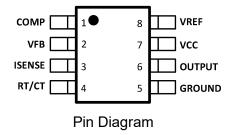

# 1. Pin Configuration and Block Diagram

Figure 1. Pin Diagram

Table 1. Pin Description

| Pin | Name                           | I/O | Description                                                                                                                                                                                                                                                                                                         |

|-----|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | СОМР                           | 0   | Output of the error amplifier for compensation. Connect external compensation components to this pin to modify the error amplifier output. The error amplifier is internally current limited so the users can command zero duty cycle by externally forcing COMP to GROUND.                                         |

| 2   | V <sub>FB</sub>                | I   | Inverting input to the error amplifier. It is normally connected to the switching power supply output through a resistor divider.                                                                                                                                                                                   |

| 3   | Isense                         | I   | A voltage proportional to inductor current is connected to this input. The PWM uses his information to terminate the output switch conduction. A voltage ramp can be applied to this pin to run the device with a voltage-mode control configuration.                                                               |

| 4   | R <sub>T</sub> /C <sub>T</sub> | I/O | The oscillator frequency and maximum output duty cycle are programmed by connecting resistor $R_T$ to $V_{REF}$ and capacitor $C_T$ to ground. Operation up to 1MHz is possible.                                                                                                                                    |

| 5   | GROUND                         | Р   | Ground return pin. It functions as both power ground and analog ground.                                                                                                                                                                                                                                             |

| 6   | OUTPUT                         | 0   | Output of the on-chip drive stage. It directly drives the gate of a power MOSFET. Peak current up to 1A are sourced and sunk by this pin. Output is actively held low when $V_{\text{CC}}$ is below the turnon threshold.                                                                                           |

| 7   | Vcc                            | Р   | Power supply pin for the control IC. This pin should be bypassed with a 0.1- $\mu$ F ceramic low ESL capacitor with minimal trace lengths. An additional bypass capacitor at least 10 times greater than the gate capacitance of the main switching MOSFET used in the design is also required on V <sub>CC</sub> . |

| 8   | $V_{REF}$                      | 0   | 5V reference. It provides charging current for capacitor $C_T$ through resistor $R_T$ . For stability, the reference should be bypassed with a 0.1- $\mu$ F ceramic low ESL capacitor and minimal trace length to the ground plane.                                                                                 |

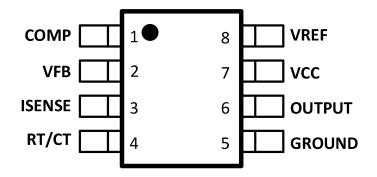

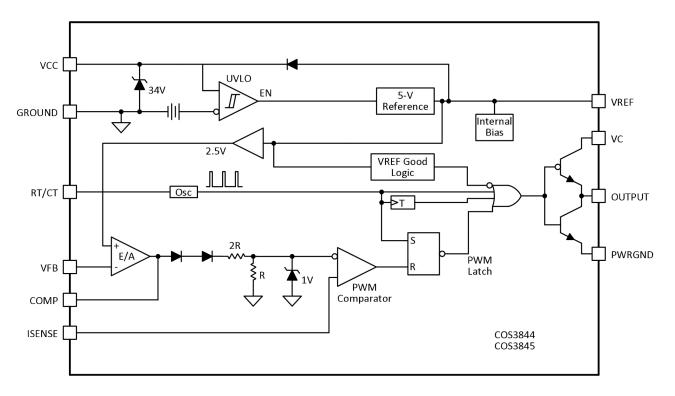

Figure 2. COS3842 and COS3843 Block Diagram (Note: with duty cycles approaching 100%)

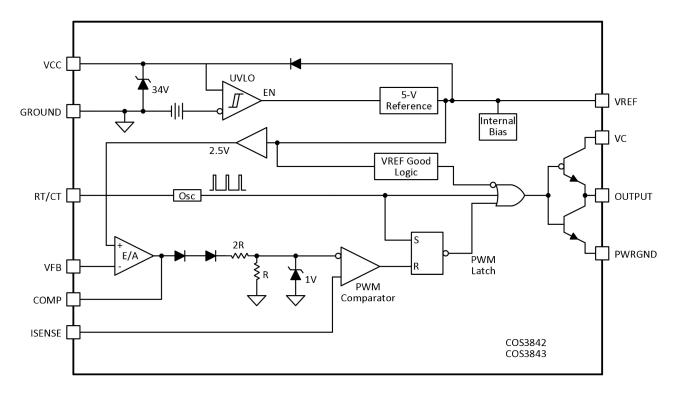

Figure 3. COS3844 and COS3845 Block Diagram (Note: with duty cycles approaching 50%)

## 2. Ordering Information

| Model   | Order Number | Package | Package Option      | Marking Information |

|---------|--------------|---------|---------------------|---------------------|

| COS3842 | COS3842BD    | SOP-8   | Tape and Reel, 3000 | COS3842BD           |

| CO53642 | COS3842BN    | DIP-8   | Tube, 50            | COS3842BN           |

| COS3843 | COS3843BD    | SOP-8   | Tape and Reel, 3000 | COS3843BD           |

| CO53643 | COS3843BN    | DIP-8   | Tube, 50            | COS3843BN           |

| COS3844 | COS3844BD    | SOP-8   | Tape and Reel, 3000 | COS3844BD           |

| CO33644 | COS3844BN    | DIP-8   | Tube, 50            | COS3844BN           |

| COS3845 | COS3845BD    | SOP-8   | Tape and Reel, 3000 | COS3845BD           |

| 0033645 | COS3845BN    | DIP-8   | Tube, 50            | COS3845BN           |

## 3. Product Specification

#### 3.1 Absolute Maximum Ratings (1)

| Parameter                           | Sym.                                 | Min  | Max  | Unit |

|-------------------------------------|--------------------------------------|------|------|------|

| Supply Voltage                      | V <sub>CC</sub>                      |      | 30   | V    |

| Analog Inputs                       | V <sub>FB</sub> , I <sub>SENSE</sub> | -0.3 | 6    | V    |

| Output Current, Source or Sink      | Io                                   |      | ±1   | А    |

| Error Amplifier Output Sink Current | I <sub>COMP</sub>                    |      | 10   | mA   |

| Operating Junction Temperature      | TJ                                   | -40  | +125 | °C   |

| Storage Temperature                 | Ts                                   | -55  | +150 | °C   |

| Lead Temperature (soldering 10s)    | TL                                   |      | +300 | °C   |

<sup>(1)</sup> Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

#### 3.2 Thermal Data

| Parameter                                                         | Rating                  | Unit |

|-------------------------------------------------------------------|-------------------------|------|

| Package Thermal Resistance, R <sub>θJA</sub> (Juntion-to-ambient) | 150 (SOP8)<br>90 (DIP8) | °C/W |

# 3.3 Recommended Operating Conditions

| Parameter                          | Min. | Тур. | Max. | Unit |

|------------------------------------|------|------|------|------|

| Vcc Supply Voltage                 | -    | -    | 30   | V    |

| V <sub>FB</sub> Input Voltage      | -    | -    | 2.5  | V    |

| I <sub>SENSE</sub> Input Voltage   | -    | -    | 1    | V    |

| Sink/Source Load Current (average) |      | -    | 200  | mA   |

| Reference Load Current             | 0    | -    | 20   | mA   |

| Oscillator Frequency Range         | -    | 100  | 500  | kHz  |

| Operating Junction Temperature     | -40  | -    | +125 | °C   |

### 3.4 Electrical Characteristics

(Typical values are tested at  $V_{\text{CC}}$ =20V,  $T_{\text{A}}$ =25 °C, unless otherwise specified.)

| Parameter                    | Sym.                | Conditions                                        | Min. | Тур. | Max. | Unit |

|------------------------------|---------------------|---------------------------------------------------|------|------|------|------|

| POWER SUPPLY                 | POWER SUPPLY        |                                                   |      |      |      |      |

| Supply Voltage               | Vcc                 |                                                   | 7.6  | -    | 30   | V    |

| Operating Supply Current     |                     | V <sub>FB</sub> = V <sub>ISENSE</sub> = 0 V       | -    | 12   | 17   | mA   |

| Start-up Current             | - I <sub>S</sub>    |                                                   |      | 0.1  | 0.3  | mA   |

| REFERENCE                    |                     |                                                   |      |      |      |      |

| Output Voltage               | V <sub>REF</sub>    |                                                   | 4.95 | 5.0  | 5.05 | V    |

| Line Regulation              | $\Delta V_{REF}$    | V <sub>IN</sub> = 8 V to 30 V                     | -    | 10   | 20   | mV   |

| Load Regulation              | $\Delta V_{REF}$    | I <sub>L</sub> = 0 to 20 mA                       | -    | 20   | 50   | mV   |

| Temp. Stability              | $\Delta V_{REF}$    | Over operating range                              |      | 20   | 50   | mV   |

| Total Output Variation       | V <sub>REF</sub>    | Line, Load, and Temperature                       | 4.9  | -    | 5.1  | V    |

| Short Circuit Output Current | Isc                 | V <sub>REF</sub> =0                               | 30   | 100  | 180  | mA   |

| OSCILLATOR                   | •                   |                                                   |      | •    |      |      |

| Frequency                    | fosc                | $R_T = 10 \text{ k}\Omega, C_T = 3.3 \mu\text{F}$ | 47   | 52   | 57   | kHz  |

| Voltage Stability            | Δf/ΔV <sub>IN</sub> | V <sub>IN</sub> = 12 V to 25 V                    | -    | 0.2  | 1    | %    |

| Temperature Stability        | Δf/ΔΤ               | V <sub>IN</sub> = 12 V to 25 V                    | -    | 5    | -    | %    |

# COS3842, 3843, 3844, 3845

|                              |                     | 00000                                                                        | ,    | , , , | , •  | <u> </u> |

|------------------------------|---------------------|------------------------------------------------------------------------------|------|-------|------|----------|

| Clock Amplitude              | V <sub>RT/CT</sub>  |                                                                              | -    | 1.6   | -    | V        |

| ERROR AMPLIFIER              |                     |                                                                              |      |       |      |          |

| Input Voltage                | V <sub>FB</sub>     |                                                                              | 2.42 | 2.5   | 2.58 | V        |

| Input Bias Current           | lΒ                  |                                                                              | -    | 0.1   | 2    | μА       |

| Open Loop Voltage Gain       | G <sub>VOL</sub>    | 2 ≤VCOMP ≤ 4 V                                                               | 65   | 90    | -    | dB       |

| Gain-Bandwidth Product       | GBP                 | A <sub>V</sub> = 0 dB                                                        | 0.7  | 1     | -    | MHz      |

| Power Supply Rejection Ratio | PSRR₁               | V <sub>IN</sub> = 12V to 25V                                                 | 60   | 70    | -    | dB       |

| COMP Sink Current            | I <sub>SK</sub>     | V <sub>FB</sub> = 2.7 V, V <sub>COMP</sub> =1.1V                             | 2    | 12    | -    | mA       |

| COMP Source Current          | I <sub>SRC</sub>    | V <sub>FB</sub> = 2.3 V, V <sub>COMP</sub> =5V                               | -0.5 | -1    | -    | mA       |

| Low-level Output Voltage     | V <sub>OL</sub>     | $V_{FB}$ = 2.7 V;<br>R <sub>L</sub> = 15-k $\Omega$ COMP to V <sub>REF</sub> |      | 0.8   | 1.1  | V        |

| High-level Output Voltage    | V <sub>ОН</sub>     | $V_{FB}$ = 2.3 V;<br>R <sub>L</sub> = 15-k $\Omega$ COMP to Ground           | 5    | 6.2   |      | V        |

| PWM COMPARATOR               |                     |                                                                              |      |       |      |          |

| Gain                         | G <sub>COMP</sub>   | $G = \Delta V_{COMP}/\Delta V_{ISENSE},$ $0 \ V \le V_{ISENSE} \le 0.8 \ V$  | 2.85 | 3     | 3.15 | V/V      |

| Maximum Input Signal         | V <sub>ISENSE</sub> |                                                                              | 0.9  | 1     | 1.1  | V        |

| Input Bias Current           | IISENSE             |                                                                              | -    | -2    | -10  | μА       |

| Power Supply Rejection Ratio | PSRR <sub>2</sub>   | V <sub>CC</sub> = 12V to 25V                                                 | -    | 70    | -    | dB       |

| Delay to Output              | t <sub>DLY</sub>    | V <sub>ISENSE</sub> stepped from 0 to 2 V                                    |      | 150   | 300  | ns       |

| OUTPUT DRIVER                |                     |                                                                              |      |       |      |          |

| Love lovel Output Valtage    | V <sub>OLI</sub>    | I <sub>SINK</sub> = 20 mA                                                    | -    | 0.2   | 0.4  | V        |

| Low-level Output Voltage     | VolII               | I <sub>SINK</sub> = 200 mA                                                   | -    | 1.6   | 2.2  | V        |

| High-level Output Voltage    | V <sub>ОН І</sub>   | I <sub>SOURCE</sub> = 20 mA                                                  | 18   | 19    | -    | V        |

| riigii-ievei Output voitage  | V <sub>OH II</sub>  | I <sub>SOURCE</sub> = 200 mA                                                 | 17   | 18    | -    | V        |

| Rise Time                    | t <sub>R</sub>      | C <sub>L</sub> =1nF                                                          | -    | 50    | 150  | ns       |

| Fall Time                    | t <sub>F</sub>      | C <sub>L</sub> =1nF                                                          | -    | 50    | 150  | ns       |

|                                       |                  |              | -    | -   |      |   |

|---------------------------------------|------------------|--------------|------|-----|------|---|

| UNDER-VOLTAGE LOCKOUT (UVLO)          |                  |              |      |     |      |   |

|                                       | 1.0.4            | COS3842/3844 | 14.5 | 16  | 17.5 | V |

| UVLO Enable Threshold                 | UVLON            | COS3843/3845 | 7.8  | 8.4 | 9.0  | V |

| LIVII O Off Three should              | 111/4            | COS3842/3844 | 8.5  | 10  | 11.5 | V |

| UVLO Off Threshold UVL <sub>OFF</sub> |                  | COS3843/3845 | 7.0  | 7.6 | 8.2  | V |

| PWM DUTY CYCLE                        |                  |              |      |     |      |   |

| Maximum Duty Cycle D <sub>MAX</sub>   |                  | COS3842/3843 | 94   | 96  | 100  | % |

|                                       |                  | COS3844/3845 | 47   | 48  | 50   | % |

| Minimum Duty Cycle                    | D <sub>MIN</sub> |              |      |     | 0    | % |

## 4. Application Information

#### 4.0 Overview

The COS384x series of pulse width modulator (PWM) integrated circuits provide the features necessary to implement AC-DC or DC-to-DC fixed-frequency current mode control schemes with a minimum number of external components. Protection circuitry includes undervoltage lockout (UVLO) and current limiting. Internally implemented circuits include a start-up current of less than 1mA, a precision reference trimmed for accuracy at the error amplifier input, logic to ensure latched operation, a pulse-width modulation (PWM) comparator that also provides current-limit control, and a totem-pole output stage designed to source and sink high-peak current. The output stage, suitable for driving N-channel MOSFETs, is low when it is in the off-state.

The differences between members of COS384x series are the UVLO thresholds and maximum duty-cycle as shown in Table 2.

Table 2. Device Information

| Model   | UVLO Threshold          | Max. Duty Cycle |

|---------|-------------------------|-----------------|

| COS3842 | 16V(Von)<br>10V(Voff)   | 100%            |

| COS3843 | 8.4V(Von)<br>7.6V(Voff) | 100%            |

| COS3844 | 16V(Von)<br>10V(Voff)   | 50%             |

| COS3845 | 8.4V(Von)<br>7.6V(Voff) | 50%             |

Typical UVLO thresholds of 16V(ON) and 10V(OFF) on the COS3842 and COS3844 devices make them ideally suited to off-line AC-DC applications. The corresponding typical thresholds for the COS3843 and COS3845 devices are 8.4V(ON) and 7.6V(OFF), making them ideal for use with regulated input voltages used in DC-DC applications. The COS3842 and COS3843 devices operate at duty cycles approaching 100%. The COS3844 and COS3845 have a duty-cycle range of 0% to 50% by the addition of an internal toggle flip-flop, which blanks the output off every other clock cycle.

The COS384x uses an external resistor to set the charging current for the external capacitor, which determines the oscillator frequency as following equation:

$$f_{OSC} = 1.72/(R_{RT} \times C_{CT}) \tag{1}$$

The recommended range of timing resistor values is between 5 k $\Omega$  and 100 k $\Omega$ ; the recommended range of timing capacitor values is between 1 nF and 100 nF.

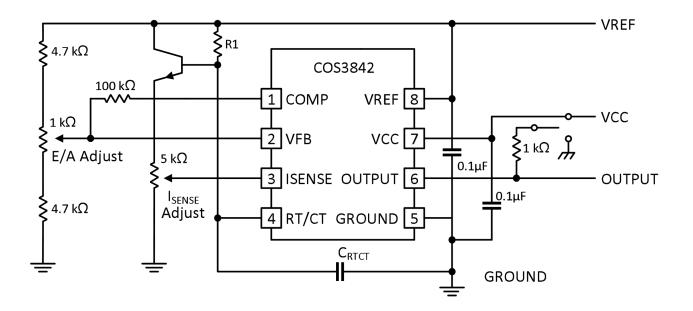

#### 4.1 Open-Loop Test Fixture

An open-loop laboratory test fixture (Figure 4) is used to demonstrate the setup and use of the COS3842 devices and their internal circuitry. The transistor and  $5-k\Omega$  potentiometer sample the oscillator waveform and apply an adjustable ramp to the I<sub>SENSE</sub> terminals. High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypass capacitors should be connected close to pin 5 in a single point ground.

Figure 4. Open-Loop Laboratory Test Fixture

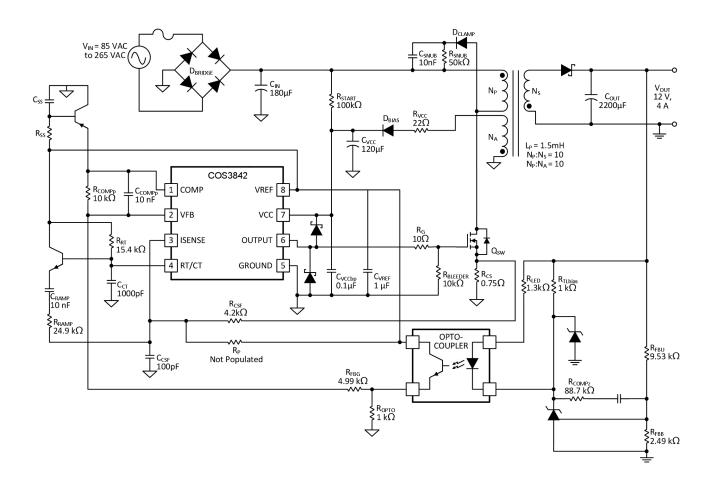

#### 4.2 Typical Application

A typical application for the COS3842 in an off-line flyback converter is shown in Figure 5. It is capable of providing 48W at 12V output voltage from a universal AC input. The design uses peak primary current control in a continuous current mode PWM converter.

Figure 5. An Off-Line Flyback Converter Scheme

# 5. Package Information

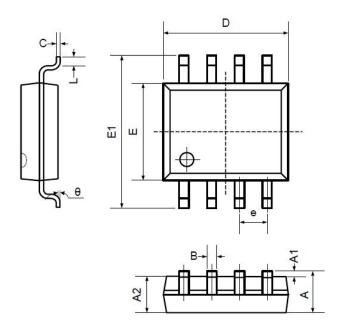

# 5.1 SOP8 (Package Outline Dimensions)

| Symbol |          | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|----------|------------------|-------------------------|-------|--|

|        | Min      | Max              | Min                     | Max   |  |

| Α      | 1.350    | 1.750            | 0.053                   | 0.069 |  |

| A1     | 0.100    | 0.250            | 0.004                   | 0.010 |  |

| A2     | 1.350    | 1.550            | 0.053                   | 0.061 |  |

| В      | 0.330    | 0.510            | 0.013                   | 0.020 |  |

| С      | 0.190    | 0.250            | 0.007                   | 0.010 |  |

| D      | 4.780    | 5.000            | 0.188                   | 0.197 |  |

| E      | 3.800    | 4.000            | 0.150                   | 0.157 |  |

| E1     | 5.800    | 6.300            | 0.228                   | 0.248 |  |

| е      | 1.270TYP |                  | 0.050                   | TYP   |  |

| L      | 0.400    | 1.270            | 0.016                   | 0.050 |  |

| θ      | 0°       | 8°               | 0°                      | 8°    |  |

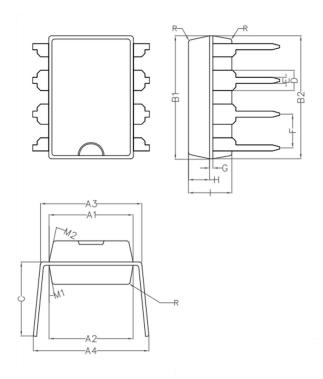

# **5.2 DIP8 (Package Outline Dimensions)**

| Symbol | Min  | Non  | Max  |

|--------|------|------|------|

| A1     | 6.28 | 6.33 | 6.38 |

| A2     | 6.33 | 6.38 | 6.43 |

| A3     | 7.52 | 7.62 | 7.72 |

| A4     | 7.80 | 8.40 | 9.00 |

| B1     | 9.15 | 9.20 | 9.25 |

| B2     | 9.20 | 9.25 | 9.30 |

| С      |      | 5.57 |      |

| D      |      | 1.52 |      |

| E      | 0.43 | 0.45 | 0.47 |

| F      |      | 2.54 |      |

| G      |      | 0.25 |      |

| Н      | 1.54 | 1.59 | 1.64 |

| 1      | 3.22 | 3.27 | 3.32 |

| R      |      | 0.20 |      |

| M1     | 9°   | 10°  | 11°  |

| M2     | 11°  | 12°  | 13°  |