# 3.3 V USB 3.2 10 Gbps Quad Channel / Dual Port Linear Redriver

# NB7NPQ1404E2M

### Description

The NB7NPQ1404E2M is a high performance 2-Port linear redriver designed for USB 3.2 applications that supports both 5 Gbps and 10 Gbps data rates. Signal integrity degrades from PCB traces, transmission cables, and inter-symbol interference (ISI). The NB7NPQ1404E2M compensates for these losses by engaging varying levels of equalization at the input receiver, and flat gain amplification on the output transmitter.

The NB7NPQ1404E2M offers programmable equalization and flat gain for each independent channel to optimize performance over various physical mediums.

The NB7NPQ1404E2M contains an automatic receiver detect function which will determine whether the output is active. The receiver detection loop will be active if the corresponding channel's signal detector is idle for a period of time. The channel will then move to Unplug Mode if a load is not detected, or it will return to Low Power Mode (Slumber mode) due to inactivity.

The NB7NPQ1404E2M comes in a 2.5 x 4.5 x 0.55 mm UQFN34 package and is specified to operate across the entire industrial temperature range,  $-40^{\circ}$ C to 85°C.

# Features

- 3.3 V  $\pm$  0.3 V Power Supply

- 5 Gbps & 10 Gbps Serial Link with Linear Amplifier

- Device Supports USB 3.2 Gen2 and Gen1

- Automatic Receiver Detection

- Supports USB-IF VCM Requirement

- Integrated Input and Output Termination

- Pin Adjustable Receiver Equalization and Flat Gain

- 100 Ω Differential CML I/O's

- Auto Slumber Mode for Adaptive Power Management

- Hot-Plug Capable

- ESD Protection ±4 kV HBM

- Operating Temperature Range Industrial: -40°C to +85°C

- Package: UQFN34, 2.5 x 4.5 x 0.55 mm

- This is a Pb-Free Device

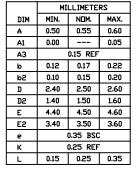

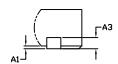

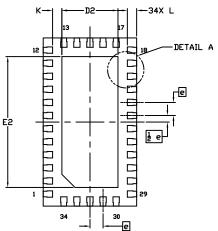

### MARKING DIAGRAM

### UQFN34 CASE 523BR

NB7N404E = Specific Device Code

= Assembly Location

L = Wafer Lot Y = Year W = Work Week

### ORDERING INFORMATION

| Device             | Package             | Shipping <sup>†</sup> |

|--------------------|---------------------|-----------------------|

| NB7NPQ1404E2MMUTWG | UQFN34<br>(Pb-Free) |                       |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### Typical Applications

- USB3.2 Type–A and Type–C Signal Routing

- Mobile Phone and Tablet

- Computer, Laptop and Notebook

- External Storage Device

- Docking Station and Dongle

- Active Cable, Back Planes

1

• Gaming Console, Smart T.V.

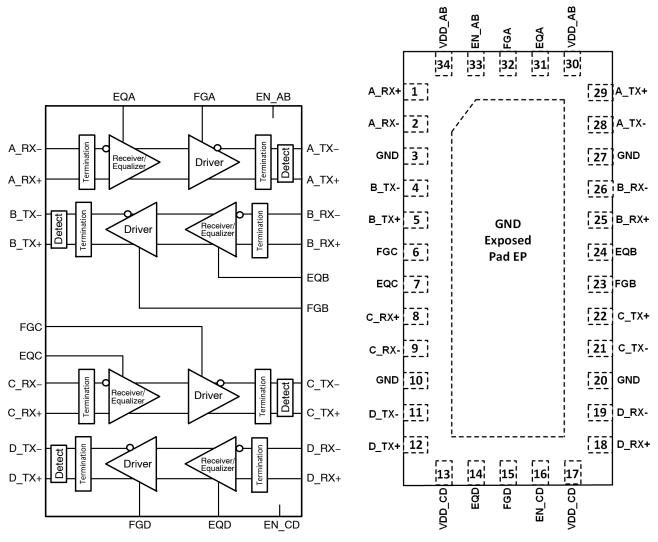

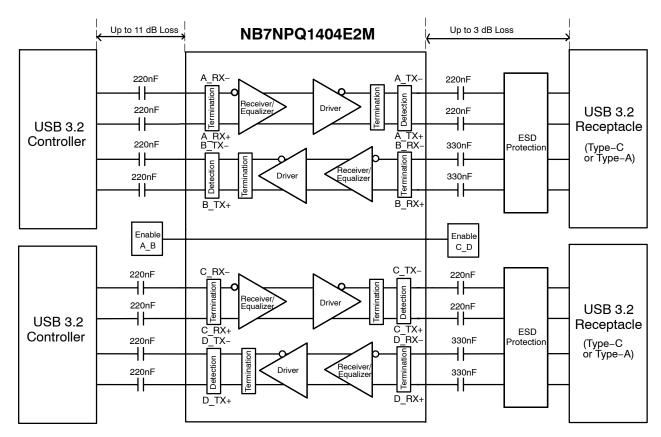

Figure 1. Logic Diagram of NB7NPQ1404E2M

Figure 2. UQFN34 Package Pinout (Top View)

# **Table 1. PIN DESCRIPTION**

| Pin Number    | Pin Name | Туре   | Description                                                                                                                                                                                                                   |

|---------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | A_RX+    | INPUT  | Channel A Differential CML input pair for 5 / 10 Gbps USB signals. Must be externally AC-coupled in                                                                                                                           |

| 2             | A_RX-    |        | system. UFP/DFP transmitter should provide this capacitor.                                                                                                                                                                    |

| 3, 10, 10, 27 | GND      | GND    | Reference Ground. GND pins must be externally connected to power supply ground to guarantee proper operation.                                                                                                                 |

| 4             | B_TX-    | OUTPUT | Channel B Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled in system.                                                                                                                           |

| 5             | B_TX+    |        |                                                                                                                                                                                                                               |

| 6             | FGC      | INPUT  | DC flat gain for channel C. 4-level input pin. Internal 100 k $\Omega$ pull-up and 200 k $\Omega$ pull-down.                                                                                                                  |

| 7             | EQC      | INPUT  | EQ select for channel C. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                     |

| 8             | C_RX+    | INPUT  | Channel C Differential CML input pair for 5 / 10 Gbps USB signals. Must be externally AC-coupled in                                                                                                                           |

| 9             | C_RX-    |        | system. UFP/DFP transmitter should provide this capacitor.                                                                                                                                                                    |

| 11            | D_TX-    | OUTPUT | Channel D Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled in system.                                                                                                                           |

| 12            | D_TX+    |        |                                                                                                                                                                                                                               |

| 13, 17        | VDD_CD   | POWER  | 3.3 V power supply for Channel C and D. VDD pins must be externally connected to power supply.                                                                                                                                |

| 14            | EQD      | INPUT  | EQ select for channel D. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                     |

| 15            | FGD      | INPUT  | DC flat gain for channel D. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                  |

| 16            | EN_CD    | INPUT  | Channel CD Enable. Internal 300 k $\Omega$ pull-up. High-Channel is in normal operation. Low-Channel is in power down mode.                                                                                                   |

| 18            | D_RX+    | INPUT  | Channel D Differential CML input pair for 5 / 10 Gbps USB signals. Must be externally AC-coupled in                                                                                                                           |

| 19            | D_RX-    |        | system. UFP/DFP transmitter should provide this capacitor.                                                                                                                                                                    |

| 21            | C_TX-    | OUTPUT | Channel C Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled in system.                                                                                                                           |

| 22            | C_TX+    |        |                                                                                                                                                                                                                               |

| 23            | FGB      | INPUT  | DC flat gain for channel B. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                  |

| 24            | EQB      | INPUT  | EQ select for channel B. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                     |

| 25            | B_RX+    | INPUT  | Channel B Differential CML input pair for 5 / 10 Gbps USB signals. Must be externally AC-coupled in                                                                                                                           |

| 26            | B_ RX-   |        | system. UFP/DFP transmitter should provide this capacitor.                                                                                                                                                                    |

| 28            | A_TX-    | OUTPUT | Channel A Differential output for 5 / 10 Gbps USB signals. Must be externally AC-coupled in system.                                                                                                                           |

| 29            | A_TX+    |        |                                                                                                                                                                                                                               |

| 30, 34        | VDD_AB   | POWER  | 3.3 V power supply for Channel A and B. VDD pins must be externally connected to power supply.                                                                                                                                |

| 31            | EQA      | INPUT  | EQ select for channel A. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                     |

| 32            | FGA      | INPUT  | DC flat gain for channel A. 4–level input pin. Internal 100 k $\Omega$ pull–up and 200 k $\Omega$ pull–down.                                                                                                                  |

| 33            | EN_AB    | INPUT  | Channel AB Enable. Internal 300 k $\Omega$ pull-up. High-Channel is in normal operation. Low-Channel is in power down mode.                                                                                                   |

| EP            | GND      | GND    | Exposed Pad (EP). EP on the package bottom is thermally connected to the die for improved heat transfer out of the package. The exposed pad is electrically connected to the die and must be soldered to GND on the PC board. |

### **Power Management**

The NB7NPQ1404E2M has an adaptive power management feature in order to minimize power consumption. When the receiver signal detector is idle, the corresponding channel will change to low power slumber mode. Accordingly, both channels will move to low power slumber mode individually.

While in the low power slumber mode, the receiver signal detector will continue to monitor the input channel. If a channel is in low power slumber mode, the receiver detection loop will be active again. If a load is not detected, then the channel will move to Device Unplug Mode and continuously monitor for the load. When a load is detected, the channel will return to Low Power Slumber Mode and receiver detection will be active again per 6 ms.

**Table 2. OPERATING MODES**

| Mode                      | R <sub>IN</sub>      | R <sub>OUT</sub>     |

|---------------------------|----------------------|----------------------|

| PD                        | 67 k $\Omega$ to GND | High-Z               |

| Unplug Mode               | High-Z               | 40 k $\Omega$ to VDD |

| Low Power<br>Slumber Mode | 50 $\Omega$ to VDD   | 40 kΩ to VDD         |

| Active                    | 50 $\Omega$ to VDD   | 50 $\Omega$ to VDD   |

### **Table 3. EQUALIZATION SETTING**

EQ A/B/C/D are the selection pins for the equalization.

| EQA/B/C/D           | Equalizer Setting (dB) |               |  |  |  |

|---------------------|------------------------|---------------|--|--|--|

|                     | @2.5 GHz               | @5 GHz        |  |  |  |

| L (Tie 0-Ω to GND)  | 5.0                    | 9.9           |  |  |  |

| R (Tie Rext to GND) | 2.7                    | 6.9           |  |  |  |

| F (Leave Open)      | 4.0                    | 8.2 (Default) |  |  |  |

| H (Tie 0-Ω to VDD)  | ) 6.5 12.1             |               |  |  |  |

### **Table 4. FLAT GAIN SETTING**

FGA/B/C/D are the selection pins for the DC gain.

| FGA/B/C/D           | Flat Gain Settings (dB) |

|---------------------|-------------------------|

| L (Tie 0 Ω to GND)  | -1.2                    |

| R (Tie Rext to GND) | -0.2                    |

| F (Leave Open)      | +0.8 (Default)          |

| H (Tie 0 Ω to VDD)  | +1.8                    |

### **Table 5. CHANNEL ENABLE SETTING**

EN\_AB / EN\_CD are the channel enable pins for channels A&B and C&D respectively.

| EN | Channel Enable Setting |

|----|------------------------|

| 0  | Disabled               |

| 1  | Enabled (Default)      |

**Table 6. ATTRIBUTES**

| Parameter                                      |                        |                      |

|------------------------------------------------|------------------------|----------------------|

| ESD Protection                                 | ± 4 kV<br>> 1.5 kV     |                      |

| Moisture Sensitivity, Indefinite Time Out of D | Level 1                |                      |

| Flammability Rating                            | Oxygen Index: 28 to 34 | UL 94 V-O @ 0.125 in |

| Transistor Count                               | 81034                  |                      |

| Meets or exceeds JEDEC Spec EIA/JESD78         |                        |                      |

<sup>1.</sup> For additional information, see Application Note AND8003/D.

Table 7. ABSOLUTE MAXIMUM RATINGS Over operating free-air temperature range (unless otherwise noted)

| Parameter                                                                | Description      | Min  | Max                   | Unit |

|--------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply Voltage (Note 2)                                                  | VDD              | -0.5 | 4.6                   | V    |

| Voltage range at any input or output terminal                            | Differential I/O | -0.5 | V <sub>DD</sub> + 0.5 | V    |

|                                                                          | LVCMOS inputs    | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Output Current                                                           |                  | -25  | +25                   | mA   |

| Power Dissipation, Continuous                                            |                  |      | 1.2                   | W    |

| Storage Temperature Range, T <sub>SG</sub>                               |                  | -65  | 150                   | °C   |

| Maximum Junction Temperature, T <sub>J</sub>                             |                  |      | 125                   | °C   |

| Junction-to-Ambient Thermal Resistance @ 500 lfm, $\theta_{JA}$ (Note 3) |                  |      | 34                    | °C/W |

| Wave Solder, Pb-Free, T <sub>SOL</sub>                                   |                  |      | 265                   | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>2.</sup> All voltage values are with respect to the GND terminals.

<sup>3.</sup> JEDEC standard multilayer board – 2S2P (2 signal, 2 power).

Table 8. RECOMMENDED OPERATING CONDITIONS Over operating free-air temperature range (unless otherwise noted)

| Parameter       | Description                                                 | Min | Тур | Max | Unit |

|-----------------|-------------------------------------------------------------|-----|-----|-----|------|

| $V_{DD}$        | Main power supply                                           | 3.0 | 3.3 | 3.6 | V    |

| T <sub>A</sub>  | Operating free-air temperature Industrial Temperature Range | -40 |     | +85 | °C   |

| C <sub>AC</sub> | AC coupling capacitor                                       | 75  | 100 | 265 | nF   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# Table 9. POWER SUPPLY CHARACTERISTICS and LATENCY

| Symbol                   | Parameter                      | Test Conditions                                            | Min | Typ<br>(Note 4) | Max | Unit |

|--------------------------|--------------------------------|------------------------------------------------------------|-----|-----------------|-----|------|

| VDD                      | Supply Voltage                 |                                                            | 3.0 | 3.3             | 3.6 | V    |

| IDD <sub>Active</sub>    | Active mode current            | EN_AB & EN_CD = 1, 10 Gbps, compliance test pattern        |     | 250             | 334 | mA   |

| IDD <sub>LPSlumber</sub> | Low Power Slumber mode current | EN_AB & EN_CD = 1, no input signal longer than TLP-Slumber |     | 0.8             | 1.3 | mA   |

| IDD <sub>Unplug</sub>    | Unplug mode current            | EN_AB & EN_CD = 1, no output load is detected              |     | 0.5             | 8.0 | mA   |

| IDDpd                    | Power-down mode current        | EN_AB & EN_CD = 0                                          |     | 50              | 100 | μΑ   |

| tpd                      | Latency                        | From Input to Output                                       |     |                 | 2   | ns   |

<sup>4.</sup> TYP values use VDD = 3.3 V,  $T_A = 25^{\circ}\text{C}$

# Table 10. LVCMOS CONTROL PIN CHARACTERISTICS

VDD = 3.3 V +/- 0.3 V Over operating free-air temperature range (unless otherwise noted)

| Symbol          | Parameter                        | Test Conditions | Min        | Тур | Max        | Unit         |

|-----------------|----------------------------------|-----------------|------------|-----|------------|--------------|

| 2-Level Cont    | rol Pins LVCMOS Inputs (EN_AB, E | N_CD)           |            |     |            |              |

| V <sub>IH</sub> | DC Input Logic High              |                 | 0.65 x VDD | VDD | VDD        | V            |

| $V_{IL}$        | DC Input Logic Low               |                 | GND        | GND | 0.35 x VDD | V            |

| I <sub>IH</sub> | High-level input current         |                 |            |     | 25         | μΑ           |

| I <sub>IL</sub> | Low-level input current          |                 | -25        |     |            | μΑ           |

| -Level Cont     | rol Pins LVCMOS Inputs (EQA/B/C/ | D, FGA/B/C/D)   |            |     |            |              |

|                 | 561                              |                 |            | \   |            | ` . <i>.</i> |

| $V_{IH}$         | DC Input Logic High; Setting "H"        | Input pin connected to VDD                                 | 0.92 x VDD | VDD      |            | ٧  |

|------------------|-----------------------------------------|------------------------------------------------------------|------------|----------|------------|----|

| V <sub>IF</sub>  | DC Input Logic 2/3 VDD; Setting "F"     | Input pin is left floating (Open) (Note 5)                 | 0.59 x VDD | 0.67*VDD | 0.75 x VDD | V  |

| V <sub>IR</sub>  | DC Input Logic 1/3 VDD; Setting "R"     | $R_{\text{ext}}$ 68 k $\Omega$ must be between pin and GND | 0.25 x VDD | 0.33*VDD | 0.41 x VDD | V  |

| $V_{IL}$         | DC Input Logic Low; Setting "L"         | Input pin connected to GND                                 |            | GND      | 0.08 x VDD | V  |

| I <sub>IH</sub>  | High-level input current                |                                                            |            |          | 50         | μΑ |

| I <sub>IL</sub>  | Low-level input current                 |                                                            | -50        |          |            | μΑ |

| R <sub>ext</sub> | External Resistor for input setting "R" | Rext connect to GND (±5%)                                  | 64.6       | 68       | 71.4       | kΩ |

<sup>5.</sup> Floating refers to a pin left in an open state, with no external connections.

# Table 11. CML RECEIVER AC/DC CHARACTERISTICS

VDD = 3.3 V +/- 0.3 V Over operating free-air temperature range (unless otherwise noted)

| Symbol                             | Parameter                                                           | Test Conditions                                                                                                                   | Min  | Тур | Max | Unit   |

|------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|--------|

| R <sub>RX-DIFF-DC</sub>            | Differential Input Impedance (DC)                                   |                                                                                                                                   | 72   | 100 | 120 | Ω      |

| R <sub>RX-SINGLE-DC</sub>          | Single-ended Input Impedance (DC)                                   | Measured with respect to GND over a voltage of 500 mV max.                                                                        | 18   |     | 30  | Ω      |

| ZRX-HIZ-DC-PD                      | Common-mode input impedance for V>0 during reset or power-down (DC) | VCM = 0 to 500 mV                                                                                                                 | 25   |     |     | kΩ     |

| Cac_coupling                       | AC coupling capacitance                                             |                                                                                                                                   | 75   |     | 265 | nF     |

| VRX-CM-AC-P                        | Common mode peak voltage                                            | AC up to 5 GHz                                                                                                                    |      |     | 150 | mVpeak |

|                                    | Rx AC common mode voltage during the U1 to U0 transition            | Measured at Rx pins into a pair of 50 $\Omega$ terminations into ground. Includes Tx and channel conversion, AC range up to 5 GHz |      |     | 200 | mVpeak |

| VRX-CM-DC-Conn<br>(Note 6, Note 7) | Instantaneous DC common mode voltage coupled from the far-end Tx    | Apply to all link states and during power–on, and power–off when Rx termination is equivalent of 200 kΩ                           | -0.5 |     | 1   | V      |

| VRX-CM-DC-Conn<br>(Note 6, Note 7) | Instantaneous DC common mode voltage coupled from the far-end Tx    | Apply to all link states and during power–on, and power–off when Rx termination is 50 $\Omega$                                    | -0.3 |     | 1   | V      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# Table 12. TRANSMITTER AC/DC CHARACTERISTICS

VDD = 3.3 V +/- 0.3 V Over operating free-air temperature range (unless otherwise noted)

| Symbol                  | Parameter                                                                                        | Test Conditions                                            | Min          | Тур | Max   | Unit    |

|-------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------|-----|-------|---------|

| V <sub>TX-DIFF-PP</sub> | Output differential p-p voltage swing at 100 MHz                                                 | Differential Swing  V <sub>TX-D+</sub> -V <sub>TX-D-</sub> | 0.8          | 1.0 | 1.2   | VPPd    |

| R <sub>TX-DIFF-DC</sub> | Differential TX impedance (DC)                                                                   |                                                            | 72           | 100 | 120   | Ω       |

| V <sub>TX-RCV-DET</sub> | Voltage change allowed during re-<br>ceiver detect                                               |                                                            |              |     | 600   | mV      |

| Cac_coupling            | AC coupling capacitance                                                                          |                                                            | 75           |     | 265   | nF      |

| TTX-EYE(10 Gbps)        | Transmitter eye, Include all jitter                                                              | At the silicon pad. 10 Gbps                                | 0.646        |     |       | UI      |

| TTX-EYE(5 Gbps)         | Transmitter eye, Include all jitter                                                              | At the silicon pad. 5 Gbps                                 | 0.625        |     |       | UI      |

| TTX-DJ-DD(10 Gbps)      | Transmitter deterministic jitter                                                                 | At the silicon pad. 10 Gbps                                |              |     | 0.17  | UI      |

| TTX-DJ-DD(5 Gbps)       | Transmitter deterministic jitter                                                                 | At the silicon pad. 5 Gbps                                 |              |     | 0.205 | UI      |

| Ctxparasitic            | Parasitic capacitor for TX                                                                       |                                                            |              |     | 1.1   | pF      |

| RTX-DC-CM               | Common-mode output impedance (DC)                                                                |                                                            | 18           |     | 30    | Ω       |

| VTX-DC-CM               | Instantaneous allowed DC common mode voltage at the connector side of the AC coupling capacitors | 200 kΩ single ended receiver load                          | -0.5         |     | 1     | V       |

| VTX-DC-CM               | Instantaneous allowed DC common mode voltage at the connector side of the AC coupling capacitors | 50 $\Omega$ single ended receiver load                     | -0.3         |     | 1     | V       |

| VTX-C                   | Common-mode voltage                                                                              | $ V_{TX-D+}+V_{TX-D-} /2$                                  | VDD –<br>1.5 |     | VDD   | V       |

| VTX-CM-AC-PP-<br>Active | TX AC common-mode peak-to-<br>peak voltage swing in active mode                                  | $V_{TX-D+} + V_{TX-D-}$ for both time and amplitude        |              |     | 100   | $mV_PP$ |

<sup>6.</sup> Not include +/-250 mV AC ground offset.

<sup>7.</sup> The receiver supports legacy implementations with VTX-DC+AC-CONN common mode transient up to 2.2 V.

# Table 12. TRANSMITTER AC/DC CHARACTERISTICS

VDD = 3.3 V + /-0.3 V Over operating free-air temperature range (unless otherwise noted)

| Symbol                                       | Parameter                                                                                                                               | Test Conditions                                                                                                                 | Min | Тур | Max | Unit   |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| V <sub>TX-CM-DC</sub> -Active_<br>Idle-Delta | Common mode delta voltage<br> AvgU0( V <sub>TX-D+</sub> +V <sub>TX-D-</sub>  )/2<br>-AvgU1( V <sub>TX-D+</sub> +V <sub>TX-D-</sub>  )/2 | Between U0 to U1                                                                                                                |     |     | 200 | mVpeak |

| VTX-Idle-DIFF-AC-pp                          | Idle mode AC common mode delta voltage  V <sub>TX-D+</sub> -V <sub>TX-D-</sub>                                                          | Between TX+ and TX- in idle mode. Use the HPF to remove DC components. 1/LPF. No AC and DC signals are applied to RX terminals. |     |     | 10  | mVppd  |

| V <sub>TX-Idle-DIFF-DC</sub>                 | Idle mode DC common mode delta voltage  V <sub>TX-D+</sub> -V <sub>TX-D-</sub>                                                          | Between TX+ and TX- in idle mode. Use the LPF to remove DC components. 1/HPF. No AC and DC signals are applied to RX terminals. |     |     | 10  | mV     |

### **CHANNEL PERFORMANCE**

| Gp                   | Peaking gain (Compensation at 5 GHz, relative to 100 MHz, 100 mVp-p sine wave input) | EQx = L EQx = R EQx = F EQx = H Variation around typical | -3 | 9.9<br>6.9<br>8.2<br>12.1    | +3 | dB<br>dB |

|----------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------|----|------------------------------|----|----------|

| GF                   | Flat Gain (<100 MHz, EQx=F)                                                          | FGx = L<br>FGx = R<br>FGx = F<br>FGx = H                 |    | -1.2<br>-0.2<br>+0.8<br>+1.8 |    | dB       |

|                      |                                                                                      | Variation around typical                                 | -3 |                              | +3 | dB       |

| V <sub>SW_100M</sub> | -1 dB compression point output swing (100 MHz)                                       |                                                          |    | 1000                         |    | mVppd    |

| V <sub>SW_5G</sub>   | -1 dB compression point output swing (5 GHz)                                         |                                                          |    | 800                          |    | mVppd    |

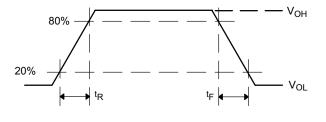

| DDNEXT               | Differential near-end crosstalk (Note 8)                                             | 100 MHz to 5 GHz, Figure 5                               |    | -40                          |    | dB       |

# SIGNAL AND FREQUENCY DETECTORS

| Vth_dsm | • | LFPS signal threshold in Low power Slumber mode      | 100 | 600 | mVppd |

|---------|---|------------------------------------------------------|-----|-----|-------|

| Vth_am  |   | Signal threshold in Active and Slumber mode (Note 9) | 45  | 175 | mVppd |

Measured using a vector network analyzer (VNA) with −15 dbm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with 50 Ω.

Below the minimum is no signal ≥ 25°C. Above the maximum is active.

# PARAMETER MEASUREMENT DIAGRAMS

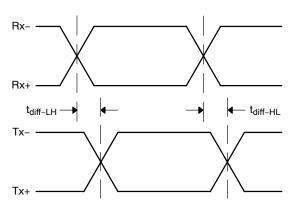

Figure 3. Propagation Delay

Figure 4. Output Rise and Fall Times

Figure 5. Channel-Isolation Test Configuration

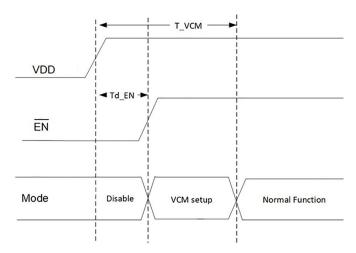

Figure 6. Power Up Timing

**Table 13. POWER UP TIMING**

| Symbol | Parameter                                  | Test Conditions | Min | Тур | Max | Unit |

|--------|--------------------------------------------|-----------------|-----|-----|-----|------|

| Td_EN  | VDD to Enable Assertion timing requirement | Figure 6.       | 0   |     |     | ms   |

| T_VCM  | Stabilization time for VCM                 | Figure 6.       |     | 330 | 400 | ms   |

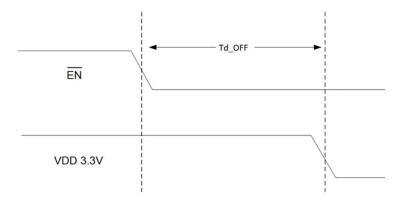

Figure 7. Power Down Timing

**Table 14. POWER DOWN TIMING**

| Symbol | Parameter                                                            | Test Conditions | Min | Тур | Max | Unit |

|--------|----------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| _      | Delay time required from EN<br>de-assertion until VDD is powered off | Figure 7.       | 900 |     |     | ms   |

### **APPLICATION GUIDELINES**

### **LFPS Compliance Testing**

As part of USB 3.2 compliance test, the host or peripheral must transmit a LFPS signal that adheres to the spec parameters. The NB7NPQ1404E2M is tested as a part of a USB compliant system to ensure that it maintains compliance while increasing system performance.

### LFPS Functionality

USB 3.2 Low Frequency Periodic Signaling.

(LFPS) to implement functions like exiting low-power modes, performing warm resets and providing link training between host and peripheral devices. LFPS signaling consists of bursts of frequencies ranging between 10 to 50 MHz and can have specific burst lengths or repeat rates.

### **Ping.LFPS for TX Compliance**

During the transmitter compliance, the system under test must transmit certain compliance patterns as defined by the USB-IF. In order to toggle through these patterns for various tests, the receiver must receive a ping.LFPS signal from either the test suite or a separate pattern generator. The standard signal comprises of a single burst period of 100 ns at 20 MHz.

# **Control Pin Settings**

Control pins A1, A0, B1, and B0 control the Flat Gain and the Equalization of channels A and B and control pins C1, C0, D1, and D0 control the Flat Gain and the Equalization of channels C and D of the NB7NPQ1404E2M Device.

The Float (Default) Setting "F" can be set by leaving the control pins in a floating state. The Redriver will internally

## **Typical Layout Practices**

- RX and TX pairs should maintain as close to a 90 Ω differential impedance as possible.

- Limit the number of vias used on each data line. It is suggested that two or fewer are used.

- Traces should be routed as straight and symmetric as possible.

bias the control pins to the correct voltage to achieve this if the pin is not connected to a voltage source. The low Setting "L" is set by pulling the control pin to ground. Likewise the high setting "H" is set by pulling the pin high to VCC. The Rexternal setting can be set by adding a 68 k $\Omega$  resistor from the control pin to ground. This will bias the Redriver internal voltage to 33% of VCC.

### **Linear Equalization**

The linear equalization that the NB7NPQ1404E2M provides compensates for losses that occur naturally along board traces and cable lines. Linear Equalization boosts high frequencies and lower frequencies linearly so when transmitting at varying frequencies, the voltage amplitude will remain consistent. This compensation electrically counters losses and allows for longer traces to be possible when routing.

# **DC Flat Gain**

DC flat gain equally boosts high and low frequency signals, and is essential for countering low frequency losses.

DC flat gain can also be used to simulate a higher input signal from a USB Controller. If a USB controller can only provide 800 mV differential to a receiver, it can be boosted to 1128 mV using 2 dB of flat gain.

### **Total Gain**

When using Flat Gain with Equalization in a USB application it is important to make sure that the total voltage does not exceed 1200 mV. Total gain can be calculated by adding the EQ gain to the FG.

- RX and TX differential pairs should always be placed and routed on the same layer directly above a ground plane.

This will help reduce EMI and noise on the data lines.

- Routing angles should be obtuse angles and kept to 135 degrees or larger.

- To minimize crosstalk, TX and RX data lines should be kept away from other high speed signals.

Figure 8. Typical Application

## **Table 15. DESIGN REQUIREMENTS**

| Design Parameter                                 | Value                                                                  |

|--------------------------------------------------|------------------------------------------------------------------------|

| Supply Voltage                                   | 3.3 V nominal, (3.0 V to 3.6 V)                                        |

| Operation Mode (Control Pin Selection)           | Floating by Default, adjust for application losses                     |

| TX AC Coupling Capacitors                        | 220 nF nominal, 75 nF to 265 nF, see Figure 8                          |

| RX AC Coupling Capacitors                        | 330 – 470 nF nominal, see Figure 8                                     |

| Power Supply Capacitors                          | 100 nF to GND close to each VCC pin, and 10 mF to GND on the VCC plane |

| Trace loss of FR4 before NB7NPQ1404E2M (Note 10) | Up to 11 dB Losses                                                     |

| Trace loss of FR4 after NB7NPQ1404E2M (Note 10)  | Up To 3 dB Losses. Keep as short as possible for best performance.     |

| Linear Range at 5 GHz                            | 900 mV differential                                                    |

| DC Flat Gain Options                             | -1.2 dB, -0.2 dB, +0.8 dB, +1.8 dB                                     |

| Equalization Options                             | 6.9 to 12.1 dB                                                         |

| Differential Trace Impedance                     | 90 Ω ±10%                                                              |

<sup>10.</sup> Trace loss of FR4 was estimated to have 1 dB of loss per 1 inch of FR4 length with matched impedance and no VIAS.

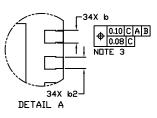

PIN 1 REFERENCE

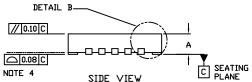

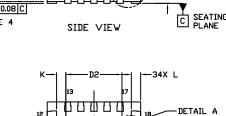

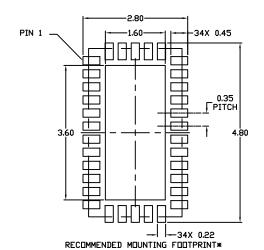

### UQFN34 2.5x4.5, 0.35P

CASE 523BR **ISSUE A**

-<u>A</u>

**DATE 10 DEC 2020**

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M,

- 2009.

CONTROLLING DIMENSION MILLIMETERS

DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS

MEASURED BETWEEN 0.15 AND 0.30 mm FROM THE

TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED PAD AS

WELL AS THE TERMINALS.

DETAIL B

TOP VIEW

For additional information on our Pb-Free strategy and soldering details, please download the IIN Semiconductor Soldering and Mounting Techniques Reference Manual, SULDERRH/D.

### **GENERIC MARKING DIAGRAM\***

= Assembly Location

= Wafer Lot ı

= Year

BOTTOM VIEW

W = Work Week

= Pb-Free Package (Note: Microdot may be in either location)

XXXX XXXX ALYW=

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON26127H           | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | UQFN34 2.5x4.5, 0.35P |                                                                                                                                                                                | PAGE 1 OF 1 |  |  |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries, onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales