Q353333N1100 系列 SoC Wi-Fi、BLE 和 SLE Combo 芯片

# 用户指南

文档版本 01

发布日期 2024-04-10

# 前言

# 概述

本文档主要介绍 Q353333N1100 系列芯片的各项基本功能,用户提供 Q353333N1100 系列芯片的应用配置方法。

# 产品版本

与本文档相对应的产品版本如下。

| 产品名称     | 产品版本   | 描述                            |

|----------|--------|-------------------------------|

| Q3533333 | N1100  | 常规版本芯片,支持 WiFi、BLE、<br>SLE 等。 |

| Q3533333 | N1100E | 雷达版本芯片,基于常规版本芯片,增加雷达检测功能。     |

# 读者对象

本文档主要适用于以下工程师:

- 技术支持工程师

- 客户开发工程师

2024-04-10 i

# 符号约定

在本文中可能出现下列标志,它们所代表的含义如下。

| 符号         | 说明                                                                        |

|------------|---------------------------------------------------------------------------|

| ▲ 危险       | 表示如不避免则将会导致死亡或严重伤害的具有高等级风险的危害。                                            |

| ♪ 警告       | 表示如不避免则可能导致死亡或严重伤害的具有中等级风险的危害。                                            |

| <u> 注意</u> | 表示如不避免则可能导致轻微或中度伤害的具有低等级风险的危害。                                            |

| 须知         | 用于传递设备或环境安全警示信息。如不避免则可能会导致设备<br>损坏、数据丢失、设备性能降低或其它不可预知的结果。<br>"须知"不涉及人身伤害。 |

| 🖺 说明       | 对正文中重点信息的补充说明。<br>"说明"不是安全警示信息,不涉及人身、设备及环境伤害信息。                           |

# 修改记录

| 文档版本  | 发布日期       | 修改说明                                                                                      |

|-------|------------|-------------------------------------------------------------------------------------------|

| 01    | 2024-04-10 | 第一次正式版本发布。                                                                                |

| 00B03 | 2024-02-22 | <ul><li>更新 "2.4 处理器子系统" 小节内容。</li><li>更新 "3.2 功能描述" 中 "AHB Master 接口"内容。</li></ul>        |

|       |            | 更新 "3.3.1 读写 Flash" 、 "3.3.2 其 他操作" 、 "3.3.3 初始化流程"和 "3.3.8 通过 DMA 方式读写 Flash 操作 流程"小节内容。 |

|       |            | • 删除 "软件擦除 Flash 后回读数据操作 流程" 小节内容。                                                        |

2024-04-10 ii

| 文档版本  | 发布日期       | 修改说明                         |

|-------|------------|------------------------------|

|       |            | • 更新 "4.1.1 概述" 、 "4.1.2 功能描 |

|       |            | 述"和 "4.1.3 RF 性能"小节内容。       |

|       |            | • 更新 "5.1.1 概述" 小节内容。        |

|       |            | • 更新 "5.7.2 功能描述" 中 EFUSE 功能 |

|       |            | 描述。                          |

|       |            | • 更新 "6.5.2 功能描述" 小节内容。      |

|       |            | • 更新 "6.6.3 工作方式"小节内容。       |

|       |            | • 更新 "6.10.2 功能描述" 小节内容。     |

| 00B02 | 2023-12-15 | • 更新 "1.1 概述" 小节内容。          |

|       |            | • 更新 "4.4.2 功能描述"小节内容。       |

|       |            | • 更新 "4.5.2 功能描述"小节内容。       |

|       |            | • 更新 "6.9.2 功能描述" 小节内容。      |

|       |            | • 更新 "6.11.2 功能描述" 小节内容。     |

| 00B01 | 2023-09-11 | 第一次临时版本发布。                   |

2024-04-10 iii

# 目 录

| 前言               |    |

|------------------|----|

| 1 产品概述           | 1  |

|                  |    |

| 1.1 概述           |    |

| 1.2 功能描述         | 2  |

| 1.2.1 功能特性       | 2  |

| 1.2.2 遵从的标准与协议   | 3  |

| 1.3 逻辑框图         | 4  |

| 1.4 应用场景         | 6  |

|                  |    |

| 2 系统             |    |

| 2.1 复位           | 7  |

| 2.1.1 概述         | 7  |

| 2.1.2 复位控制       | 7  |

| 2.1.3 复位信号       | 8  |

| 2.1.4 复位约束       | g  |

| 2.2 时钟           | g  |

| 2.2.1 概述         | g  |

| 2.2.2 时钟分配       | g  |

| 2.2.3 时钟控制       | 10 |

| 2.3 电源管理与低功耗模式控制 | 10 |

| 2.3.1 概述         | 10 |

| 2.3.2 系统工作模式     | 10 |

| 2.4 处理器子系统       | 11 |

| 2.5 存储器空间映射      | 11 |

| 2.6 中断系统                           | 14 |

|------------------------------------|----|

| 2.6.1 中断分配                         | 14 |

| 2.6.2 中断结构                         | 16 |

| 2.6.3 寄存器概览                        | 17 |

| 2.6.4 寄存器描述                        | 18 |

| 2.7 RTC                            | 21 |

| 2.7.1 概述                           | 21 |

| 2.7.2 功能描述                         | 21 |

| 2.8 Timer                          | 22 |

| 2.8.1 概述                           | 22 |

| 2.8.2 功能描述                         | 22 |

| 2.9 看门狗                            | 22 |

| 2.9.1 概述                           | 22 |

| 2.9.2 功能描述                         | 23 |

| 3 QSPI Flash 控制器                   | 24 |

| 3.1 概述                             | 24 |

| 3.2 功能描述                           | 25 |

| 3.3 工作方式                           |    |

| 3.3.1 读写 Flash                     |    |

| 3.3.2 其他操作                         | 26 |

| 3.3.3 初始化流程                        | 27 |

| 3.3.4 通过寄存器方式读 Flash 操作流程          | 27 |

| 3.3.5 通过寄存器方式写 Flash 操作流程          | 28 |

| 3.3.6 通过寄存器方式其他操作流程                | 29 |

| 3.3.7 通过 AHB Slave 直接读写 Flash 操作流程 | 30 |

| 3.3.8 通过 DMA 方式读写 Flash 操作流程       | 30 |

| 3.4 寄存器概览                          |    |

| 3.5 寄存器描述                          |    |

| 4 WiFi /BLE & SLE 系统               |    |

| 4.1 WiFi / BLE & SLE RF            |    |

| 7.1 WHIT / DEL & OLL IXI           | 52 |

| 4.1.2 功能描述             | 53 |

|------------------------|----|

| 4.1.3 RF 性能            | 53 |

| 4.2 WiFi/BLE & SLE ABB | 64 |

| 4.2.1 概述               | 64 |

| 4.2.2 功能描述             | 65 |

| 4.2.3 工作方式             | 65 |

| 4.3 WiFi PHY           | 66 |

| 4.3.1 概述               | 66 |

| 4.3.2 功能描述             | 66 |

| 4.3.3 工作方式             | 67 |

| 4.4 WiFi MAC           | 68 |

| 4.4.1 概述               | 68 |

| 4.4.2 功能描述             | 68 |

| 4.4.3 工作方式             | 69 |

| 4.4.3.1 AP 模式          | 69 |

| 4.4.3.2 STA 模式         | 69 |

| 4.4.3.3 Monitor 模式     | 69 |

| 4.4.3.4 AP 与 STA 共存    | 69 |

| 4.4.3.5 CSI 模式         | 69 |

| 4.5 BLE/SLE            | 70 |

| 4.5.1 概述               | 70 |

| 4.5.2 功能描述             | 70 |

| 4.5.3 工作方式             | 73 |

| 4.5.3.1 中断             | 73 |

| 4.5.3.2 加密             | 73 |

| 4.6 雷达特性               | 73 |

| 4.6.1 概述               | 73 |

| 4.6.2 功能描述             | 74 |

| 4.6.2.1 靠近检测           |    |

| 4.6.2.2 存在检测           |    |

| 4.6.3 工作方式             |    |

|                        |    |

| 5.1 安全子系统     | 75  |

|---------------|-----|

| 5.1.1 概述      | 75  |

| 5.1.2 功能描述    | 75  |

| 5.2 对称加解密模块   | 76  |

| 5.2.1 概述      | 76  |

| 5.2.2 功能描述    | 76  |

| 5.3 HASH 模块   | 76  |

| 5.3.1 概述      | 76  |

| 5.3.2 功能描述    | 76  |

| 5.4 密钥派生模块    | 77  |

| 5.4.1 概述      | 77  |

| 5.4.2 功能描述    | 77  |

| 5.5 非对称公钥算法模块 | 77  |

| 5.5.1 概述      | 77  |

| 5.5.2 功能描述    | 77  |

| 5.6 随机数生成模块   | 78  |

| 5.6.1 概述      | 78  |

| 5.6.2 功能描述    | 78  |

| 5.7 EFUSE     | 78  |

| 5.7.1 概述      | 78  |

| 5.7.2 功能描述    | 78  |

| 6 外围设备        | 80  |

| 6.1 IO MUX    |     |

| 6.1.1 概述      |     |

| 6.1.2 软用管脚描述  | 80  |

| 6.1.3 寄存器概览   | 87  |

| 6.1.4 寄存器描述   | 89  |

| 6.2 GPIO      | 128 |

| 6.2.1 概述      | 128 |

| 6.2.2 功能描述    | 128 |

| 6.2.3 工作方式    | 129 |

| 6.2.3.1 初始化配置 | 129 |

| 6.2.3.2 边沿中断配置    | 129 |

|-------------------|-----|

| 6.2.3.3 电平中断配置    | 130 |

| 6.2.4 寄存器概览       | 131 |

| 6.2.5 寄存器描述       | 131 |

| 6.3 UART          | 139 |

| 6.3.1 概述          | 139 |

| 6.3.2 功能描述        | 139 |

| 6.3.3 工作方式        | 140 |

| 6.3.4 寄存器概览       | 143 |

| 6.3.5 寄存器描述       | 144 |

| 6.4 I2C           | 162 |

| 6.4.1 概述          | 162 |

| 6.4.2 功能描述        | 163 |

| 6.4.3 工作方式        | 163 |

| 6.4.3.1 不使用 FIFO  | 163 |

| 6.4.3.2 使用 FIFO   | 165 |

| 6.4.4 寄存器概览       | 167 |

| 6.4.5 寄存器描述       | 168 |

| 6.5 SPI           | 179 |

| 6.5.1 概述          | 179 |

| 6.5.2 功能描述        | 179 |

| 6.6 PWM           |     |

| 6.6.1 概述          | 179 |

| 6.6.2 功能描述        | 179 |

| 6.6.3 工作方式        | 180 |

| 6.6.4 寄存器概览       | 180 |

| 6.6.5 寄存器描述       | 182 |

| 6.7 Tsensor       | 191 |

| 6.7.1 概述          | 191 |

| 6.7.2 功能描述        | 191 |

| 6.7.3 工作方式        |     |

| 6.7.3.1 正常检测温度模式  | 192 |

| 6.7.3.2 高低温门限中断模式 | 192 |

| 用尸指南             | 日 录 |

|------------------|-----|

| 6.7.3.3 过温保护中断模式 | 193 |

| 6.7.4 寄存器概览      | 194 |

| 6.7.5 寄存器描述      | 195 |

| 6.8 I2S          |     |

| 6.8.1 概述         | 202 |

| 6.8.2 功能描述       | 202 |

| 6.9 QSPI         | 203 |

| 6.9.1 概述         | 203 |

| 6.9.2 功能描述       | 203 |

| 6.10 DMA         | 204 |

| 6.10.1 概述        | 204 |

| 6.10.2 功能描述      | 204 |

| 6.10.3 工作方式      | 205 |

| 6.10.4 寄存器概览     | 206 |

| 6.10.5 寄存器描述     | 208 |

| 6.11 ADC         | 234 |

| 6.11.1 概述        | 234 |

| 6.11.2 功能描述      | 235 |

| 7 JTAG           | 236 |

| 7.1 概述           |     |

| 7.2 调试接口         |     |

| r entre see at 1 |     |

A 缩略语......237

**1** 产品概述

- 1.1 概述

- 1.2 功能描述

- 1.3 逻辑框图

- 1.4 应用场景

## 1.1 概述

Q3533333N1100 系列芯片是一款高度集成的 2.4GHz SoC Wi-Fi、BLE 和 SLE 的 Combo 芯片,集成 IEEE 802.11b/g/n/ax 基带和 RF 电路,RF 电路包括功率放大器 PA、低噪声放大器 LNA、RF balun、天线开关以及电源管理等模块;支持 HT 20MHz/40MHz、HE 20MHz 标准带宽,提供最大 150Mbit/s 物理层速率。

Q353333N1100 系列芯片 Wi-Fi 基带支持正交频分多址 (OFDMA) 技术,正交频分复用 (OFDM) 技术,并向下兼容直接序列扩频 (DSSS) 和补码键控 (CCK) 技术,支持 IEEE 802.11b/g/n 协议的各种数据速率,支持 IEEE 802.11ax 协议的MCS0~MCS9 速率。

Q353333N1100 系列芯片支持 BLE 1MHz/2MHz 频宽,支持 BLE 5.4 协议,支持 BLE Mesh 和 BLE 网关功能,最大空口速率 2Mbps。

Q353333N1100 系列芯片支持 SLE 1MHz/2MHz/4MHz 频宽,支持 SLE1.0 协议,支持 SLE 网关功能,Q353333N1100 最大空口速率 4Mbps,Q353333N1100E 最大空口速率 12Mbps。

Q353333N1100 系列芯片集成高性能 32bit 微处理器、硬件安全引擎以及丰富的外设接口, 外设接口包括 SPI、QSPI、UART、I2C、PWM、GPIO 和多路 ADC; 芯片内置 SRAM 和 Flash,可独立运行,并支持在 Flash 上运行程序。

Q353333N11001E 支持雷达感知功能,智能感知房间内是否有人。

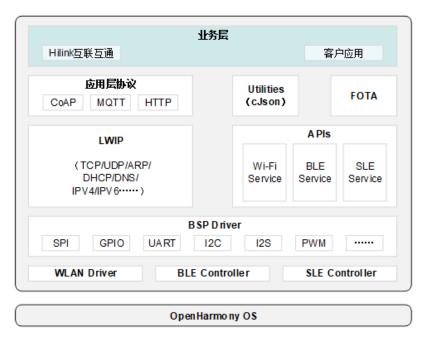

Q353333N1100 系列芯片支持 OpenHarmony 和第三方组件,并配套提供开放、易用的开发和调试运行环境。

Q353333N1100 系列芯片适应于智能家电等物联网智能终端领域。

## 1.2 功能描述

## 1.2.1 功能特性

#### Wi-Fi

- 1×1 2.4GHz 频段。

- PHY 支持 IEEE 802.11b/g/n/ax。

MAC 支持 IEEE 802.11d/e/i/k/v/r/w。

- 支持 802.11n 20MHz/40MHz 频宽,支持 802.11ax 20MHz 频宽。

- 支持最大速率: 150Mbit/s@HT40 MCS7, 114.7Mbit/s@HE20 MCS9。

- 内置 PA 和 LNA,集成 TX/RX Switch、Balun 等。

- 支持 STA 和 SoftAP 形态,作为 SoftAP 时最大支持 6 个 STA 接入。

- 支持 A-MPDU、A-MSDU。

- 支持 Block-ACK。

- 支持 QoS,满足不同业务服务质量需求。

- 支持 WPA/WPA2/WPA3 personal、WPS2.0、WAPI。

- 支持 RF 自校准方案。

- 支持 STBC 和 LDPC。

- 支持雷达感知功能(仅 Q353333N11001E 芯片支持)。

#### 蓝牙

- 低功耗蓝牙 Bluetooth Low Energy (BLE)。

- 支持 BLE 5.4。

2024-04-10

- 支持 125Kbit/s、500Kbit/s、1Mbit/s、2Mbit/s 速率。

- 支持多路广播。

- 支持 Class 1。

- 支持高功率 20dBm。

- 支持 BLE Mesh, 支持 BLE 网关。

#### 星闪

- 星闪低功耗接入技术 Sparklink Low Energy (SLE)。

- 支持 SLE 1.0。

- 支持 SLE 1MHz/2MHz/4MHz,最大空口速率 12Mbit/s。

- 支持 Polar 信道编码。

- 支持 SLE 网关。

#### CPU 子系统

- 高性能 32bit 微处理器,最大工作频率 240MHz。

- 内嵌 SRAM 606KB、ROM 300KB。

- 内嵌 4MB Flash。

#### 外围接口

- 1个 SPI 接口、1个 QSPI 接口、2个 I2C 接口、1个 I2S 接口、3个 UART 接口、19个 GPIO 接口、6 路 ADC 输入、8 路 PWM (注:上述接口通过复用实现)。

- 外部晶体时钟频率 24MHz、40MHz。

#### 其他信息

- 电源电压输入: 典型值 3.3V/5V。

IO 电源电压支持 1.8V/3.3V, 外接 MCU 和调试的 UART 支持 5V tolerant。

- 封装: QFN-40, 5mm×5mm。

- 工作温度: -40℃~+85℃。

## 1.2.2 遵从的标准与协议

Q353333N1100 系列芯片支持以下标准协议:

2024-04-10

用户指南 1 产品概述

- 802.11-2020 Wireless LAN Medium Access Control(MAC) and Physical Layer (PHY) Specifications.

- Bluetooth Core Specification Version 5.4.

- Sparklink Wireless Communication Low Enery Air-interface Technical Requirements V01.00.

## 1.3 逻辑框图

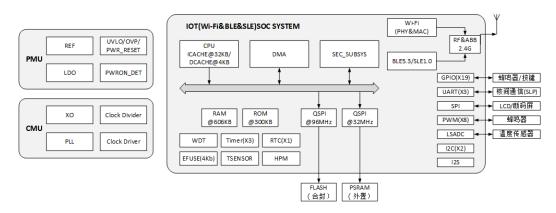

Q353333N1100 系列芯片逻辑框图如图 1-1 所示。

#### 图1-1 Q353333N1100 系列芯片逻辑框图

其中, 图中的各模块功能描述如表 1-1 所示。

表1-1 模块功能描述

| 模块名                   | 功能描述          |

|-----------------------|---------------|

| PMU                   | 电源管理单元。       |

| REF                   | 电压参考。         |

| UVLO/OVP/PWR<br>RESET | 欠压/过压保护、电源复位。 |

| LDO                   | 低压差线性稳压器。     |

| PWRON DET             | 上电检测。         |

| СМИ                   | 时钟管理单元。       |

| XO                    | 晶体振荡器。        |

| Clock Divider         | 时钟分频器。        |

| 模块名          | 功能描述          |

|--------------|---------------|

| PLL          | 锁相环。          |

| Clock Driver | 时钟驱动器。        |

| CPU          | 中央处理单元。       |

| DMA          | 直接存储器访问单元。    |

| SEC SUBSYS   | 安全子系统。        |

| RAM          | 随机存取存储器。      |

| ROM          | 只读存储器。        |

| QSPI         | 4线 SPI。       |

| WDT          | 看门狗单元。        |

| Timer        | 定时器。          |

| RTC          | 实时时钟单元。       |

| EFUSE        | 加解密和芯片 ID 存储。 |

| TSENSOR      | 温度传感器。        |

| HPM          | 工艺监视单元。       |

| Wi-Fi        | WiFi 通信模块。    |

| BLE          | 低功耗蓝牙通信模块。    |

| SLE          | SLE 通信模块。     |

| PHY          | 信道调制、解调。      |

| MAC          | MAC 层业务处理。    |

| RF&ABB       | 射频&模拟模块。      |

| GPIO         | 通用输入输出接口。     |

| UART         | 通用异步串行接口控制器。  |

| SPI          | 串行外设接口控制器。    |

| PWM          | 脉冲宽度调制单元。     |

用户指南 1 产品概述

| 模块名   | 功能描述           |  |

|-------|----------------|--|

| LSADC | 低速 ADC。        |  |

| 12C   | 集成电路互连总线控制器。   |  |

| 128   | 集成电路内置音频总线控制器。 |  |

| FLASH | 闪存。            |  |

| PSRAM | 伪静态存储器。        |  |

# 1.4 应用场景

Q353333N1100 系列芯片适应于智能家电等物联网智能终端领域,典型应用框图如图 1-2 所示。

图1-2 Q353333N1100 系列芯片典型应用框图

# **2** 系统

- 2.1 复位

- 2.2 时钟

- 2.3 电源管理与低功耗模式控制

- 2.4 处理器子系统

- 2.5 存储器空间映射

- 2.6 中断系统

- 2.7 RTC

- 2.8 Timer

- 2.9 看门狗

# 2.1 复位

## 2.1.1 概述

复位模块根据输入复位源产生各个模块的复位信号,支持整个芯片的全局复位和各个模块的单独复位。

复位实现为异步复位,同步撤离。

## 2.1.2 复位控制

复位控制的输入信号分为:

• 全局复位控制。

#### • 单独模块复位控制。

芯片可以使用的复位控制方式如表 2-1 所示。

表2-1 复位控制

| 复位方式                          | 来源                                                | 复位时间     | 复位范围      | 复位后芯 片模式                       |

|-------------------------------|---------------------------------------------------|----------|-----------|--------------------------------|

| POR 复位<br>(Power on<br>Reset) | PMU POR 模块输出。                                     | 400µs    | 全芯片       | WORK                           |

| Watch Dog 复位<br>控制            | Watch Dog 模块输出,软件可以屏蔽。                            | -        | 全芯片/模块可配置 | WORK                           |

| 全局软复位控制                       | 软件配置。                                             | -        | 全芯片       | WORK                           |

| 模块软复位控制                       | CRG (Clock and Reset<br>Generator) 寄存器, 软件<br>配置。 | 软件控<br>制 | 模块        | 该模块处于<br>于复位状态,其余模块处于<br>Work。 |

# 2.1.3 复位信号

表2-2 复位信号

| 信号名称       | 含义                                                               | 复位时间    | I/O | 说明 |

|------------|------------------------------------------------------------------|---------|-----|----|

| PWR_O<br>N | 芯片上下电管脚: 1. 拉高 PWR_ON 管脚, 芯片完成上电。 2. 拉低 PWR_ON 管脚, 芯片完成复位, 并且下电。 | 1ms/5ms | I   | -  |

## 2.1.4 复位约束

芯片第一次上电, PWR\_ON 时间要大于 1ms; 芯片上电后, 拉低 PWR\_ON 再拉高 PWR\_ON 的时间需要大于 5ms。

## 2.2 时钟

## 2.2.1 概述

时钟管理模块对芯片时钟输入、生成、控制进行统一的管理, 其功能包括:

- 时钟输入的管理和控制。

- 时钟高频与低频的切换。

- 时钟分频和控制。

- 时钟的门控控制。

- 各模块工作时钟的生成。

## 2.2.2 时钟分配

正常工作时,各模块的时钟分配如表 2-3 所示。

表2-3 模块时钟分配

| 模块名称     | 时钟频率<br>(MHz) | 模块名称                  | 时钟频率<br>(MHz) |

|----------|---------------|-----------------------|---------------|

| CPU      | 240           | WDT (WatchDog)        | 晶体分频          |

| CPU Bus  | 240           | RTC (Real-Time Clock) | 0.032         |

| Timer    | 晶体分频          | UART                  | 160           |

| GPIO     | 120           | EFUSE                 | 晶体            |

| WiFi MAC | 120           | BT MAC                | 32            |

| WiFi PHY | 320           | BT PHY                | 32            |

| 晶体       | 40/24         | PMU OSC               | 0.032         |

| I2C      | 80            | SPI                   | 160           |

用户指南 2 系统

| 模块名称 | 时钟频率<br>(MHz) | 模块名称 | 时钟频率<br>(MHz) |

|------|---------------|------|---------------|

| QSPI | 64            | 12S  | 8.192 等       |

## 2.2.3 时钟控制

时钟管理模块主体包括:

- PLL 频率控制。

- 时钟分频和时钟源选择控制。

- 时钟门控管理。

## 2.3 电源管理与低功耗模式控制

### 2.3.1 概述

芯片的低功耗模式用于有效减少芯片的功耗,芯片提供多种低功耗的控制来动态降低 芯片的功耗:

• 系统工作模式控制

除了 Work 模式之外,各种模式对功耗都有一定的减少作用,可以根据实际的功耗要求和功能要求选择不同的工作模式。

- 时钟门控和时钟频率调整

- 提供时钟关断功能,可以关闭没有必要的时钟,减少芯片的功耗。

- 系统工作的时钟频率可以进行调整,在满足功能的情况下可以调节时钟频率,动态降低芯片功耗。

- 模块级低功耗控制

提供模块级的低功耗控制,可以在某模块不工作的情况下,关断该模块或使模块 处于低功耗状态,以减少芯片的功耗。

## 2.3.2 系统工作模式

系统工作模式分为以下三种模式:

• Work

2024-04-10

正常工作状态,所有电源供电均打开,完成正常的 WiFi 收发等业务。

#### Light Sleep

浅睡模式为可快速恢复业务收发的睡眠模式,关闭收发时钟以降低功耗。此时 CPU 配置为 WFI (Wait For Interrupt) 模式,等待中断唤醒后恢复收发,Flash、IO 保持供电,系统内发生任意中断均可唤醒 CPU (如定时中断,外设通信中断,GPIO 中断等); SoC 系统可选晶体或 PLL 时钟,时钟频率和外设的通信速率有关。

#### Shutdown

关机模式,芯片通过 PWR\_ON 管脚拉低之后进入 Shutdown 模式,整芯片下电。当 PWR ON 管脚拉高后退出 Shutdown 模式,进入到 Work 模式。

## 2.4 处理器子系统

用户指南

系统提供一个自研 RISC-V 处理器作为主控 CPU,完成各种系统任务和控制工作。处理器带有 32KB 指令 Cache、4KB 数据 Cache。

该芯片 CPU 具有以下功能特点:

- 处理器的工作频率最高可达 240MHz。

- 支持直接模式和向量模式的中断方式,支持 1 个 nmi 中断,以及 64 个非标准外部中断。

- 支持 Flash Patch 功能,支持 192 个指令比较器和 2 个地址比较器。

- 支持边沿和电平两种中断触发方式。

- 支持 PMP (Physical Memory Protection) 功能。

- 支持 JTAG 和 SWD (Serial Wire Debug) 调试接口。

## 2.5 存储器空间映射

地址空间映射如表 2-4 所示。

#### 表2-4 存储器地址空间映射

| Slave Name | 地址范围<br>(Start) | 地址范围<br>(End) |

|------------|-----------------|---------------|

| CPU_ITCM   | 0x0010_0000     | 0x0017_FFFF   |

2024-04-10

| Slave Name                         | 地址范围        | 地址范围        |

|------------------------------------|-------------|-------------|

|                                    | (Start)     | (End)       |

| CPU_DTCM                           | 0x0018_0000 | 0x001C_7FFF |

| -reserved (读取返回 dead_beef)         | 0x001C_8000 | 0x001F_FFFF |

| NOR_FLASH(读取范围超过 Flash 大小时,地址卷绕读取) | 0x0020_0000 | 0x009F_FFFF |

| SHARE_RAM                          | 0x00A0_0000 | 0x00A9_8FFF |

| -reserved (读取返回 resp_error)        | 0x00A9_9000 | 0x00BF_FFFF |

| PKE_ROM                            | 0x00C0_0000 | 0x00C0_0BFF |

| -reserved (读取返回随机值)                | 0x00C0_0C00 | 0x00C0_0FFF |

| -reserved (读取返回 resp_error)        | 0x00C0_1000 | 0x3FFF_FFFF |

| SYS_CTL0                           | 0x4000_0000 | 0x4000_3FFF |

| -reserved (读取返回 dead_dead)         | 0x4000_4000 | 0x4000_4FFF |

| RTC                                | 0x4000_5000 | 0x4000_50FF |

| -reserved (读取返回 dead_dead)         | 0x4000_5100 | 0x4000_5FFF |

| WDT                                | 0x4000_6000 | 0x4000_6FFF |

| -reserved (读取返回 dead_dead)         | 0x4000_7000 | 0x4000_FFFF |

| -reserved (读取返回 resp_error)        | 0x4001_0000 | 0x43FF_FFFF |

| SYS_CTL1                           | 0x4400_0000 | 0x4400_1FFF |

| TIMER                              | 0x4400_2000 | 0x4400_2FFF |

| -reserved (读取返回 dead_dead)         | 0x4400_3000 | 0x4400_3FFF |

| SYS_CTL2                           | 0x4400_4000 | 0x4400_7FFF |

| EFUSE_CTL                          | 0x4400_8000 | 0x4400_BFFF |

| LSADC_CTL                          | 0x4400_C000 | 0x4400_CFFF |

| IO_CONFIG                          | 0x4400_D000 | 0x4400_DFFF |

| TSENSOR_CTL                        | 0x4400_E000 | 0x4400_EFFF |

| -reserved (读取返回 dead_dead)         | 0x4400_F000 | 0x4400_FFFF |

| UART0                              | 0x4401_0000 | 0x4401_0FFF |

| UART1                              | 0x4401_1000 | 0x4401_1FFF |

| Slave Name                  | 地址范围        | 地址范围        |

|-----------------------------|-------------|-------------|

|                             | (Start)     | (End)       |

| UART2                       | 0x4401_2000 | 0x4401_2FFF |

| -reserved (读取返回 dead_dead)  | 0x4401_3000 | 0x4401_7FFF |

| I2C0                        | 0x4401_8000 | 0x4401_80FF |

| I2C1                        | 0x4401_8100 | 0x4401_81FF |

| -reserved (读取返回 dead_dead)  | 0x4401_8200 | 0x4401_FFFF |

| SPI                         | 0x4402_0000 | 0x4402_00FF |

| -reserved (读取返回 dead_dead)  | 0x4402_0100 | 0x4402_0FFF |

| QSPI                        | 0x4402_1000 | 0x4402_10FF |

| -reserved (读取返回 dead_dead)  | 0x4402_1100 | 0x4402_3FFF |

| PWM0~7                      | 0x4402_4000 | 0x4402_4FFF |

| 128                         | 0x4402_5000 | 0x4402_50FF |

| -reserved (读取返回 dead_dead)  | 0x4402_5100 | 0x4402_7FFF |

| GPI00~7                     | 0x4402_8000 | 0x4402_8FFF |

| GPIO8~15                    | 0x4402_9000 | 0x4402_9FFF |

| GPIO16~18                   | 0x4402_A000 | 0x4402_AFFF |

| -reserved (读取返回 dead_dead)  | 0x4402_B000 | 0x440F_FFFF |

| SEC_APB                     | 0x4410_0000 | 0x4411_4FFF |

| -reserved (读取返回 dead_dead)  | 0x4411_5000 | 0x4411_FFFF |

| WIFI_SUB                    | 0x4421_0000 | 0x4421_3FFF |

| -reserved (读取返回 resp_error) | 0x4421_4000 | 0x47FF_FFFF |

| SFC_CFG                     | 0x4800_0000 | 0x4800_1FFF |

| -reserved (读取返回 resp_error) | 0x4800_2000 | 0x48FF_FFFF |

| BSLE_SUB                    | 0x4900_0000 | 0x4903_FFFF |

| -reserved (读取返回 resp_error) | 0x4904_0000 | 0x49FF_FFFF |

| DMA_CFG                     | 0x4A00_0000 | 0x4A00_0FFF |

# 2.6 中断系统

# 2.6.1 中断分配

芯片支持向量模式和直接模式的中断方式,支持边沿和电平两种中断触发方式。支持优先级可编程,优先级配置寄存器(共3bit)可配置7级的优先级。

#### 中断系统包括:

● CPU 的内部标准中断:中断编号 0~25。

• CPU 外部的非标准中断: 所支持的非标准中断编号如表 2-5 所示。

#### 表2-5 非标准中断编号列表

| Int No. | Int Name     | Description         |

|---------|--------------|---------------------|

| nmi     | TEE_NMI_INT  | nmi 软中断&WDT 全局中断。   |

| 26      | TIMER_INT[0] | Timer[0]的全局中断。      |

| 27      | TIMER_INT[1] | Timer[1]的全局中断。      |

| 28      | TIMER_INT[2] | Timer[2]的全局中断。      |

| 29      | RTC_IRQ      | RTC 的全局中断。          |

| 30      | Reserved     | 保留。                 |

| 31      | I2C0_INT     | I2C0 中断。            |

| 32      | I2C1_INT     | I2C1 中断。            |

| 33      | GPIO_INT[0]  | GPIO[7:0]上报的组合中断。   |

| 34      | GPIO_INT[1]  | GPIO[15:8]上报的组合中断。  |

| 35      | GPIO_INT[2]  | GPIO[23:16]上报的组合中断。 |

| 36      | SOFT_INT[0]  | CPU 软中断 0。          |

| 37      | SOFT_INT[1]  | CPU 软中断 1。          |

| 38      | SOFT_INT[2]  | CPU 软中断 2。          |

| 39      | SOFT_INT[3]  | CPU 软中断 3。          |

| Int No. | Int Name                 | Description     |

|---------|--------------------------|-----------------|

| 40      | COEX_WL_INT              | 共存 WLAN 软中断。    |

| 41      | COEX_BT_INT              | 共存 BT 软中断。      |

| 42      | COEX_WIFI_R<br>ESUME_INT | 共存 WLAN 恢复射频中断。 |

| 43      | SPI_INT                  | SPI中断。          |

| 44      | WLPHY_INT                | WLAN PHY 中断。    |

| 45      | WLMAC_INT                | WLAN MAC 中断。    |

| 46      | BLE_INT                  | BLE 中断。         |

| 47      | SLE_INT                  | SLE 中断。         |

| 48      | TSENSOR_INT              | TSENSOR 中断。     |

| 49      | PMU_CMU_ER<br>R_INT      | PMU/CMU 异常中断。   |

| 50      | DIAG_INT                 | 维测中断。           |

| 51      | I2S_INT                  | I2S 中断。         |

| 52      | QSPI_INT                 | QSPI 中断。        |

| 53      | UART0_INT                | UART0 中断。       |

| 54      | UART1_INT                | UART1 中断。       |

| 55      | UART2_INT                | UART2 中断。       |

| 56      | PWM_ABNOR<br>_INT        | PWM_ABNOR 中断。   |

| 57      | PWM_CFG_IN<br>T          | PWM_CFG 中断。     |

| 58      | SFC_INT                  | SFC 中断。         |

| 59      | DMA_INT                  | DMA 中断。         |

| 60      | TIMER_ABNO<br>R_INT      | TIMER[2:0]异常中断。 |

| 61      | I2S_TX_INT               | I2S_TX 中断。      |

| 62      | I2S_RX_INT               | I2S_RX 中断。      |

| Int No. | Int Name                | Description       |

|---------|-------------------------|-------------------|

| 63      | PKE_REE_INT             | PKE REE 中断。       |

| 64      | SPACC_REE_I<br>NT       | SPACC REE 中断。     |

| 65      | RKP_REE_INT             | RKP REE 中断。       |

| 66      | KLAD_REE_IN<br>T        | KLAD REE 中断。      |

| 67      | GLP UART RX<br>WAKE INT | GLP UART RX 唤醒中断。 |

| 68      | TIMING_GEN_I<br>NT      | TIMING_GEN 中断。    |

| 69      | MAC_MONITO<br>R_INT     | MAC 维测中断。         |

| 70      | MEM_MONITO<br>R_INT     | MEM 维测中断。         |

| 71      | TCM_MONITO<br>R_INT     | TCM 维测中断。         |

| 72      | LSADC_INTR              | LSADC 中断。         |

| 89~73   | Reserved                | 保留。               |

## 2.6.2 中断结构

芯片使用 CPU 内部集成的中断控制器,所有的外设或寄存器触发的非标准中断均直接 连至 CPU 内部进行处理。

本节主要介绍非 IP 中断,各个 IP 的中断说明请参见各 IP 对应章节。

## NMI 中断

#### 须知

TEE\_NMI\_INT[tee\_nmi\_int]不会自动清零,在触发中断后需要将该值写回 0。

NMI(Non-Maskable Interrupt)中断用于控制软件,由 WDOG 中断和寄存器触发,通过使能 WDOG 或写 TEE\_NMI\_INT[tee\_nmi\_int]为 1 触发 NMI 中断。

#### 软中断

软中断为通过配置寄存器触发中断的中断触发方式,包含4个可以通过写寄存器触发的中断(软中断0~软中断3)。

软中断 0~软中断 3 的触发方式相同,以使用软中断 0 为例,配置步骤如下:

步骤 1 写 SOFT\_INT\_EN[soft\_int0\_en]为 1, 打开软中断 0 的使能。

步骤 2 写 SOFT\_INT\_SET[soft\_int0\_set]为 1,将软中断 0 置位。 此寄存器为自清零寄存器,写 1 后自动回零,写 0 无效。

步骤 3 软件进入软中断 0 处理程序,此时可读取 SOFT\_INT\_STS[soft\_int0\_sts]查询中断状态:

● 0: 无中断。

● 1: 有中断。

步骤 4 写 SOFT\_INT\_CLR[soft\_int0\_clr]为 1,清除软中断 0。

此寄存器为自清零寄存器,写1后自动回零,写0无效。

#### ----结束

## 2.6.3 寄存器概览

中断系统寄存器概览如表 2-6 所示。

表2-6 中断系统寄存器概览 (基址是 0x44000000)

| Offset Address | Register     | Description           |

|----------------|--------------|-----------------------|

| 0x0040         | NMI_INT      | WDT 中断查询&NMI 中断配置寄存器。 |

| 0x0150         | SOFT_INT_EN  | CPU 软中断使能寄存器。         |

| 0x0154         | SOFT_INT_SET | CPU 软中断置位寄存器。         |

| 0x0158         | SOFT_INT_CLR | CPU 软中断清除寄存器。         |

| 0x015C         | SOFT_INT_STS | CPU 软中断查询寄存器。         |

2 系统

## 2.6.4 寄存器描述

## NMI\_INT

用户指南

NMI\_INT 为 WDT 中断查询&NMI 中断配置寄存器。

Offset Address: 0x0040 Total Reset Value: 0x00000000

| Bits | Access | Name         | Description        | Reset      |

|------|--------|--------------|--------------------|------------|

| 31:2 | RO     | reserve<br>d | 保留。                | 0x00000000 |

| 1    | RO     | wdt_int      | 看门狗中断查询寄存器。        | 0x0        |

|      |        |              | 0: WDT 中断无效;       |            |

|      |        |              | 1: WDT 中断有效。       |            |

| 0    | RW     | tee_nmi      | 软控 nmi 中断配置寄存器。    | 0x0        |

|      |        | _""          | 0:拉低 CPU NMI 软中断;  |            |

|      |        |              | 1: 拉高 CPU NMI 软中断。 |            |

## SOFT\_INT\_EN

SOFT\_INT\_EN 为 CPU 软中断使能寄存器。

Offset Address: 0x0150 Total Reset Value: 0x00000000

| Bits | Access | Name             | Description                   | Reset     |

|------|--------|------------------|-------------------------------|-----------|

| 31:4 | RO     | reserve<br>d     | 保留。                           | 0x0000000 |

| 3    | RW     | soft_int<br>3_en | CPU 软中断 3 使能开关寄存器。<br>0:使能无效; | 0x0       |

|      |        |                  | 1: 使能有效。                      |           |

| 2    | RW     | soft_int<br>2_en | CPU 软中断 2 使能开关寄存器。            | 0x0       |

|      |        |                  | 0: 使能无效;                      |           |

|      |        |                  | 1: 使能有效。                      |           |

用户指南 2 系统

| Bits | Access | Name             | Description        | Reset |

|------|--------|------------------|--------------------|-------|

| 1    | RW     | soft_int<br>1_en | CPU 软中断 1 使能开关寄存器。 | 0x0   |

|      |        |                  | 0: 使能无效;<br>       |       |

|      |        |                  | 1: 使能有效。           |       |

| 0    | RW     | soft_int<br>0_en | CPU 软中断 0 使能开关寄存器。 | 0x0   |

|      |        |                  |                    |       |

|      |        |                  | 0: 使能无效;           |       |

|      |        |                  | 1: 使能有效。           |       |

## SOFT\_INT\_SET

SOFT\_INT\_SETCPU 软中断置位寄存器。

Offset Address: 0x0154 Total Reset Value: 0x00000000

| Bits | Access       | Name              | Description                            | Reset     |

|------|--------------|-------------------|----------------------------------------|-----------|

| 31:4 | RO           | reserved          | 保留。                                    | 0x0000000 |

| 3    | W1_PU<br>LSE | soft_int3<br>_set | CPU 软中断 3 置位配置寄存器。  0: 置位无效;  1: 置位有效。 | 0x0       |

| 2    | W1_PU<br>LSE | soft_int2<br>_set | CPU 软中断 2 置位配置寄存器。  0: 置位无效;  1: 置位有效。 | 0x0       |

| 1    | W1_PU<br>LSE | soft_int1<br>_set | CPU 软中断 1 置位配置寄存器。  0: 置位无效;  1: 置位有效。 | 0x0       |

| 0    | W1_PU<br>LSE | soft_int0<br>_set | CPU 软中断 0 置位配置寄存器。                     | 0x0       |

用户指南 2 系统

| Bits | Access | Name | Description | Reset |

|------|--------|------|-------------|-------|

|      |        |      | 0: 置位无效;    |       |

|      |        |      | 1: 置位有效。    |       |

## SOFT\_INT\_CLR

SOFT\_INT\_CLR 为 CPU 软中断清除寄存器。

Offset Address: 0x0158 Total Reset Value: 0x00000000

| Bits | Access       | Name              | Description                          | Reset     |

|------|--------------|-------------------|--------------------------------------|-----------|

| 31:4 | RO           | reserve<br>d      | 保留。                                  | 0x0000000 |

| 3    | W1_PU<br>LSE | soft_int<br>3_clr | CPU 软中断 3 清除配置寄存器。 0: 清除无效; 1: 清除有效。 | 0x0       |

| 2    | W1_PU<br>LSE | soft_int<br>2_clr | CPU 软中断 2 清除配置寄存器。 0: 清除无效; 1: 清除有效。 | 0x0       |

| 1    | W1_PU<br>LSE | soft_int<br>1_clr | CPU 软中断 1 清除配置寄存器。 0: 清除无效; 1: 清除有效。 | 0x0       |

| 0    | W1_PU<br>LSE | soft_int<br>0_clr | CPU 软中断 0 清除配置寄存器。 0: 清除无效; 1: 清除有效。 | 0x0       |

## SOFT\_INT\_STS

SOFT\_INT\_STS 为 CPU 软中断查询寄存器。

Offset Address: 0x015C Total Reset Value: 0x00000000

| Bits | Access | Name              | Description                            | Reset     |

|------|--------|-------------------|----------------------------------------|-----------|

| 31:4 | RO     | reserve<br>d      | 保留。                                    | 0x0000000 |

| 3    | RO     | soft_int<br>3_sts | CPU 软中断 3 状态查询寄存器。  0: 中断无效;  1: 中断有效。 | 0x0       |

| 2    | RO     | soft_int<br>2_sts | CPU 软中断 2 状态查询寄存器。  0:中断无效;  1:中断有效。   | 0x0       |

| 1    | RO     | soft_int<br>1_sts | CPU 软中断 1 状态查询寄存器。  0:中断无效;  1:中断有效。   | 0x0       |

| 0    | RO     | soft_int<br>0_sts | CPU 软中断 0 状态查询寄存器。 0:中断无效; 1:中断有效。     | 0x0       |

## 2.7 RTC

## 2.7.1 概述

RTC 的功能主要是实现定时、计数功能,可以供操作系统用作系统时钟,也可以供应用程序用作定时和计数。

# 2.7.2 功能描述

RTC 具有以下功能特点:

- 48bit 位宽的 free running 递加计数器。

- 计数器上电解复位后即开始计数,无需任何使能配置。

- 计数时钟为 32kHz 时钟。

- 支持配置中断产生寄存器阈值, 计数器递加到阈值时产生中断。

- 支持计数器值实时读取。

## 2.8 Timer

用户指南

## 2.8.1 概述

芯片中有3个相同且可独立配置的定时器(Timer),主要实现定时、计数功能的IP,可供程序用作定时和计数。

## 2.8.2 功能描述

Timer 具有以下功能特点:

- 3 个 32bit 的可独立配置的 Timer 单元。

- 每个 Timer 单元支持三种工作模式:

one-shot 模式:加载配置值到计数器,进行递减计数,递减到0后停止计数。 periodic 模式: Timer 持续计数,加载配置值到计数器,进行递减计数,递减到0 后再次载入配置值并继续递减计数。

free running 模式: Timer 持续计数, 计数器起始值为 0xFFFF\_FFFF, 进行递减计数, 递减到 0 后再次载入 0xFFFF\_FFF 并继续递减计数。

● 每个 Timer 单元支持独立使能。

## 2.9 看门狗

## 2.9.1 概述

WatchDog 用于系统异常恢复,如果未得到更新则隔一定时间(可编程)产生一个系统复位信号,当 WatchDog 在此之前关闭工作时钟或更新计数器,复位信号不会产生。

## 2.9.2 功能描述

用户指南

WatchDog 内置 1 个可编程 32bit 计数器,具有以下功能特点:

- 内置计数器进行递减计数,当由预设值递减到0时产生超时。

- WatchDog 具有 2 种工作方式。

- 方式一: 如果超时,则只产生系统复位。

- 方式二:第一次超时,WatchDog产生中断;第二次超时,如果中断未被清除,WatchDog产生系统复位。

- 可配置超时间隔。

# **3** QSPI Flash 控制器

- 3.1 概述

- 3.2 功能描述

- 3.3 工作方式

- 3.4 寄存器概览

- 3.5 寄存器描述

## 3.1 概述

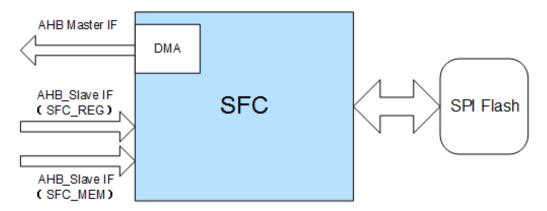

SFC 是一个 SPI Flash 控制器。业务侧提供一个 AHB(Advanced High Performance Bus) Slave 接口,主要完成 AHB 通道对 SPI Flash 的访问控制功能;提供一个 AHB Master 接口,用于 DMA 方式读写 Flash。

图3-1 SFC 应用框图

注: IF (Interface)。

## 3.2 功能描述

用户指南

#### AHB Slave 接口

#### AHB Slave 接口具有以下特点:

- 提供一个 AHB Slave 接口,可以根据不同的选择信号访问内部配置寄存器或直接 访问 SPI Flash Memory。

- 支持 AMBA2.0 协议。

- 仅支持小端 (Little-Endian)。

#### AHB Master 接口

#### AHB Master 接口具有以下特点:

- 提供一个 AHB Master 接口,用于 DMA 方式在内存和 Flash 之间搬运数据。

- 支持 AMBA2.0 协议。

- 只支持小端。

- 支持 Single、INCR、INCR4、INCR8、INCR16 传输类型。

- 不支持 Early Termination。

- 支持总线 Lock 传输。

#### 存储器接口

#### 存储器接口具有以下特点:

- 片选的存储空间最大支持到 64Mbit (3Byte 地址模式)。片选映射基地址可配置。

只支持片选 1,不支持片选 0。

- 支持 Standard SPI、Dual-Output/Dual-Input SPI、Quad-Output/Quad-Input SPI、Dual-I/O SPI、Quad-I/O SPI 五种接口类型。上电后默认支持 Standard SPI 接口类型,可通过寄存器配置切换接口类型。

- 支持 XIP (Executed In Place)。

- SPI Flash 读写操作支持总线直接读写、寄存器编程读写、DMA 读写三种方式。

- 支持多种写保护操作。

- SFC 模块支持 SPI Mode0 和 Mode3,按协议要求,支持 SPI Mode0 和 Mode3

的 SPI Flash 器件在时钟的上升沿采样数据,在时钟的下降沿输出数据。

- XIP 实现地址 remap,为了软件只编译一个 XIP 镜像,升级镜像时主镜像和备份 镜像使用相同地址。

#### Flash 数据在线解密

Flash 数据在线解密具有以下特点:

- 解密算法为 AES-128-CTR, 仅支持 1 个 IV, 秘钥来源于 KM 派生。

- 支持 4 个解密区域,配置粒度为 256Byte;每个区域支持单独的 IV 解密起始地址可配,配置粒度同为 256Byte,4 个解密区域配置不能存在交叉地址。

#### □□说明

支持 AES 在线解密,解密时读取数据量没有 16Byte 的倍数与对齐的约束。

## 3.3 工作方式

## 3.3.1 读写 Flash

有三种方式读写 Flash:

- 通过寄存器配置方式发送 SPI Flash Program、Read 等命令来读写 Flash。例如:对寄存器 CMD\_CONFIG 写 0x0000\_7F8B,对寄存器 CMD\_INS 写 0x03,表示通过 Standard SPI 方式发起读 64Byte Flash 数据的操作。

- 此方式直接控制需要发送的 Flash 命令。

- 通过 AHB Slave 接口以类似读写普通 Memory 的方式读写 Flash。

SFC 模块会自动将 AHB 总线的读写操作时序映射为 SPI Flash 读写命令。

- 通过 DMA 方式在 Flash 和外部 Memory 之间搬移数据。

## 3.3.2 其他操作

对 Flash 的其他操作如 Erase、进入 Deep Power Down、读 Device ID 等必须通过寄存器访问来实现。需要配置 CMD\_INS[REG\_INS]为相应的命令,具体请参见 Flash 器件手册。

例如:对寄存器 CMD\_CONFIG 写 0x0000\_0583,对寄存器 CMD\_INS 写 0x0000 009F,表示读器件 ID 的操作。

# 3.3.3 初始化流程

用户指南

### 须知

注意以下初始化流程仅做参考,请根据器件差异进行调整。

### 初始化流程如下:

步骤 1 (如果需要调整 Timing 参数) 配置 TIMING 寄存器。

### 步骤 2 配置总线操作方式寄存器。

- 根据实际 Flash 大小配置 BUS\_FLASH\_SIZE[flash\_size\_cs1] (直接获知器件大小或可通过发 Read ID 命令给 Flash 查询获得)。

- 有些器件要求进入非 Standard SPI 读写时序,需要预先以特殊命令配置 Flash。

根据器件需要,对寄存器 CMD INS 进行写操作,发特定命令配置 Flash。

- 通过 BUS\_CONFIG1/BUS\_CONFIG2 配置总线读写操作指令和参数。

例如:对寄存器 BUS\_CONFIG1 写 0xCC85\_EB1E 表示配置的参数为写指令 32h,写方式为 Quad-Input SPI,读指令 EBh、读方式为 Quad I/O SPI。

- 如果需要开启总线写操作,配置 BUS\_CONFIG1[wr\_enable]为 1,使能总线写。 默认关闭总线写功能。

### ----结束

# 3.3.4 通过寄存器方式读 Flash 操作流程

通过寄存器读取 Flash 的操作流程 (查询方式), 如图 3-2 所示。

# 开始 IDLE 配置CMD\_INS寄存器 配置CMD\_ADDR寄存器 配置CMD\_CONFIG寄存器 读CMD\_CONFIG寄存器 本 CMD\_CONFIG[start]=0? 本 根据data\_cnt读取寄存器 CMD\_DATABUF\_N 结束

图3-2 通过寄存器读取 Flash 的操作流程 (查询方式)

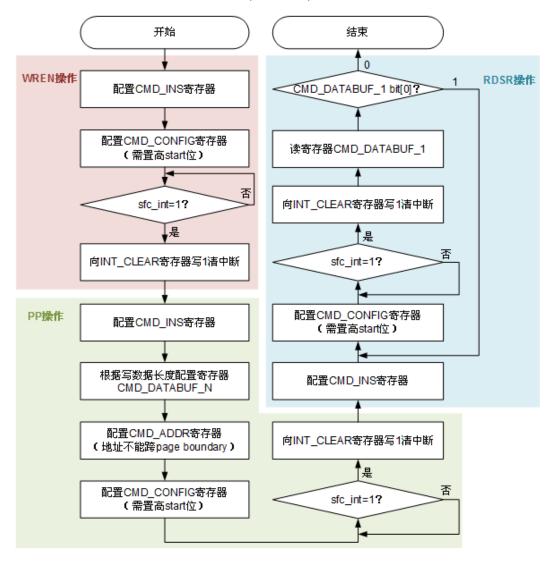

# 3.3.5 通过寄存器方式写 Flash 操作流程

### 须知

- 通过寄存器方式写 Flash 数据时,总线和 DMA 不得访问 Flash。

- 单次写 Flash 不能跨越 Page 边界(寄存器写方式没有跨越 Page 边界保护,需要软件保证,如果跨越 256Byte 边界,将会 Wrap 到该 Page 的起始地址,覆盖原来的内容)。

通过寄存器写 Flash 的操作流程 (中断方式), 如图 3-3 所示。

图3-3 通过寄存器写 Flash 的操作流程 (中断方式)

注: WREN (Write Read Enable), PP (Page Program), RDSR (Read Status Register)。

# 3.3.6 通过寄存器方式其他操作流程

通过寄存器方式其他操作流程如图 3-4 所示。

### 开始 结束 根据写数据长度配置寄存器 配置CMD\_INS寄存器 CMD DATABUF N 是 否 否 有无地址? 有无数据读回? 是 向INT\_CLEAR寄存器写1清中断 配置CMD\_ADDR寄存器 是 否 否 有无写入数据? CMD CONFIG[start]=0? 是, 根据写数据长度配置寄存器 配置CMD CONFIG寄存器 CMD DATABUF N (并置高start位)

### 图3-4 通过寄存器方式其他操作流程

### □ 说明

SFC 控制器不支持发出 "OPCODE (1byte) + DUMMY (3byte 全 0)" 组合 SPI 时序,某些 Flash 指令需要这种组合时序时,可以采用 "OPCODE (1byte) + ADDR (3byte 全 0)"组合代替。

## 3.3.7 通过 AHB Slave 直接读写 Flash 操作流程

上电复位后,默认配置为 Standard SPI 时序模式。不需要额外配置,可直接读Flash。

默认通过 AHB Slave 写 Flash 是禁止的。需要配置 BUS\_CONFIG1[wr\_enable]为 1, 使能总线写操作。

如果需要调整默认配置,请参见"3.3.3 初始化流程"。

# 3.3.8 通过 DMA 方式读写 Flash 操作流程

DMA 操作流程如下:

步骤 1 如需调整总线操作方式时序配置,请参见"3.3.3 初始化流程"。

- 步骤 2 写 BUS\_DMA\_MEM\_SADDR,配置 DMA 操作的内存端起始地址;写 BUS\_DMA\_FLASH\_SADDR,配置 Flash 端起始地址(Flash 偏移地址);写 BUS\_DMA\_LENBUS\_DMA\_LEN,配置数据长度。

- 步骤 3 写 BUS DMA CTRL,配置读写方向,选择 Flash 片选 1。

- 步骤 4 写 BUS DMA CTRL[start]为 1, 使能 DMA 操作。

- 步骤 5 等待 dma\_done 中断触发 (中断方式) 或轮询 DMA 操作完成 (BUS DMA CTRL[start]变为 0)。

### □ 说明

- DMA 操作时可以同时 Flash 寄存器读命令操作。

- DMA 操作时可以同时通过 AHB Slave 直接访问 Flash,但需保证中间不修改总线操作相关配置。

- DMA 操作时需要保证首地址 4Byte 对齐。

### ----结束

# 3.4 寄存器概览

SFC 寄存器概览如表 3-1 所示。

### 表3-1 SFC 寄存器概览 (基址是 0x4800\_0000)

| 偏移地址   | 名称             | 描述              |

|--------|----------------|-----------------|

| 0x0100 | GLOBAL_CONFIG  | 全局配置寄存器。        |

| 0x0110 | TIMING         | Timing 配置寄存器。   |

| 0x0120 | INT_RAW_STATUS | 中断原始状态寄存器。      |

| 0x0124 | INT_STATUS     | 经过屏蔽处理的中断状态寄存器。 |

| 0x0128 | INT_MASK       | 中断屏蔽寄存器。        |

| 0x012C | INT_CLEAR      | 中断清除寄存器。        |

| 0x0130 | SOFT_RST_MASK  | 软复位寄存器屏蔽位。      |

| 0x0200 | BUS_CONFIG1    | 总线操作方式配置 1 寄存器。 |

| 0x0204 | BUS_CONFIG2    | 总线操作方式配置 2 寄存器。 |

| 偏移地址             | 名称                        | 描述                              |

|------------------|---------------------------|---------------------------------|

| 0x0240           | BUS_DMA_CTRL              | DMA 操作控制寄存器。                    |

| 0x0244           | BUS_DMA_MEM_SA<br>DDR     | DMA 操作 DDR 起始地址寄存器。             |

| 0x0248           | BUS_DMA_FLASH_S<br>ADDR   | DMA 操作 Flash 起始地址寄存器。           |

| 0x024C           | BUS_DMA_LEN               | DMA 操作搬运数据长度寄存器。                |

| 0x0250           | BUS_DMA_AHB_CTR<br>L      | DMA 操作 AHB 时 burst 操作方式选择控制寄存器。 |

| 0x0300           | CMD_CONFIG                | 命令操作方式配置寄存器。                    |

| 0x0308           | CMD_INS                   | 命令操作方式指令寄存器。                    |

| 0x030C           | CMD_ADDR                  | 命令操作方式地址寄存器。                    |

| 0x0400 + 4<br>×n | CMD_DATABUF_N             | 命令操作方式数据 Buffer 寄存器。            |

| 0x1000 + 4<br>×n | APC_CFG_START_A<br>DDR    | FAPC 鉴权。                        |

| 0x1040 + 4<br>×n | APC_CFG_END_ADD<br>R      | FAPC 鉴权。                        |

| 0x1180           | SFC_FAPC_DEC_AU<br>TH_CFG | FAPC 鉴权。                        |

| 0x1200           | SFC_FAPC_SADDR_<br>STATUS | FAPC 鉴权。                        |

| 0x1204           | SFC_FAPC_EADDR_<br>STATUS | FAPC 鉴权。                        |

| 0x1208           | SFC_APC_ERR_INT           | FAPC 鉴权。                        |

| 0x120C           | SFC_APC_CLR               | FAPC 鉴权。                        |

| 0x1220           | FAPC_ONE_WAY_LO           | FAPC 鉴权锁定寄存器。                   |

| 0x1300           | LEA_LP_EN                 | LEA 控制。                         |

| 0x1304           | LEA_DFX_INFO              | LEA DFX。                        |

| 0x1600           | LEA_IV_VLD                | LEA 控制。                         |

| 偏移地址   | 名称                           | 描述                  |

|--------|------------------------------|---------------------|

| 0x1640 | LEA_IV_ACPU_STAR<br>T_ADDR_0 | LEA IV 解密起始地址寄存器 0。 |

| 0x1644 | LEA_IV_ACPU_STAR<br>T_ADDR_1 | LEA IV 解密起始地址寄存器 1。 |

| 0x1648 | LEA_IV_ACPU_STAR<br>T_ADDR_2 | LEA IV 解密起始地址寄存器 2。 |

| 0x164C | LEA_IV_ACPU_STAR<br>T_ADDR_3 | LEA IV 解密起始地址寄存器 3。 |

SFC 寄存器偏移地址中变量的取值范围和含义如表 3-2 所示。

### 表3-2 SFC 寄存器偏移地址变量表

| 变量名称 | 取值范围 | 描述               |

|------|------|------------------|

| n    | 0~3  | FLASH 解密地址的区间个数。 |

# 3.5 寄存器描述

用户指南

### GLOBAL CONFIG

GLOBAL\_CONFIG 为全局配置寄存器。

Offset Address: 0x0100 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name     | Description                                                             | Reset    |

|--------|--------|----------|-------------------------------------------------------------------------|----------|

| [31:6] | -      | reserved | 保留。                                                                     | 0x000000 |

| [5:3]  | RW     | rd_delay | SPI 读出数据延迟周期个数。 000: 0.5~1个时钟周期(默认值); 001: 1~1.5个时钟周期; 010: 1.5~2个时钟周期; | 0x0      |

|        |        |          | 011: 2~2.5 个时钟周期;<br>100: 2.5~3 个时钟周期;                                  |          |

| Bits | Access | Name                | Description                                                                 | Reset |

|------|--------|---------------------|-----------------------------------------------------------------------------|-------|

|      |        |                     | 101: 3~3.5 个时钟周期;                                                           |       |

|      |        |                     | 110: 3.5~4 个时钟周期;                                                           |       |

|      |        |                     | 111: 不支持, (按照 "110" 含<br>义处理)。                                              |       |

| [2]  | RW     | flash_addr_mo<br>de | SPI 地址模式。 0: 3byte 寻址模式(默认值); 1: 4byte 寻址模式。 注意: CMD_CONFIG[start]为 1 时写无效。 | 0x0   |

| [1]  | RW     | wp_en               | 硬件写保护使能(写保护管脚)。<br>0:禁止;<br>1:使能。                                           | 0x0   |

| [0]  | RW     | mode                | SPI 模式设置。<br>0:支持 Mode0;<br>1:支持 Mode3。                                     | 0x0   |

### **TIMING**

TIMING 为 Timing 配置寄存器。

Offset Address: 0x0110 Total Reset Value: 0x0000\_660F

| Bits    | Access | Name     | Description         | Reset   |

|---------|--------|----------|---------------------|---------|

| [31:15] | -      | reserved | 保留。                 | 0x00000 |

| [14:12] | RW     | tcsh     | 片选保持时间。             | 0x6     |

|         |        |          | 0x0~0x7: (n+1) 个时钟周 |         |

|         |        |          | 期。                  |         |

|         |        |          | 例如:0x6 表示 7 个时钟周    |         |

|         |        |          | 期。                  |         |

| [11]    | -      | reserved | 保留。                 | 0x0     |

| Bits   | Access | Name     | Description                                                          | Reset |

|--------|--------|----------|----------------------------------------------------------------------|-------|

| [10:8] | RW     | tcss     | 片选建立时间。 0x0~0x7: (n+1) 个时钟周期。 例如: 0x6表示7个时钟周期。                       | 0x6   |

| [7:4]  | -      | reserved | 保留。                                                                  | 0x0   |

| [3:0]  | RW     | tshsl    | 设置 2 次 Flash 操作之间的时间间隔。  0x0~0xF: (n+2) 个时钟周期。  例如: 0xF 表示 17 个时钟周期。 | 0xF   |

# INT\_RAW\_STATUS

INT\_RAW\_STATUS 为中断原始状态寄存器。

Offset Address: 0x0120 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                        | Description                                  | Reset      |

|--------|--------|-----------------------------|----------------------------------------------|------------|

| [31:2] | -      | reserved                    | 保留。                                          | 0x00000000 |

| [1]    | RO     | dma_done_int_<br>raw_status | DMA 操作完成中断原始状态(未经过屏蔽)。<br>0:未完成;<br>1:已完成。   | 0x0        |

| [0]    | RO     | cmd_op_end_r<br>aw_status   | 指令操作结束原始中断状态<br>(未经过屏蔽)。<br>0:未完成;<br>1:已完成。 | 0x0        |

# INT\_STATUS

INT\_STATUS 为经过屏蔽处理的中断状态寄存器。

Offset Address: 0x0124 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                    | Description                                | Reset      |

|--------|--------|-------------------------|--------------------------------------------|------------|

| [31:2] | -      | reserved                | 保留。                                        | 0x00000000 |

| [1]    | RO     | dma_done_int_st<br>atus | DMA 操作完成中断原始状态 (经过屏蔽)。<br>0:未完成;<br>1:已完成。 | 0x0        |

| [0]    | RO     | cmd_op_end_sta<br>tus   | 指令操作结束中断状态<br>(经过屏蔽)。<br>0:未完成;<br>1:已完成。  | 0x0        |

# INT\_MASK

INT\_MASK 为中断屏蔽寄存器。

Offset Address: 0x0128 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                    | Description    | Reset      |

|--------|--------|-------------------------|----------------|------------|

| [31:2] | -      | reserved                | 保留。            | 0x00000000 |

| [1]    | RW     | dma_done_<br>int mask   | DMA 操作完成中断屏蔽位。 | 0x0        |

|        |        |                         | 0: 屏蔽;         |            |

|        |        |                         | 1:不屏蔽。         |            |

| [0]    | RW     | cmd_op_en<br>d int mask | 指令操作结束中断屏蔽位。   | 0x0        |

|        |        | u_me_maon               | 0: 屏蔽;         |            |

|        |        |                         | 1:不屏蔽。         |            |

# INT\_CLEAR

INT\_CLEAR 为中断清除寄存器。

Offset Address: 0x012C Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                   | Description                                                                                                                              | Reset      |

|--------|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------|

| [31:2] | -      | reserved               | 保留。                                                                                                                                      | 0x00000000 |

| [1]    | WO     | dma_done_in<br>t_clr   | DMA 操作完成中断清除位,向该位写 1 将清除 INT_STATUS[dma_done_int_st atus]和 INT_RAW_STATUS[dma_done_int_raw_status]。 0: 不清除; 1: 清除。 注意: 清除操作完成后该位自动 返回 0。 | 0x0        |

| [0]    | WO     | cmd_op_end<br>_int_clr | 指令操作结束中断清除位,向该位写 1 将清除INT_STATUS[cmd_op_end_status]和INT_RAW_STATUS[cmd_op_end_raw_status]。 0: 不清除; 1: 清除。 注意:清除操作完成后该位自动返回 0。            | 0x0        |

### SOFT\_RST\_MASK

SOFT\_RST\_MASK 为软复位寄存器屏蔽位

Offset Address: 0x0130 Total Reset Value: 0x0000\_0001

| Bits   | Access | Name     | Description | Reset          |

|--------|--------|----------|-------------|----------------|

| [31:1] | -      | reserved | 保留。         | 0x000000<br>00 |

| Bits | Access | Name                  | Description                                        | Reset |

|------|--------|-----------------------|----------------------------------------------------|-------|

| [0]  | RW     | sfc_bus_soft_rst_mask | SFC 总线时钟域数字逻辑软复位屏蔽位: 0: 软复位可以正常生效; 1: 软复位被屏蔽,不会生效。 | 0x1   |

# BUS\_CONFIG1

BUS\_CONFIG1 为总线操作方式配置 1 寄存器。

Offset Address: 0x0200 Total Reset Value: 0x8080\_0300

| Bits    | Access | Name           | Description           | Reset |

|---------|--------|----------------|-----------------------|-------|

| [31]    | RW     | rd_enable      | 总线读使能。                | 0x1   |

|         |        |                | 0: 禁止;                |       |

|         |        |                | 1: 使能。                |       |

| [30]    | RW     | wr_enable      | 总线写使能。                | 0x0   |

|         |        |                | 0: 禁止;                |       |

|         |        |                | 1: 使能。                |       |

| [29:22] | RW     | wr_ins         | 写指令。                  | 0x02  |

| [21:19] | RW     | wr_dummy_bytes | 总线写操作 DummyByte。      | 0x0   |

|         |        |                | 000: 没有 DummyByte;    |       |

|         |        |                | 001: 1Byte;           |       |

|         |        |                | 010: 2Byte;           |       |

|         |        |                |                       |       |

|         |        |                | 111: 7Byte。           |       |

| [18:16] | RW     | wr_mem_if_type | 总线写操作指定连接的 SPI        | 0x0   |

|         |        |                | FLASH 接口类型。           |       |

|         |        |                | 000: Standard SPI 接口类 |       |

|         |        |                | 型;                    |       |

| Bits   | Access | Name            | Description                          | Reset |

|--------|--------|-----------------|--------------------------------------|-------|

|        |        |                 | 001: Dual-Input/Dual-Output          |       |

|        |        |                 | SPI;                                 |       |

|        |        |                 | 010: Dual-I/O SPI;                   |       |

|        |        |                 | 011: Full DIO SPI;                   |       |

|        |        |                 | 100: 保留;                             |       |

|        |        |                 | 101: Quad-Input/Dual-<br>Output SPI; |       |

|        |        |                 | 110: Quad-I/O SPI;                   |       |

|        |        |                 | 111: Full QIO SPI。                   |       |

| [15:8] | RW     | rd_ins          | 读指令。                                 | 0x03  |

| [7:6]  | RW     | rd_prefetch_cnt | 总线访问 Flash 方式(非定长<br>读)预取周期。         | 0x0   |

|        |        |                 | 00: 不预取(默认值);                        |       |

|        |        |                 | 01: 预取 1 个时钟周期数                      |       |

|        |        |                 | 据;                                   |       |

|        |        |                 | 10: 预取 2 个时钟周期数                      |       |

|        |        |                 | 据;                                   |       |

|        |        |                 | 11: 预取 3 个时钟周期数                      |       |

|        |        |                 | 据。                                   |       |

| [5:3]  | RW     | rd_dummy_bytes  | 总线读操作 DummyByte。                     | 0x0   |

|        |        |                 | 00: 没有 DummyByte;                    |       |

|        |        |                 | 001: 1Byte                           |       |

|        |        |                 | 010: 2Byte;                          |       |

|        |        |                 |                                      |       |

|        |        |                 | 111: 7Byte。                          |       |

| [2:0]  | RW     | rd_mem_if_type  | 总线读操作指定连接的 SPI                       | 0x0   |

|        |        |                 | FLASH 接口类型。                          |       |

|        |        |                 | 000: Standard SPI接口类型;               |       |

|        |        |                 | 001: Dual-Input/Dual-Output          |       |

| Bits | Access | Name | Description           | Reset |

|------|--------|------|-----------------------|-------|

|      |        |      | SPI;                  |       |

|      |        |      | 010: Dual-I/O SPI;    |       |

|      |        |      | 101: Quad-Input/Dual- |       |

|      |        |      | Output SPI;           |       |

|      |        |      | 110: Quad-I/O SPI;    |       |

|      |        |      | 其他:保留。                |       |

# BUS\_CONFIG2

BUS\_CONFIG2 为总线操作方式配置 2 寄存器。

Offset Address: 0x0204 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name       | Description                                 | Reset      |

|--------|--------|------------|---------------------------------------------|------------|

| [31:3] | -      | reserved   | 保留。                                         | 0x00000000 |

| [2:0]  | RW     | wip_locate | WIP(Write In Progress)位于<br>Flash 状态寄存器的位置。 | 0x0        |

|        |        |            | 000: WIP 位于 Flash 状态寄存<br>器的 bit[0](默认值);   |            |

|        |        |            | 001: WIP 位于 Flash 状态寄存<br>器的 bit[1];        |            |

|        |        |            | 010: WIP 位于 Flash 状态寄存<br>器的 bit[2];        |            |

|        |        |            | 011: WIP 位于 Flash 状态寄存<br>器的 bit[3];        |            |

|        |        |            | 100: WIP 位于 Flash 状态寄存<br>器的 bit[4];        |            |

|        |        |            | 101: WIP 位于 Flash 状态寄存<br>器的 bit[5];        |            |

|        |        |            | 110: WIP 位于 Flash 状态寄存<br>器的 bit[6];        |            |

|        |        |            | 111: WIP 位于 Flash 状态寄存                      |            |

| Е | Bits | Access | Name | Description | Reset |

|---|------|--------|------|-------------|-------|

|   |      |        |      | 器的 bit[7]。  |       |

# BUS\_DMA\_CTRL

BUS\_DMA\_CTRL 为 DMA 操作控制寄存器。

Offset Address: 0x0240 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name       | Description    | Reset     |

|--------|--------|------------|----------------|-----------|

| [31:5] | -      | reserved   | 保留。            | 0x0000000 |

| [4]    | RW     | dma_sel_cs | DMA 操作指定片选。    | 0x0       |

|        |        |            | 0: 片选 0;       |           |

|        |        |            | 1: 片选 1。       |           |

| [3:2]  | -      | reserved   | 保留。            | 0x0       |

| [1]    | RW     | dma_rw     | DMA 读写指示。      | 0x0       |

|        |        |            | 0: 写操作;        |           |

|        |        |            | 1: 读操作。        |           |

| [0]    | RW     | dma_start  | DMA 传输使能控制。    | 0x0       |

|        |        |            | 0: 无操作;        |           |

|        |        |            | 1: 开始 DMA 操作。  |           |

|        |        |            | 注意:DMA 传输完成自动回 |           |

|        |        |            | 0.             |           |

# BUS\_DMA\_MEM\_SADDR

BUS\_DMA\_MEM\_SADDR 为 DMA 操作芯片内存起始地址寄存器。

Offset Address: 0x0244 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name              | Description         | Reset      |

|--------|--------|-------------------|---------------------|------------|

| [31:0] | RW     | dma_mem_sad<br>dr | DMA 操作 memory 起始地址。 | 0x00000000 |

| Bits | Access | Name | Description     | Reset |

|------|--------|------|-----------------|-------|

|      |        |      | Q353333 配置值应在   |       |

|      |        |      | 0x0010_0000~    |       |

|      |        |      | 0x00BF_FFFF 之间。 |       |

### BUS\_DMA\_FLASH\_SADDR

BUS\_DMA\_FLASH\_SADDR为 DMA 操作 Flash 起始地址寄存器。

Offset Address: 0x0248 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name            | Description        | Reset      |

|--------|--------|-----------------|--------------------|------------|

| [31:0] | RW     | dma_flash_saddr | DMA 操作 Flash 起始地址。 | 0x00000000 |

### BUS\_DMA\_LEN

BUS\_DMA\_LEN 为 DMA 操作搬运数据长度寄存器。

Offset Address: 0x024C Total Reset Value: 0x0000\_0000

| Bits    | Access | Name     | Description                                           | Reset      |

|---------|--------|----------|-------------------------------------------------------|------------|

| [31:30] | -      | reserved | 保留。                                                   | 0x0        |

| [29:0]  | RW     | dma_len  | DMA 操作数据搬运长度(n+1),<br>单位: byte。<br>例如: 6 表示长度为 7byte。 | 0x00000000 |

### BUS\_DMA\_AHB\_CTRL

BUS\_DMA\_AHB\_CTRL为 DMA 操作 AHB 时 burst 操作方式选择控制寄存器。

Offset Address: 0x0250 Total Reset Value: 0x0000\_0007

| Bits   | Access | Name      | Description       | Reset      |

|--------|--------|-----------|-------------------|------------|

| [31:3] | -      | reserved  | 保留。               | 0x00000000 |

| [2]    | RW     | incr16_en | INC16 burst 类型使能。 | 0x1        |

|        |        |           | 0: 禁止;            |            |

| Bits | Access | Name     | Description      | Reset |

|------|--------|----------|------------------|-------|

|      |        |          | 1: 使能。           |       |

| [1]  | RW     | incr8_en | INC8 burst 类型使能。 | 0x1   |

|      |        |          | 0: 禁止;           |       |

|      |        |          | 1: 使能。           |       |

| [0]  | RW     | incr4_en | INC4 burst 类型使能。 | 0x1   |

|      |        |          | 0: 禁止;           |       |

|      |        |          | 1: 使能。           |       |

# CMD\_CONFIG

CMD\_CONFIG 为命令操作方式配置寄存器。

Offset Address: 0x0300 Total Reset Value: 0x0000\_7E00

| Bits    | Access | Name        | Description                                                                                                                                                            | Reset |

|---------|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| [31:20] | -      | reserved    | 保留。                                                                                                                                                                    | 0x000 |

| [19:17] | RW     | mem_if_type | 指定寄存器命令操作方式连接的 SPI FLASH 接口类型。 000: Standard SPI 接口类型; 001: Dual-Input/Dual-Output SPI; 010: Dual-I/O SPI; 101: Quad-Input/Dual-Output SPI; 110: Quad-I/O SPI; 其他: 保留。 | 0x0   |

| [16:15] | -      | reserved    | 保留。                                                                                                                                                                    | 0x0   |

| [14:9]  | RW     | data_cnt    | 读写数据长度(单位:<br>Byte)。<br>0x00~0x3F: (n+1) Byte。                                                                                                                         | 0x3F  |

| Bits  | Access | Name               | Description                                                                 | Reset |

|-------|--------|--------------------|-----------------------------------------------------------------------------|-------|

|       |        |                    | 例如: 0x3F 表示 64Byte。                                                         |       |

| [8]   | RW     | rw                 | 标识此次操作数据读写,需<br>[data_en]为 1。<br>0:写,有发送数据;<br>1:读,有返回数据。                   | 0x0   |

| [7]   | RW     | data_en            | 标识此次操作是否有数据。<br>0:无数据;<br>1:有数据。                                            | 0x0   |

| [6:4] | RW     | dummy_byte_<br>cnt | 寄存器命令操作方式 DummyByte。 000: 没有 DummyByte; 001: 1Byte; 010: 2Byte; 111: 7Byte。 | 0x0   |

| [3]   | RW     | addr_en            | 此次操作是否有地址。<br>0:无地址;<br>1:有地址。                                              | 0x0   |

| [2]   | -      | reserved           | 保留。                                                                         | 0x0   |

| [1]   | RW     | sel_cs             | 片选选择操作。 0:选择片选 0 进行操作; 1:选择片选 1 进行操作。                                       | 0x0   |

| [0]   | RW     | start              | 标识指令操作开始。 0: 结束; 1: 开始。 注意: 此次操作完成后该位自动回 0。                                 | 0x0   |

# CMD\_INS

CMD\_INS 为命令操作方式指令寄存器。

Offset Address: 0x0308 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name     | Description          | Reset    |

|--------|--------|----------|----------------------|----------|

| [31:8] | -      | reserved | 保留。                  | 0x000000 |

| [7:0]  | RW     | reg_ins  | 寄存器访问 Flash 方式下的指令码。 | 0x00     |

### CMD ADDR

CMD\_ADDR 为命令操作方式地址寄存器。

Offset Address: 0x030C Total Reset Value: 0x0000\_0000

| Bits    | Access | Name     | Description           | Reset      |

|---------|--------|----------|-----------------------|------------|

| [31:30] | -      | reserved | 保留。                   | 0x0        |

| [29:0]  | RW     | cmd_addr | 寄存器访问 Flash 方式下的操作地址。 | 0x00000000 |

# CMD\_DATABUF\_N

CMD\_DATABUF\_N 为命令操作方式数据 Buffer 寄存器。

Offset Address: 0x0400 + 4×n Total Reset Value: 0x0000\_0000

| Bits   | Access | Name              | Description                               | Reset     |

|--------|--------|-------------------|-------------------------------------------|-----------|

| [31:0] | RW     | cmd_databuf_<br>n | 寄存器访问 Flash 方式下第 n<br>数据 Buffer(n: 0~15)。 | 0x0000000 |

### APC\_CFG\_START\_ADDR

APC\_CFG\_START\_ADDR 为 FAPC 鉴权。

Offset Address: 0x1000 + 4×n Total Reset Value: 0x0000\_0000

| Bits | Access | Name | Description | Reset |

|------|--------|------|-------------|-------|

|------|--------|------|-------------|-------|

| Bits   | Access | Name                     | Description                                                                                 | Reset    |

|--------|--------|--------------------------|---------------------------------------------------------------------------------------------|----------|

| [31:8] | RW     | apc_cfg_sta<br>rt_addr_n | flash 存储区域划分 4 段地址区间,每段起始和截止地址位宽32bit,该寄存器表示第 n 段起始地址的高 24bit (n: 0~3)。 注意:该处为绝对地址,包含总线基地址。 | 0x000000 |

| [7:0]  | -      | reserved                 | 保留。                                                                                         | 0x00     |

# APC\_CFG\_END\_ADDR

APC\_CFG\_END\_ADDR 为 FAPC 鉴权。

Offset Address: 0x1040 + 4×n Total Reset Value: 0x0000\_0000

| Bits   | Access | Name               | Description                                                                               | Reset    |

|--------|--------|--------------------|-------------------------------------------------------------------------------------------|----------|

| [31:8] | RW     | apc_cfg_end_addr_n | flash 存储区域划分 4 段地址区间,每段起始和截止地址位宽 32bit,该寄存器表示第 n 段截止地址的高24bit (n: 0~3) 注:该处为绝对地址,包含总线基地址。 | 0x000000 |

| [7:0]  | -      | reserved           | 保留。                                                                                       | 0x00     |

# SFC\_FAPC\_DEC\_AUTH\_CFG

SFC\_FAPC\_DEC\_AUTH\_CFG 为 FAPC 鉴权。

Offset Address: 0x1180 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                      | Description                                               | Reset      |

|--------|--------|---------------------------|-----------------------------------------------------------|------------|

| [31:0] | RW     | sfc_fapc_dec<br>_auth_cfg | flash 存储区域划分 4 段区<br>间,该寄存器从低位开始,每<br>2bit(n: 0~3)表示一段区间的 | 0x00000000 |

| Bits | Access | Name | Description | Reset |

|------|--------|------|-------------|-------|

|      |        |      | 数据处理方式:     |       |

|      |        |      | 0b00: 透传;   |       |

|      |        |      | 0b10: 解密;   |       |

|      |        |      | 其他:保留。      |       |

# SFC\_FAPC\_SADDR\_STATUS

SFC\_FAPC\_SADDR\_STATUS 为 FAPC 鉴权。

Offset Address: 0x1200 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                      | Description                                              | Reset      |

|--------|--------|---------------------------|----------------------------------------------------------|------------|

| [31:0] | RO     | sfc_fapc_sad<br>dr_status | APC 状态检测寄存器:基于 burst 起始地址检测 [31:31]:是否出现过鉴权不通过 历史态;      | 0x00000000 |

|        |        |                           | [30:28]: 当前 master 对应 MID<br>的低 3bit;                    |            |

|        |        |                           | [27:27]: 1 表示当前是写操作,<br>0 表示读;<br>[26:0]: 当前访问 flash 地址。 |            |

# SFC\_FAPC\_EADDR\_STATUS

SFC\_FAPC\_EADDR\_STATUS 为 FAPC 鉴权。

Offset Address: 0x1204 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                      | Description                    | Reset      |

|--------|--------|---------------------------|--------------------------------|------------|

| [31:0] | RO     | sfc_fapc_ead<br>dr_status | APC 状态检测寄存器:基于<br>burst 结束地址检测 | 0x00000000 |

|        |        |                           | [31:31]: 是否出现过鉴权不通过历史态;        |            |

|        |        |                           | [30:28]: 当前 master 对应 MID      |            |

| Bits | Access | Name | Description                    | Reset |

|------|--------|------|--------------------------------|-------|

|      |        |      | 的低 3bit;                       |       |

|      |        |      | [27:27]: 1 表示当前是写操作,<br>0 表示读; |       |

|      |        |      | [26:0]:当前访问 flash 地址。          |       |

# SFC\_APC\_ERR\_INT

SFC\_APC\_ERR\_INT 为 FAPC 鉴权

Offset Address: 0x1208 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name            | Description     | Reset      |

|--------|--------|-----------------|-----------------|------------|

| [31:1] | -      | reserved        | 保留。             | 0x00000000 |

| [0]    | RO     | sfc_apc_err_int | 鉴权错误中断状态:       | 0x0        |

|        |        |                 | 0: 鉴权全部通过;      |            |

|        |        |                 | 1: 出现鉴权不通过, 上报中 |            |

|        |        |                 | 断。              |            |

# SFC\_APC\_CLR

SFC\_APC\_CLR 为 FAPC 鉴权

Offset Address: 0x120C Total Reset Value: 0x0000 0000

| Bits   | Access   | Name            | Description               | Reset      |

|--------|----------|-----------------|---------------------------|------------|

| [31:1] | -        | reserved        | 保留。                       | 0x00000000 |

| [0]    | W1_PULSE | sfc_apc_<br>clr | 鉴权错误中断状态清除:               | 0x0        |

|        |          |                 | 0: 无效;                    |            |

|        |          |                 | 1: 清除 sfc_apc_err_int 中断。 |            |

# FAPC\_ONE\_WAY\_LOCK

FAPC\_ONE\_WAY\_LOCK 为 FAPC 鉴权锁定寄存器

Offset Address: 0x1220 Total Reset Value: 0x0000\_0000

| Bits    | Access | Name                     | Description                                                              | Reset  |

|---------|--------|--------------------------|--------------------------------------------------------------------------|--------|

| [31:16] | -      | reserved                 | 保留。                                                                      | 0x0000 |

| [15:0]  | RW     | sfc_fpac_one<br>way_lock | 鉴权寄存器锁定位,bit0~3分别表示16段地址区间对应的鉴权寄存器锁定位。 0:对应鉴权寄存器可读可写; 1:对应鉴权寄存器不可改写,只能读。 | 0x0000 |

|         |        |                          | 注意: 默认值是 0, 一旦写 1,<br>只有整 harden 复位才能归 0。                                |        |

### LEA\_LP\_EN

### LEA\_LP\_EN 为 LEA 控制

Offset Address: 0x1300 Total Reset Value: 0x0000\_0001

| Bits   | Access | Name      | Description     | Reset      |

|--------|--------|-----------|-----------------|------------|

| [31:1] | -      | reserved  | 保留。             | 0x00000000 |

| [0]    | RW     | lea_lp_en | AES 模块低功耗模式配置:  | 0x1        |

|        |        |           | 0:关闭 LEA 低功耗配置; |            |

|        |        |           | 1:使能 LEA 低功耗。   |            |

### LEA DFX INFO

LEA\_DFX\_INFO is LEA DFX

Offset Address: 0x1304 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name         | Description         | Reset      |

|--------|--------|--------------|---------------------|------------|

| [31:0] | RO     | lea_dfx_info | AES 模块 DFX 信息观测寄存器。 | 0x00000000 |

### LEA IV VLD

用户指南

LEA\_IV\_VLD 为 LEA 控制。

Offset Address: 0x1600 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name       | Description                                       | Reset      |

|--------|--------|------------|---------------------------------------------------|------------|

| [31:1] | -      | reserved   | 保留。                                               | 0x00000000 |

| [0]    | RW     | lea_iv_vld | AES IV 值有效寄存器。                                    | 0x0        |

|        |        |            | 配置 AES_IV 之后,需要将该寄存器写 1,是配置同步生效,做完时钟同步之后,该信号自动归0。 |            |

# LEA\_IV\_ACPU\_START\_ADDR\_0

LEA\_IV\_ACPU\_START\_ADDR\_0为 LEA IV 解密起始地址寄存器 0。

Offset Address: 0x1640 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name                | Description                                                 | Reset    |

|--------|--------|---------------------|-------------------------------------------------------------|----------|

| [31:8] | RW     | iv_start_add<br>r_0 | ACPU IV 解密区域 0 的起始地址,该寄存器表示起始地址的高24bit。 注意:该处为绝对地址,包含总线基地址。 | 0x000000 |

| [7:0]  | -      | reserved            | 保留。                                                         | 0x00     |

### LEA IV ACPU START ADDR 1

LEA\_IV\_ACPU\_START\_ADDR\_1为 LEA IV 解密起始地址寄存器 1。

Offset Address: 0x1644 Total Reset Value: 0x0000\_0000

| Bits   | Access | Name            | Description         | Reset    |

|--------|--------|-----------------|---------------------|----------|

| [31:8] | RW     | iv_start_addr_1 | ACPU IV 解密区域 1 的起始地 | 0x000000 |

|        |        |                 | 址, 该寄存器表示起始地址的高     |          |

| Bits  | Access | Name     | Description               | Reset |

|-------|--------|----------|---------------------------|-------|

|       |        |          | 24bit。                    |       |

|       |        |          | 注意: 该处为绝对地址, 包含总<br>线基地址。 |       |

| [7:0] | -      | reserved | 保留。                       | 0x00  |

# LEA\_IV\_ACPU\_START\_ADDR\_2

LEA\_IV\_ACPU\_START\_ADDR\_2为 LEA IV 解密起始地址寄存器 2。

Offset Address: 0x1648 Total Reset Value: 0x0000\_0000

| Bits   | Acces<br>s | Name            | Description                                                 | Reset    |

|--------|------------|-----------------|-------------------------------------------------------------|----------|

| [31:8] | RW         | iv_start_addr_2 | ACPU IV 解密区域 2 的起始地址,该寄存器表示起始地址的高24bit。 注意:该处为绝对地址,包含总线基地址。 | 0x000000 |

| [7:0]  | -          | reserved        | 保留。                                                         | 0x00     |

# LEA\_IV\_ACPU\_START\_ADDR\_3

LEA\_IV\_ACPU\_START\_ADDR\_3为 LEA IV 解密起始地址寄存器 3。

Offset Address: 0x164C Total Reset Value: 0x0000\_0000

| Bits   | Acces<br>s | Name            | Description                                                 | Reset    |

|--------|------------|-----------------|-------------------------------------------------------------|----------|

| [31:8] | RW         | iv_start_addr_3 | ACPU IV 解密区域 3 的起始地址,该寄存器表示起始地址的高24bit。 注意:该处为绝对地址,包含总线基地址。 | 0x000000 |

| [7:0]  | -          | reserved        | 保留。                                                         | 0x00     |

# 4 WiFi /BLE & SLE 系统

- 4.1 WiFi / BLE & SLE RF

- 4.2 WiFi/BLE & SLE ABB

- 4.3 WiFi PHY

- 4.4 WiFi MAC

- 4.5 BLE/SLE

- 4.6 雷达特性

# 4.1 WiFi / BLE & SLE RF

# 4.1.1 概述

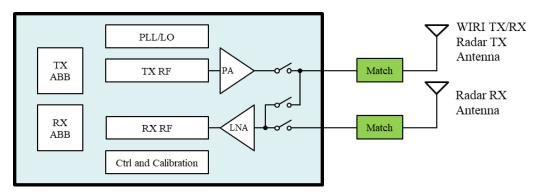

RF 部分包含 2.4G RX、TX、PLL 三个模块。支持 IEEE 802.11b/g/n/ax 20M 模式。 RF 的电路功能主要包含:

- 集成 TX/RX Switch。

- RX 通路包含 LNA、Mixer、LPF (Low Pass Filter)、VGA (Variable Gain Amplifier)。

- TX 通路包含 LPF、UPC (UP Converter)、PA (Power Amplifier)。

- 集成 PLL/LO (Local Oscillator) 通路,为信号通路提供 LO。

- 集成了 Radar 功能

### 图4-1 RF 电路模块架构

# 4.1.2 功能描述

用户指南

WiFi RF 具有以下功能特点:

- RF 电路提供稳定的 LO 信号,支持收发信号的上下变频功能。

- 支持校准功能,包含:RX DC (Direct Current)校准、TX LO Leakage 校准、TX Power 校准、TRX IQ 校准等。

# 4.1.3 RF 性能

芯片集成 2.4G WiFi/BLE/SLE 收发机,支持雷达功能。除雷达在 RFI 口接收之外,其他的功能都在 RFIO 口测试。

| 参数                | Sub-Item       | 最小值  | 典型值 | 最大值  | 単位  | 测试条件                                                                             |

|-------------------|----------------|------|-----|------|-----|----------------------------------------------------------------------------------|

| RF 工作频<br>率段      | -              | 2400 | -   | 2500 | MHz | 2401MHz 以下和<br>2483.5MHz 以上频<br>点无法满足无委会<br>辐射要求。<br>信道频率的选择需<br>要遵循协议和法规<br>要求。 |

| WIF RX<br>11b 灵敏度 | 1 Mbps<br>DSSS | -    | -99 | -98  | dBm | PER 8%, 1024<br>octet PSDU                                                       |

|                   | 2 Mbps<br>DSSS | -    | -96 | -95  | dBm |                                                                                  |

| 参数                  | Sub-Item                             | 最小值 | 典型值 | 最大值 | 单位  | 测试条件                        |

|---------------------|--------------------------------------|-----|-----|-----|-----|-----------------------------|

|                     | 5.5 Mbps<br>DSSS/CCK                 | -   | -94 | -93 | dBm |                             |

|                     | 11 Mbps<br>DSSS/CCK                  | -   | -91 | -90 | dBm |                             |

| WIF RX<br>11g 灵敏度   | BPSK,<br>R=1/2<br>(6Mbps<br>OFDM)    | -   | -96 | -95 | dBm | PER 8%, 1000<br>octets PSDU |

|                     | BPSK,<br>R=3/4<br>(9Mbps<br>OFDM)    | -   | -94 | -92 | dBm |                             |

|                     | QPSK,<br>R=1/2<br>(12Mbps<br>OFDM)   | -   | -93 | -91 | dBm |                             |

|                     | QPSK,<br>R=3/4<br>(18Mbps<br>OFDM)   | -   | -90 | -89 | dBm |                             |

|                     | 16-QAM,<br>R=1/2<br>(24Mbps<br>OFDM) | -   | -87 | -86 | dBm |                             |

|                     | 16-QAM,<br>R=3/4<br>(36Mbps<br>OFDM) | -   | -84 | -82 | dBm |                             |

|                     | 16-QAM,<br>R=1/2<br>(48Mbps<br>OFDM) | -   | -80 | -78 | dBm |                             |

|                     | 64-QAM,<br>R=3/4<br>(54Mbps<br>OFDM) | -   | -78 | -76 | dBm |                             |

| WIF RX<br>11n HT20- | HT20<br>MCS0                         | -   | -95 | -94 | dBm | BCC Long<br>PER 10%, 4096   |

| 参数                  | Sub-Item     | 最小值 | 典型值 | 最大值 | 単位  | 测试条件                                         |

|---------------------|--------------|-----|-----|-----|-----|----------------------------------------------|

| MF 灵敏度              | HT20<br>MCS1 | -   | -92 | -91 | dBm | octets PSDU                                  |

|                     | HT20<br>MCS2 | -   | -90 | -88 | dBm |                                              |

|                     | HT20<br>MCS3 | -   | -87 | -85 | dBm |                                              |

|                     | HT20<br>MCS4 | -   | -83 | -82 | dBm |                                              |

|                     | HT20<br>MCS5 | -   | -79 | -78 | dBm |                                              |

|                     | HT20<br>MCS6 | -   | -77 | -75 | dBm |                                              |

|                     | HT20<br>MCS7 | -   | -76 | -74 | dBm |                                              |

| WIF RX<br>11ac HT40 | HT40<br>MCS0 | -   | -93 | -92 | dBm | BCC Long<br>PER 10%, 4096<br>octets PSDU     |

| 灵敏度<br>             | HT40<br>MCS1 | -   | -90 | -88 | dBm |                                              |

|                     | HT40<br>MCS2 | -   | -87 | -86 | dBm |                                              |

|                     | HT40<br>MCS3 | -   | -84 | -83 | dBm |                                              |

|                     | HT40<br>MCS4 | -   | -81 | -79 | dBm |                                              |

|                     | HT40<br>MCS5 | -   | -76 | -75 | dBm |                                              |

|                     | HT40<br>MCS6 | -   | -74 | -73 | dBm |                                              |

|                     | HT40<br>MCS7 | -   | -73 | -72 | dBm |                                              |

| WIF RX<br>11ax HE20 | HE20<br>MCS0 | -   | -96 | -95 | dBm | LDPC 4x3.2us<br>PER 10%, 4096<br>octets PSDU |

| 灵敏度                 | HE20<br>MCS1 | -   | -93 | -92 | dBm |                                              |

|                     | HE20<br>MCS2 | -   | -91 | -89 | dBm |                                              |

| 参数                                | Sub-Item                             | 最小值 | 典型值 | 最大值 | 单位  | 测试条件                                       |

|-----------------------------------|--------------------------------------|-----|-----|-----|-----|--------------------------------------------|

|                                   | HE20<br>MCS3                         | -   | -88 | -87 | dBm |                                            |

|                                   | HE20<br>MCS4                         | -   | -84 | -83 | dBm |                                            |

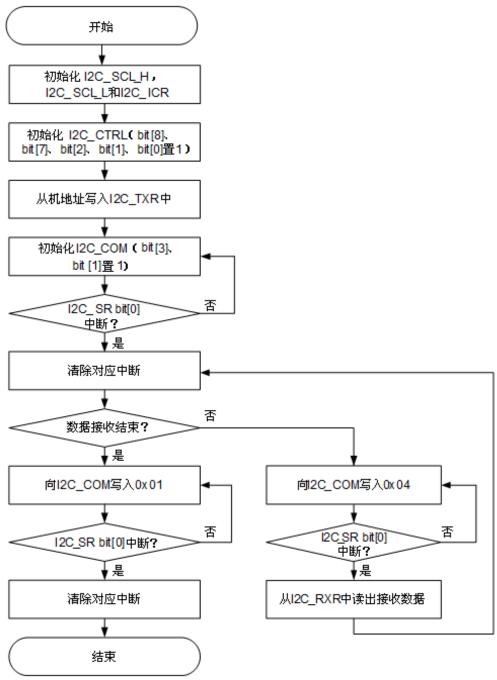

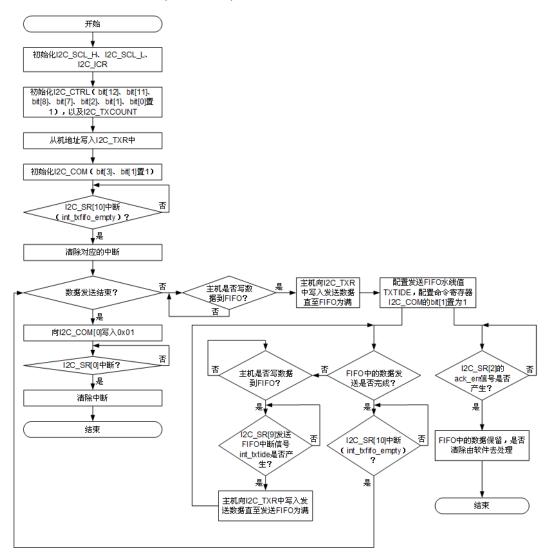

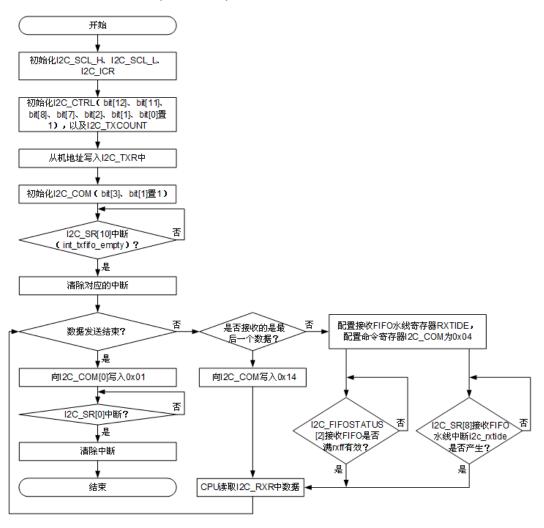

|                                   | HE20<br>MCS5                         | -   | -80 | -79 | dBm |                                            |