# FRDMGD3100HB8EVM half-bridge evaluation board Rev. 1 — 4 August 2020

User guide

# FRDMGD3100HB8EVM

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### **Important Notice**

NXP provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Typical parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including Typical, must be validated for each customer application by customer's technical experts.

NXP does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use NXP products for any such unintended or unauthorized application, the Buyer shall indemnify and hold NXP and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges NXP was negligent regarding the design or manufacture of the part.

#### FRDMGD3100HB8EVM half-bridge evaluation board

# 2 Getting started

NXP analog product development boards provide a platform for evaluating a broad range of NXP analog, mixed-signal and power solution products. NXP analog product development boards incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer a long battery life, a small form factor, reduced component counts, low cost, and improved performance in powering state-of-the-art systems.

The tool summary page for the FRDMGD3100HB8EVM evaluation board is at <a href="http://www.nxp.com/FRDMGD3100HB8EVM">http://www.nxp.com/FRDMGD3100HB8EVM</a>. The tool summary page provides information related to using the evaluation board. The page contains the following sections:

- Overview A brief summary of the evaluation board and its capabilities

- Supported Devices A list of devices that the evaluation board supports

- Specifications An overview of the technical and functional specifications for the board

- Documents and Software/Design Resources All of the information and resources required by users who have already purchased the FRDMGD3100HB8EVM. This section includes:

- Design Tools & Files Click on the Download button to download the board Bill of Materials and the Gerber files for the PCB assemblies.

- Printed Circuit Boards and Schematics Click on the Download button to download a .pdf version of the FRDMGD3100HB8EVM board schematics.

The Get Started link in the upper left of the menu bar provides information applicable to using the FRDMGD3100HB8EVM.

#### 2.1 Kit contents/packing list

The FRDMGD3100HB8EVM kit contents include:

- Complete assembly of FRDMGD3100HB8EVM evaluation board

- 3.3 V to 5.0 V GD3100 translator board connected to FRDM-KL25Z

- USB cable, type A male/type mini B male, 3 ft

- 1.27 mm jumpers for configuration (included with kit boards)

- · Quick start guide

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### 2.2 Required equipment

The kit requires the following equipment:

- · Compatible SiC module

- · DC link capacitor compatible with the SiC module

- 30 μH to 50 μH, high current air core inductor for double pulse testing

- · HV power supply with protection shield and hearing protection

- 25 V, 1.0 A DC power supply

- 500 MHz 2.5 GS/s 4-channel oscilloscope

- Rogowski coil, PEM Model CWT Mini HF60R, or CTW MiniHF30 (smaller diameter)

- Isolated high-voltage probe (CAL Test Electric CT2593-1, LeCroy AP030)

- · Digital voltmeter

#### 2.3 System requirements

The kit requires the following to function properly with the software:

· Windows 7 or higher operating system

# 3 Getting to know the hardware

#### 3.1 Overview

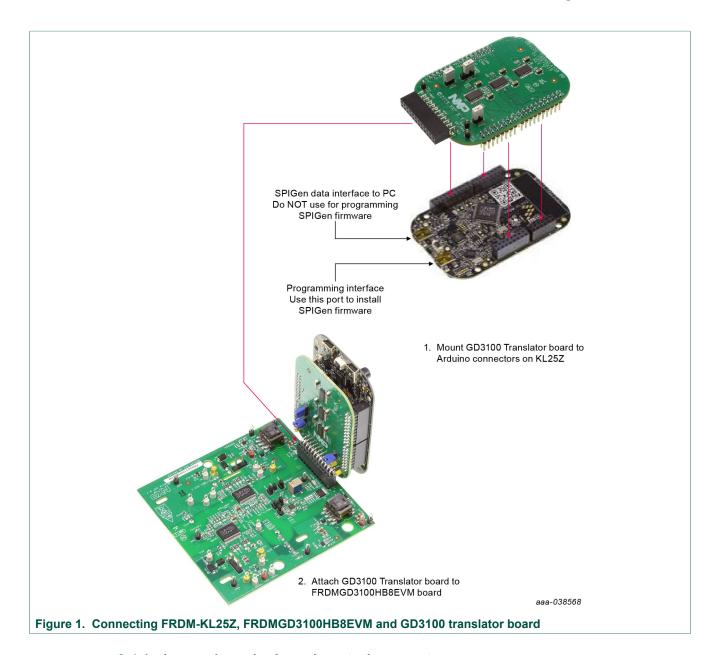

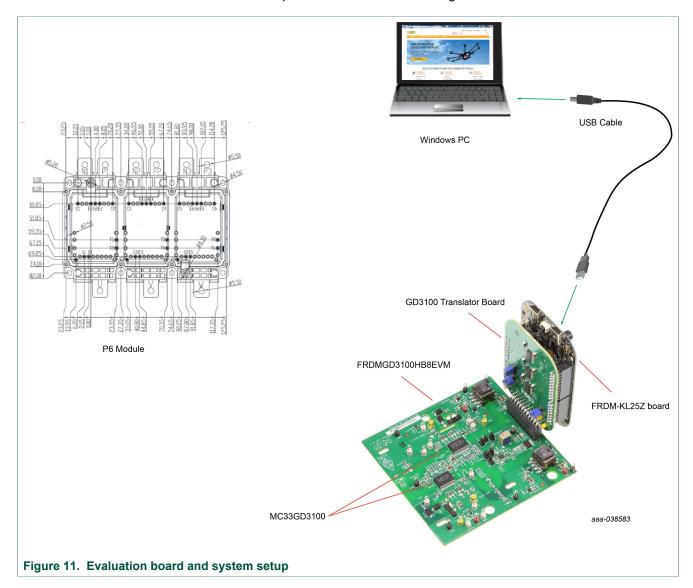

The FRDMGD3100HB8EVM is a half-bridge evaluation kit populated with two MC33GD3100 single channel gate drive devices. The kit includes the Freedom KL25Z microcontroller hardware for interfacing a PC installed with SPIGen software for communication to the serial peripheral interface (SPI) registers on the GD3100 gate drive devices in either daisy chain or standalone configuration.

The GD3100 translator board is used to translate 3.3 V signals to 5.0 V signals between the MCU and the MC33GD3100 gate drivers. The evaluation kit can be connected to a compatible insulated gate bipolar transistor (IGBT) or SiC module for half-bridge evaluations and applications development.

#### 3.2 Board features

- Capability to connect to P6 SiC module for half-bridge evaluations

- Negative VEE gate low drive level (-3.9 V DC)

- VCCREG regulated high gate drive level (+15 V DC)

- Jumper configurable for disabling dead time fault protection when short-circuit testing

- · Easy access power, ground, and signal test points

- Easy to install and use SPIGen GUI for interfacing via SPI through PC; software includes double pulse and short-circuit testing capability

- DC link bus voltage monitor on low-side driver via AMUXIN and AOUT

- Negative temperature coefficient (NTC) connection and configurable for monitoring module temperature

UM11440

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### 3.3 Device features

Table 1. Device features

| Device     | Description                                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33GD3100 | The MC33GD3100 is an advanced single channel gate driver for IGBTs. | <ul> <li>Compatible with current sense and temp sense IGBTs</li> <li>DESAT detection capability for detecting V<sub>CE</sub> desaturation condition</li> <li>Fast short-circuit protection for IGBTs with current sense feedback</li> <li>Compliant with automotive safety integrity level (ASIL) C/D ISO 26262 functional safety requirements</li> <li>SPI interface for safety monitoring, programmability, and flexibility</li> <li>Integrated galvanic signal isolation</li> <li>Integrated gate drive power stage capable of 10 A peak source and sink</li> <li>Interrupt pin for fast response to faults</li> <li>Compatible with negative gate supply</li> <li>Compatible with 200 V to 1700 V IGBTs, power range &gt; 125 kW</li> </ul> |

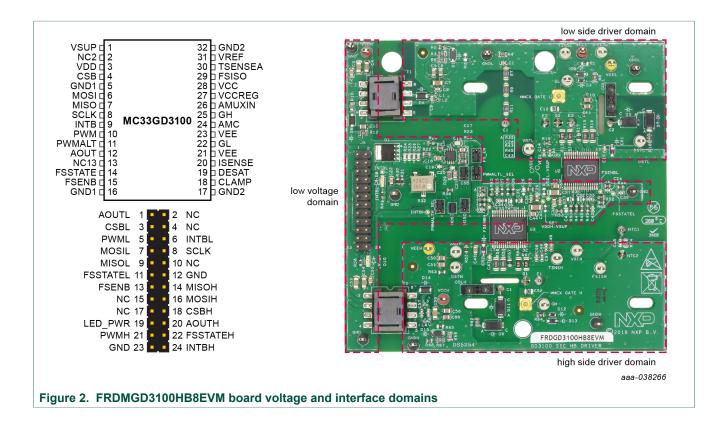

### 3.4 Board description

The FRDMGD3100HB8EVM is a half-bridge evaluation board populated with two MC33GD3100 single channel IGBT or SiC gate drive devices. The board supports connection to an FRDM-KL25Z microcontroller for SPI communication configuration programming and monitoring. The board includes DESAT circuitry for short-circuit detection and implementation of MC33GD3100 shutdown protection capabilities.

The evaluation board is designed to connect to a P6 SiC metal-oxide-semiconductor field-effect transistor (MOSFET) for evaluation of the MC33GD3100 performance and capabilities.

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### 3.4.1 Low-voltage logic and control connector

The low-voltage domain is 12 V VSUP domain that interfaces with the MCU and MC33GD3100 control registers through the 24-pin connector interface.

The low-side driver and high-side driver domains are driver control interfaces to SiC module single phase connections and test points.

#### FRDMGD3100HB8EVM half-bridge evaluation board

Table 2. Low-voltage domain 24-pin connector definitions

| Pin | Name     | Function                                                                                                     |

|-----|----------|--------------------------------------------------------------------------------------------------------------|

| 1   | AOUTL    | analog output duty cycle encoded signal (low side) for reading temperature via TSENSEA or voltage via AMUXIN |

| 2   | n.c.     | not connected                                                                                                |

| 3   | CSBL     | chip select bar (low side)                                                                                   |

| 4   | n.c.     | not connected                                                                                                |

| 5   | PWML     | pulse width modulation (PWM) input (low side)                                                                |

| 6   | INTBL    | interrupt bar (low side)                                                                                     |

| 7   | MOSIL    | master out slave in (low side)                                                                               |

| 8   | SCLK     | serial clock input                                                                                           |

| 9   | MISOL    | master in slave out (low side)                                                                               |

| 10  | n.c.     | not connected                                                                                                |

| 11  | FSSTATEL | fail-safe state (low side)                                                                                   |

| 12  | GND      | ground                                                                                                       |

| 13  | FSENB    | fail-safe enable (high side and low side)                                                                    |

| 14  | MISOH    | master in slave out (high side)                                                                              |

| 15  | n.c.     | not connected                                                                                                |

| 16  | MOSIH    | master out slave in (high side)                                                                              |

| 17  | n.c.     | not connected                                                                                                |

UM11440 All information

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

#### FRDMGD3100HB8EVM half-bridge evaluation board

| Pin | Name     | Function                                               |

|-----|----------|--------------------------------------------------------|

| 18  | CSBH     | chip select bar (high side)                            |

| 19  | LED_PWR  | USB 3.3 V power for INTB LEDs (high side and low side) |

| 20  | AOUTH    | duty cycle encoded signal (high side)                  |

| 21  | PWMH     | PWM input (high side)                                  |

| 22  | FSSTATEH | fail-safe state (high side)                            |

| 23  | GND      | ground                                                 |

| 24  | INTBH    | interrupt bar (high side)                              |

#### 3.4.2 Test point definitions

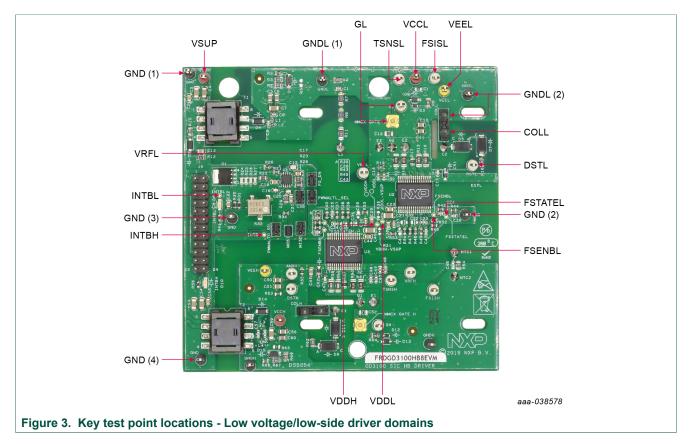

All test points are clearly marked on the evaluation board. Figure 3 shows the location of various test points.

# FRDMGD3100HB8EVM half-bridge evaluation board

Table 3. Test point definitions-low voltage/low-side driver domains

| Name       | Test Point   | Definition                                                                                                                 |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| Low-voltag | e domain     | ,                                                                                                                          |

| GND (1)    | TP2          | Grounding points for low-voltage domain                                                                                    |

| INTBH      | TP20         | Test point for interrupt bar high-side                                                                                     |

| INTBL      | TP11         | Test point for interrupt bar low-side                                                                                      |

| VSUP       | TP26         | DC voltage source connection point for VSUP power input of GD3100 devices. Typically supplied by vehicle battery +12 V DC. |

| Low-side d | river domain | ,                                                                                                                          |

| COLL       | J90          | Collector test point/connection low-side                                                                                   |

| DSTL       | TP10         | V <sub>CE</sub> desaturation test point connected to high-side driver DESAT pin and circuitry                              |

| FSENBL     | TP12         | Test point connection to low-side driver fail-safe enable pin (FSENB)                                                      |

| FSISL      | TP6          | Test point connection to low-side driver tri-state gate drive pin (FSISO)                                                  |

| FSTATEL    | TP17         | Test point connection to low-side driver fail-state state pin (FSSTATE)                                                    |

| GL         | TP5          | Module gate test point on low-side driver domain which is the charging pin of gate; including MMCX probe connection        |

| GND (2)    | TP13         | Grounding point for low-side driver domain                                                                                 |

| GND (3)    | TP16         | Grounding point for low-side driver domain                                                                                 |

| GND (4)    | TP27         | Grounding point for low-side driver domain                                                                                 |

| GNDL (1)   | TP3          | Grounding point for isolated low-side driver grounding plane                                                               |

| GNDL (2)   | TP7          | Grounding point for isolated low-side driver grounding plane                                                               |

| TSNSL      | TP8          | Test point connection to low-side gate drive TSENSE pin                                                                    |

| VCCL       | TP1          | Positive voltage supply test point for isolated circuitry and low-side driver domain                                       |

| VDDH       | TP18         | Test point for internal power from MC33GD3100A1 (U3) VDD pin                                                               |

| VDDL       | TP14         | Test point for internal power from MC33GD3100A1 (U2) VDD pin                                                               |

| VEEL       | TP4          | Negative voltage supply test point for low-side driver gate of IGBT or SiC module                                          |

| VRFL       | TP9          | 5.0 V reference test point for isolated analog circuitry on low-side driver                                                |

# FRDMGD3100HB8EVM half-bridge evaluation board

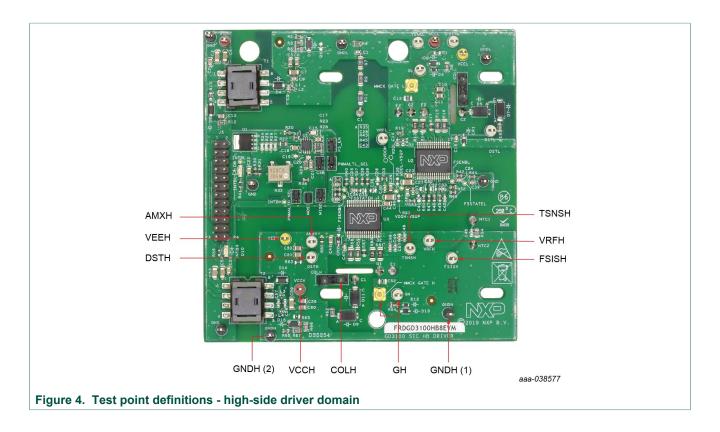

Table 4. Test point definition - high-side driver

| Name     | Test point | Definition                                                                                                           |

|----------|------------|----------------------------------------------------------------------------------------------------------------------|

| AMXH     | TP23       | High-side driver test point for analog MUX input                                                                     |

| COLH     | J101       | Collector test point/connection high-side                                                                            |

| DSTH     | TP25       | V <sub>CE</sub> desaturation test point connected to high-side driver DESAT pin and circuitry                        |

| FSISH    | TP24       | Test point connection to high-side driver tri-state gate drive pin (FSISO)                                           |

| GH       | TP28       | Module gate test point on high-side driver domain which is the charging pin of gate; including MMCX probe connection |

| GNDH (1) | TP31       | Grounding point for isolated high-side driver grounding plane                                                        |

| GNDH (2) | TP32       | Grounding point for isolated high-side driver grounding plane                                                        |

| TSNSH    | TP21       | Test point connection to high-side gate drive TSENSE pin                                                             |

| VCCH     | TP29       | Positive voltage supply test point for isolated circuitry and high-side driver domain                                |

| VEEH     | TP30       | Negative voltage supply test point for high-side driver gate of IGBT or SiC module                                   |

| VRFH     | TP22       | 5.0 V reference test point for isolated analog circuitry on high-side driver                                         |

#### FRDMGD3100HB8EVM half-bridge evaluation board

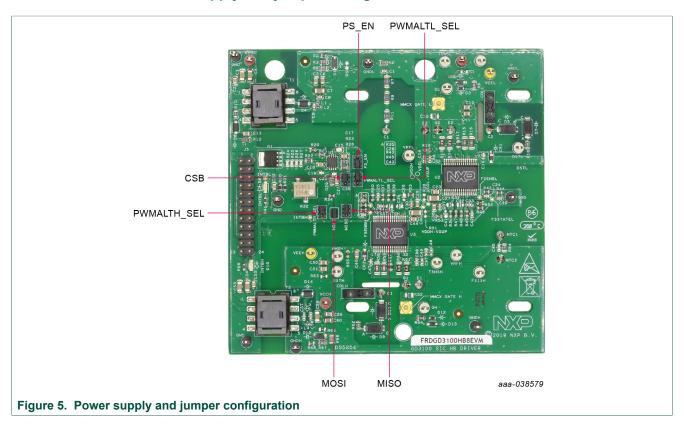

## 3.4.3 Power supply and jumper configuration

Table 5. Jumper definitions

| Jumper           | Position | Function                                                            |  |

|------------------|----------|---------------------------------------------------------------------|--|

| PWMALTL_SEL (J4) | 1-2      | Dead time fault protection enabled (high side)                      |  |

| FWWALTL_SEL (34) | 2-3      | Dead time fault protection disabled (use for short-circuit testing) |  |

| PS EN (J2)       | 1–2      | Flyback power supply enable controlled from MCU                     |  |

| F3_EN (J2)       | 2–3      | Flyback power supply enable always on                               |  |

| CSB (J3)         | 1–2      | Normal operation                                                    |  |

| C3B (J3)         | 2–3      | Daisy chain operation                                               |  |

| PWMALTH_SEL      | 1-2      | Dead time fault protection enabled (low side)                       |  |

| (J7)             | 2-3      | Dead time fault protection disabled (use for short-circuit testing) |  |

| MOSI (J8)        | Open     | Daisy chain operation                                               |  |

| MOSI (Jo)        | Close    | Normal operation                                                    |  |

| MISO (16)        | 1-2      | Normal operation                                                    |  |

| MISO (J6)        | 2-3      | Daisy chain operation                                               |  |

#### FRDMGD3100HB8EVM half-bridge evaluation board

**Table 6. Power Supply Definition**

| Component           | Definition                                                               |

|---------------------|--------------------------------------------------------------------------|

| Flyback MOSFET (Q1) | AEC Q101-compliant logic level N-channel MOSFET                          |

| Potentiometer (R32) | Adjusts resistor R3 for VCCH/VCCL and VEEH/VEEL Tune VCC-GNDISO FOR +17V |

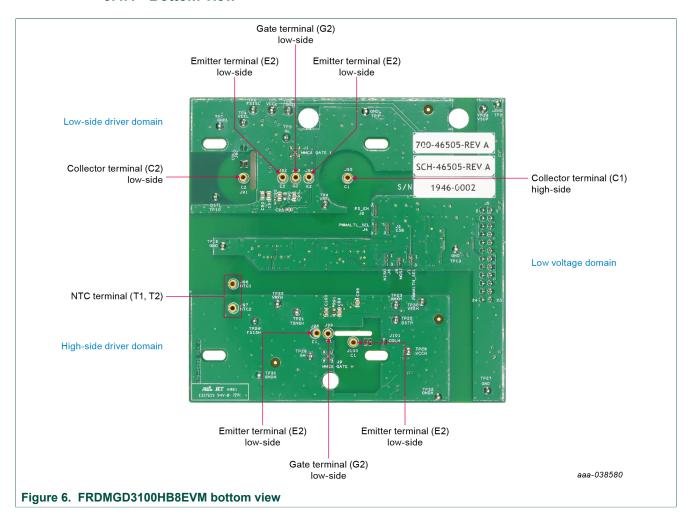

#### 3.4.4 Bottom view

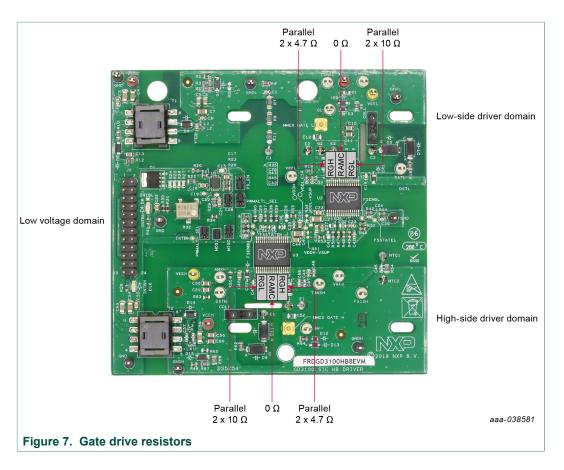

#### 3.4.5 Gate drive resistors

- RGH gate high resistor in series with the GH pin at the output of the MC33GD3100 gate high driver and P6 SiC module gate that controls the turn-on current for SiC MOSFET gate.

- RGL gate low resistor in series with the GL pin at the output of the MC33GD3100 gate low driver and P6 SiC module gate that controls the turn-off current for SiC MOSFET gate.

- RAMC series resistor between P6 SiC module gate and AMC input pin of the MC33GD3100 driver for gate sensing and active Miller clamping.

UM11440

#### FRDMGD3100HB8EVM half-bridge evaluation board

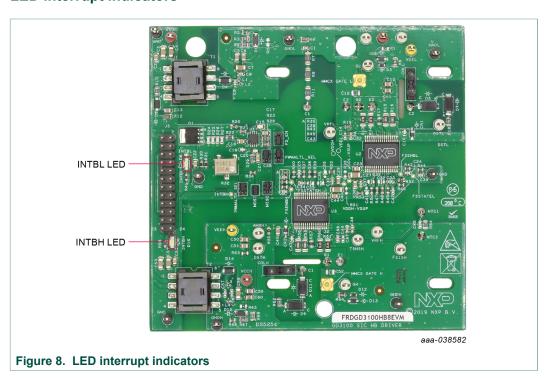

#### 3.4.6 LED interrupt indicators

#### FRDMGD3100HB8EVM half-bridge evaluation board

Table 7. LED interrupt indicators

| LED            | Description                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| Low-side INTB  | connected to the INTB output pin of low-side driver indicating reported fault status when on (active LOW)            |

| High-side INTB | connected to the INTB interrupt output pin of high-side driver indicating reported fault status when on (active LOW) |

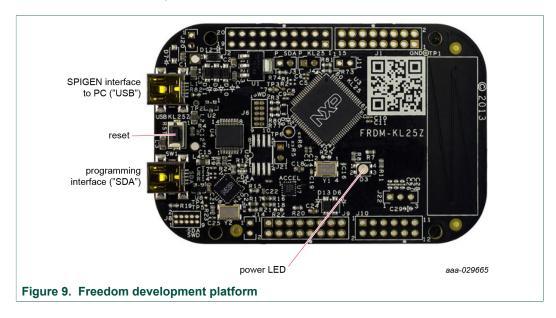

#### 3.5 Kinetis KL25Z Freedom board

The Freedom KL25Z is an ultra low-cost development platform for Kinetis L series MCU built on Arm Cortex-M0+ processor.

#### FRDMGD3100HB8EVM half-bridge evaluation board

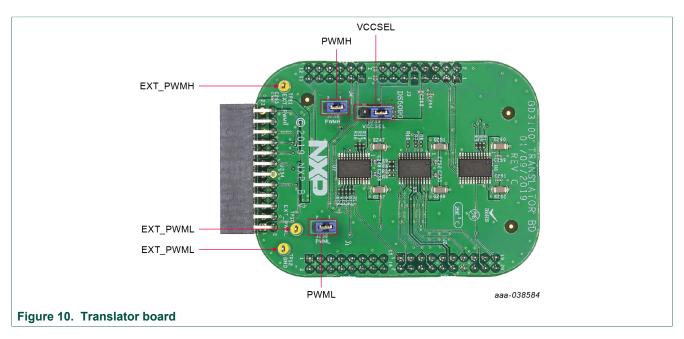

#### 3.6 3.3 V to 5.0 V translator board

KITGD3100TREVB translator enables level shifting of signals from MCU 3.3 V to  $5.0~\rm{V}$  SPI communication.

Table 8. Translator board jumper definitions

| Jumper/Test Point                                                | Position    | Function                                       |  |  |

|------------------------------------------------------------------|-------------|------------------------------------------------|--|--|

| Jumper                                                           | Jumper      |                                                |  |  |

| D\A(\A)   OF   (1005)                                            | 1-2         | Selects PWM high-side control from KL25Z MCU   |  |  |

| PWMH_SEL (J235)                                                  | Open        | External PWM high-side control                 |  |  |

| DIAMAL OF (1996)                                                 | 1-2         | Selects PWM low-side control from KL25Z MCU    |  |  |

| PWML_SEL (J236)                                                  | Open        | External PWM low-side control                  |  |  |

| VCCSEL (J233)                                                    | 1-2         | Selects 5.0 V for 5.0 V compatible gate drive  |  |  |

| VOCSEE (0200)                                                    | 2-3         | Selects 3.3 V for 3.3 V compatible gate drive  |  |  |

| Test points                                                      | Test points |                                                |  |  |

| EXT_PWMH (TP11) — Test point connection for terminal PWM control |             | Test point connection for terminal PWM control |  |  |

| EXT_PWML (TP10)                                                  | _           | Test point connection for terminal PWM control |  |  |

| GND (TP12)                                                       | _           | Grounding point                                |  |  |

# 4 Configuring the hardware

FRDMGD3100HB8EVM is connected to a GD3100 translator board and a FRDM-KL25Z board as shown in <u>Figure 11</u>. Double pulse and short-circuit testing can be conducted using a Windows based PC with SPIGen software.

#### FRDMGD3100HB8EVM half-bridge evaluation board

Suggested equipment needed for test:

- · Rogowski coil high-current probe

- High-voltage differential voltage probe

- · High sample rate digital oscilloscope with probes

- · DC link capacitor

- SiC MOSFET P6 module

- · Windows based PC

- High-voltage DC power supply for DC link voltage

- Low-voltage DC power supply for VSUP

- +12 V DC gate drive board low-voltage domain

- Voltmeter for monitoring high-voltage DC link supply

- · Load coil for double pulse and short-circuit testing

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### 5 Installation and use of software tools

Software for FRDMGD3100HB8EVM is distributed with the SPIGen GUI tool (available on NXP.com). Necessary firmware comes pre-installed on the FRDM-KL25Z with the kit.

Even if the user intends to test with other software or PWM, it is recommended to install this software as a backup or to help debugging.

#### 5.1 Installing SPIGen on your computer

The latest version of SPIGen supports the MC33GD3100 and is designed to run on any Windows 10, Windows 8, or Windows 7 based operating system. To install the software, do the following:

- 1. Go to www.nxp.com/SPIGen and click **Download**.

- 2. When the SPI generator (SPIGen) software page appears, click **Download** and select the version associated with your PC operating system.

- 3. If instructed for the SPIGen wizard to create a shortcut, an SPIGen icon appears on the desktop. By default, the SPIGen executable file is installed at C:\Program Files (x86)\SPIGen.

Installing the device drivers overwrites any previous SPIGen installation and replaces it with a current version containing the MC33GD3100 drivers. However, configuration files (.spi) from the previous version remain intact.

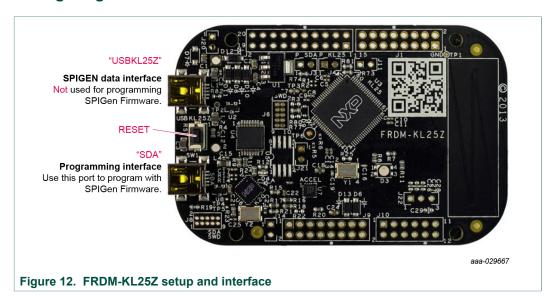

#### 5.2 Configuring the FRDM-KL25Z microcode

By default, the FRDM-KL25Z delivered with this kit is preprogrammed with the current and most up-to-date firmware available for the kit.

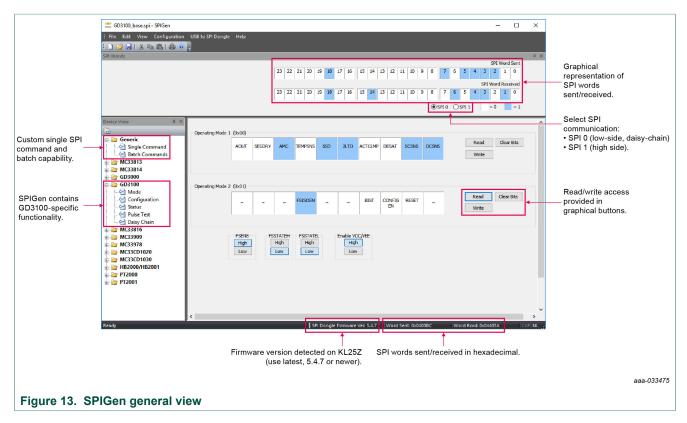

A way to check quickly that the microcode is programmed and the board is functioning properly, is to plug the KL25Z into the computer, open SPIGen, and verify that the software version at the bottom is 5.4.7 (see <u>Figure 13</u>).

If a loss of functionality following a board reset, reprogramming, or a corrupted data issue, the microcode may be rewritten per the following steps:

UM11440

#### FRDMGD3100HB8EVM half-bridge evaluation board

- 1. To clear the memory and place the board in boot loader mode, hold down the reset button while plugging a USB cable into the **OpenSDA** USB port.

- 2. Verify that the board appears as a BOOTLOADER device and continue with step 3. If the board appears as KL25Z, you may go to step 6.

- 3. Download the **Firmware Apps** .zip archive from the PEmicro OpenSDA webpage (<a href="http://www.pemicro.com/opensda/">http://www.pemicro.com/opensda/</a>). Validate your email address to access the files.

- 4. Find the most recent MDS-DEBUG-FRDM-KL25Z\_Pemicro\_v\*\*\*.SDA and copy/drag-and-drop into the **BOOTLOADER** device.

- 5. Reboot the board by unplugging and replugging the connection to the **OpenSDA** port. Verify now that the device appears as a KL25Z device to continue.

- 6. Locate the most recent KL25Z firmware; which is distributed as part of the SPIGen package.

- a. From the SPIGen install directory, which is located in the **SPI Dongle Firmware** folder and is named in the form "UsbSPIDongleKL25Z GD3100 v\*\*\*.srec".

- b. This .srec file is a product/family-specific configuration file for FRDM-KL25Z containing the pin definitions, SPI/PWM generation code, and pin mapping assignments necessary to interface with the translator board as part of FRDMGD31RPEVM.

- With the KL25Z still plugged through the OpenSDA port, copy/drag-and-drop the .srec file into the KL25Z device memory. Once done, disconnect the USB and plug into the other USB port, labeled KL25Z.

- a. The device may not appear as a distinct device to the computer while connected through the KL25Z USB port, this is normal.

- 8. The FRDM-KL25Z board is now fully set up to work with FRDMGD31RPEVM and the SPIGen GUI.

- a. There is no software stored or present on either the driver or translator boards, only on the FRDM-KL25Z MCU board.

All uploaded firmware is stored in non-volatile memory until the reset button is hit on the FRDM-KL25Z. There is no need to repeat this process upon every power up, and there is no loss of data associated with a single unplug event.

#### 5.3 Using the SPIGen graphical user interface

The SPIGen graphical user interface is available from <a href="http://www.nxp.com/SPIGen">http://www.nxp.com/SPIGen</a> as an evaluation tool demonstrating MC33GD3100-specific functionality, configuration, and fault reporting. SPIGen also includes basic capacity for the FRDMGD31RPEVM to control an IGBT or SiC module, enabling double pulse or short-circuit testing.

SPI messages can be realized graphically or in hexadecimal format. CSB is selectable to address one or both MC33GD3100 on the board. See <u>Figure 13</u> for SPIGen graphical user interface for MC33GD3100 internal register read and write access.

#### FRDMGD3100HB8EVM half-bridge evaluation board

Some general guidelines on SPIGen usage:

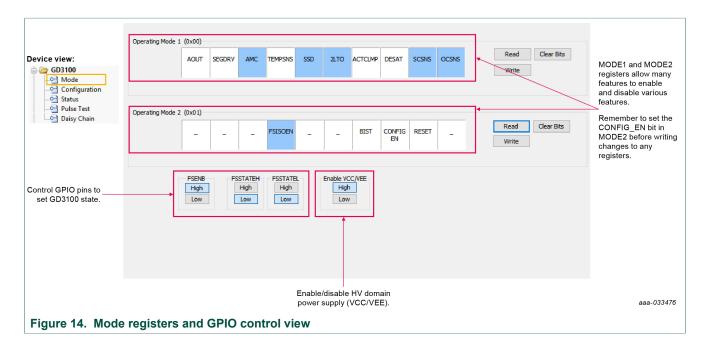

- When attempting to change operating modes, configuration registers, or status mask bits, ensure the CONFIG\_EN bit in the MODE2 register is set to logic 1. Fault status bits can be cleared without CONFIG\_EN being set to logic 1.

- On mode, configuration, and status views, read operations send identical back-to-back commands so the response is obtained upon a single click on the "Read" button. This behavior is normal SPI operation, but is implemented this way for the convenience of the end-user.

- On all views, write operations are only performed once per click.

#### 5.3.1 Mode registers

See Figure 14 for an overview of control options available on the "Mode" view on SPIGen. See the MC33GD3100 data sheet for a complete description of MODE1 and MODE2 registers and pin functionalities. The onboard flyback power supply provides VCC and VEE for the HV domains and can be enabled (default) or disabled in the event an external supply or characteristic is desired.

#### FRDMGD3100HB8EVM half-bridge evaluation board

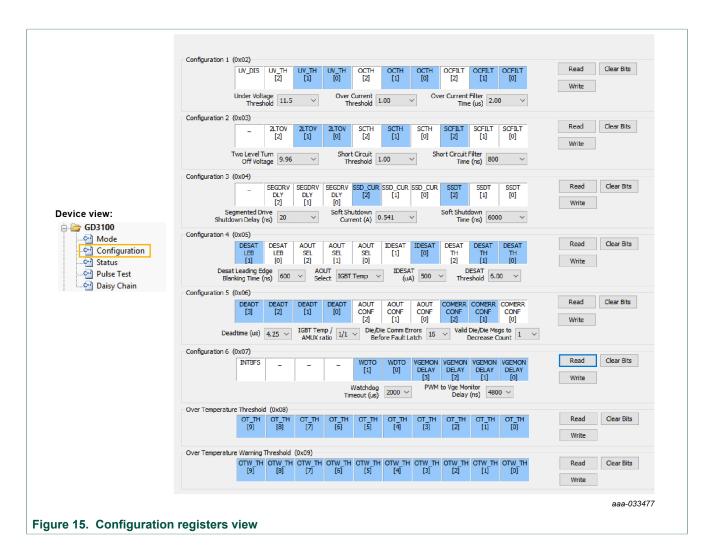

#### 5.3.2 Configuration register

See the MC33GD3100 data sheet for configuration register descriptions.

When attempting to change configuration parameters, ensure the CONFIG\_EN bit in the MODE2 register is set to logic 1. Read operations send identical back-to-back commands so the response is obtained upon a single click on the **Read** button. Write operations are only performed once per click.

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### 5.3.3 Status and mask register

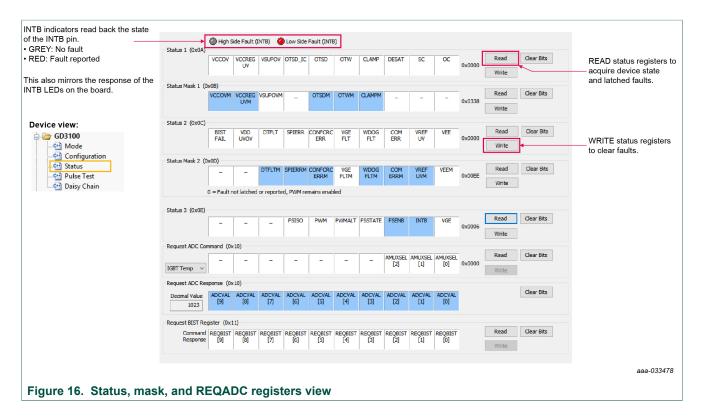

See the MC33GD3100 data sheet for status and mask SPI register descriptions. INTB indicators mirror the status of the INTB pin on both high-side and low-side MC33GD3100 simultaneously. However, only one (either high side or low side) can be read at a time over SPI (selected by "SPI 0" or "SPI 1") in this view.

#### FRDMGD3100HB8EVM half-bridge evaluation board

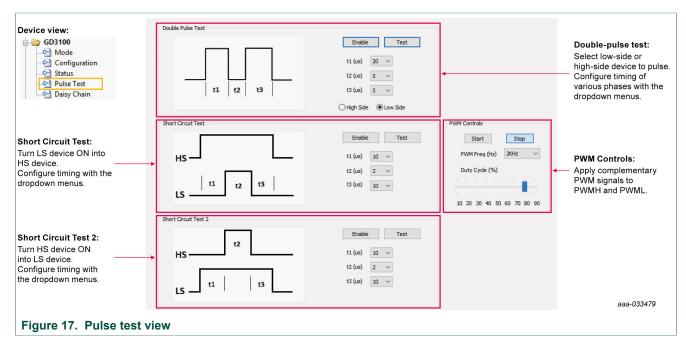

#### 5.3.4 Pulse test

The pulse test view allows a few simple waveforms to be applied to the PWM and PWMALT pins, to evaluate with an IGBT or SiC module.

For short-circuit testing, it is recommended to bypass dead time protection. Dead time protection can be disabled as described in <u>Section 3.4.3</u>. The jumpers PWMLSEL and PWMHSEL are used to disable the dead time fault protection.

UM11440

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

#### FRDMGD3100HB8EVM half-bridge evaluation board

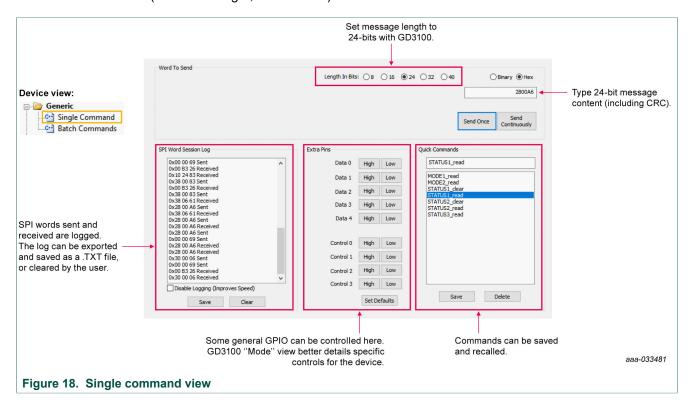

#### 5.3.5 Single command

The single command view contains a log of recent commands, displayed in hexadecimal format. Single SPI commands can be saved and recalled by name. Commands defined here are available for scripting in the batch commands page. SPI words sent and received (initiated from any tab) are logged here in hexadecimal and can be saved and exported in a text file. This view does not support daisy-chain length command structure ( $n \times 24$  bit length, where n > 1).

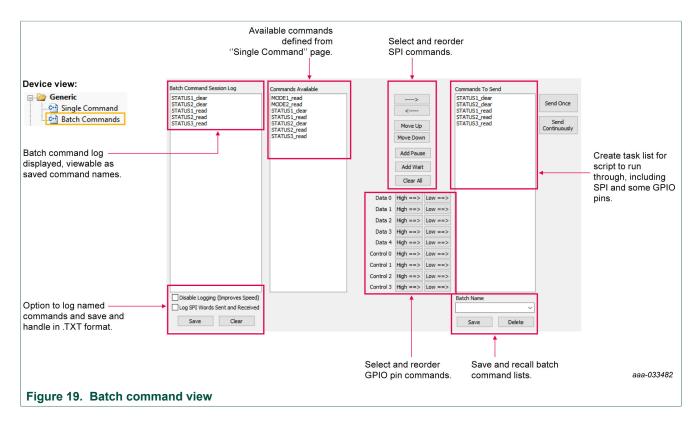

#### 5.3.6 Batch command

The batch command view allows creation of scripts containing commands defined by the single command page. Batches can be named, saved, and recalled. Batch commands are useful for quickly initializing the device after power-up.

The batch commands sent can be logged and saved in a text file. The SPI words sent/received can be viewed in hexadecimal and exported back in the single command view. This view does not support daisy-chain length command structure ( $n \times 24$  bit length, where n > 1).

#### FRDMGD3100HB8EVM half-bridge evaluation board

# 5.4 Troubleshooting

Some common issues and troubleshooting procedures are detailed below. This is not an exhaustive list by any means, and additional debug may be needed:

| Problem                           | Evaluation                                                    | Explanation                                                                                                                              | Corrective action(s)                                                                                                                                   |

|-----------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| No PWM output (no fault reported) | Check PWM jumper position on translator board                 | Incorrect PWM jumpers obstruct signal path but not report fault                                                                          | Set PWMH_SEL (J235) and PWML_SEL (J236) jumpers properly, for desired control method:  • 3.3 V to 5.0 V translator board reviewed in Section 3.6       |

|                                   | Check correct firmware is in use for translator board version | Firmware includes pin definitions and pinout for KL25Z corresponding to routing and pin allocation on specific translator board revision | Check firmware version in SPIGen, according to Figure 13. Match this to microcode needed for translator board revision, stated in Section 5.2, step 6. |

|                                   | Check PWM control signal                                      | Ensure that proper PWM signal is reaching MC33GD3100                                                                                     | Monitor EXT_PWML (TP10) and EXT_PWMH (TP11) for commanded PWM state                                                                                    |

|                                   | Check FSENB status (see<br>MC33GD3100 pin 15, STATUS3)        | PWM is disabled when FSENB = LOW                                                                                                         | Set pin FSENB = HIGH to continue                                                                                                                       |

|                                   | Check CONFIG_EN bit (MODE2)                                   | PWM is disabled when CONFIG_EN is logic 1                                                                                                | Write CONFIG_EN = logic 0 to continue                                                                                                                  |

# FRDMGD3100HB8EVM half-bridge evaluation board

| Problem                                                       | Evaluation                                                    | Explanation                                                                                                                                                            | Corrective action(s)                                                                                                                                                                                                                               |

|---------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No PWM output (fault reported)                                | Check VGE fault (VGE_FLT)                                     | A short on IGBT or SiC module gate, or too low of VGEMON delay setting causes VGE fault, locking out PWM control of the gate.                                          | Clear VGE_FLT bit (STATUS2) to continue. Increase VGEMON delay setting (CONFIG6).  If safe operating condition can be guaranteed, set VGE_FLTM (MSK2) bit to logic 0, to mask fault.                                                               |

|                                                               | Check for short-circuit fault (SC) in STATUS1 register        | SC is a severe fault that disables PWM. SC fault cannot be masked                                                                                                      | Clear SC fault to continue. Consider adjusting SC fault settings on MC33GD3100:  Adjust short-circuit threshold setting (CONFIG2)  Adjust short-circuit filter setting (CONFIG2)                                                                   |

| PWM output is good, but with persistent fault reported        | Check for dead time fault (DTFLT) in<br>STATUS2 register      | Dead time is enforced, but fault indicates that PWM controls signals are in violation                                                                                  | Clear DTFLT fault bit (STATUS2). Check PWMHSEL (J10) and PWMLSEL (J9) are configured to bypass dead time faults. Consider adjusting dead time settings on MC33GD3100: Change mandatory PWM dead time setting (CONFIG5) Mask dead time fault (MSK2) |

|                                                               | Check for overcurrent (OC) fault in STATUS1 register          | OC fault latches, but does not disable PWM. OC fault cannot be masked.                                                                                                 | Clear OC fault bit (STATUS1).  Adjust OC fault detection settings on MC33GD3100:  • Adjust overcurrent threshold setting (CONFIG1)  • Adjust overcurrent filter setting (CONFIG1)                                                                  |

| PWM or FSSTATE rising edge has longer delay than falling edge | Check translator output voltage versus MC33GD3100 VDD voltage | Low translator output voltage<br>(compared with correct VDD at<br>MC33GD3100) causes the high<br>threshold at the MC33GD3100 pin to<br>be crossed later than commanded | Check translator output voltage selection (J233) is configured to the same level as the MC33GD3100 VDD Check VCCSEL supply or translator outputs on the translator board for excessive loading or supply droop/pulldown                            |

| WDOG_FLT reported on startup                                  | Check VSUP and VCC are powered                                | On initialization, watchdog fault is reported when one die is powered up before the other                                                                              | Check VSUP and VCC both have power applied. Clear WDOG_FLT bit (STATUS2) to continue.                                                                                                                                                              |

| SPIERR reported on startup                                    | Check KL25Z/translator connection                             | On initialization, SPIERR can occur when the SPI bus is open, or when MC33GD3100 IC is powered up before the translator (which provides CSB).                          | Clear SPIERR fault to continue.<br>Reinitialize power to MC33GD3100<br>after translator is powered (over<br>USB).                                                                                                                                  |

| SPIERR reported after SPI message                             | Check bit length of message sent                              | There is SPIERR if SCLK does not see a n*24 multiple of cycles                                                                                                         | Use 24-bit message length for SPI messages                                                                                                                                                                                                         |

|                                                               | Check CRC                                                     | SPIERR faults if CRC provided in sent message is not good                                                                                                              | Use SPIGen to generate commands with valid CRC. The command can be copied in binary or hexadecimal and sent from another program.                                                                                                                  |

|                                                               | Check for sufficient dead time between SPI messages           | SPIERR fault bit is set when the time between SPI messages (txfer_delay) received is too short. Minimum required delay time is 19 µs.                                  | Check time between CSB rising edge (old message end) and CSB falling edge (new message start) during normal SPI read, and ensure transfer delay dead time check.  SPIERR can also be cleared in BIST.                                              |

| VCCREGUV reported on startup                                  | Check VCCREG potential                                        | Caused by low VCC                                                                                                                                                      | Clear VCCREGUV fault bit (STATUS1). Tune VCC-GNDISO potential with power supply set resistor (R32).                                                                                                                                                |

#### FRDMGD3100HB8EVM half-bridge evaluation board

| Problem                                           | Evaluation                                                       | Explanation                                                                              | Corrective action(s)                                                                                                                                                                                                                            |

|---------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREFUV reported on startup                        | Check HV domain is powered correctly                             | Related to slow rise time of VCC supply on HV domain, or failed VREF regulator           | Clear VREFUV bit (STATUS2).<br>Reset HV domain supply if fault bit<br>does not clear.                                                                                                                                                           |

|                                                   | Check VCC for undervoltage condition                             | Low VCC is visible indirectly through other HV domain faults                             | Tune VCC-GNDISO using R32 feedback                                                                                                                                                                                                              |

| VCCOV fault reported on startup                   | Check VEE level on suspect domain.                               | If VEE level is not at desired negative voltage it could cause excessive VCC level.      | Check Zener diode in power supply circuit for proper value in setting VEE level. Clear VCCOV bit (STATUS1) to continue.                                                                                                                         |

|                                                   | Check VCC-GNDISO potential                                       | PWM is disabled during a VCC overvoltage (20 V nom.)                                     | Tune VCC-GNDISO potential to suitable level with power supply set resistor (R32). Clear VCCOV bit (STATUS1) to continue.                                                                                                                        |

| No PWM during short circuit test                  | Check PWMxSEL jumpers                                            | Incorrect configuration of PWMALT pins prevent short-circuit test by enforcing dead time | For short-circuit test, set PWMLSEL (J9) and PWMHSEL (J10) to bypass dead time. See Section 3.4.3 for details.                                                                                                                                  |

| Bad SPI data, appears to repeat previous response | Check VSUP/VDD for undervoltage condition                        | VDD_UV latches SPI buffer contents, preventing updated fault reporting.                  | Check voltage provided at VDD pin (pin 3). On each read, compare the address from the sent command and response (a difference indicates that the SPI response is latched due to inactive). Read multiple addresses to ensure a good comparison. |

|                                                   | Check enable VCC/VEE is set to HIGH in SPIGen GUI; see Figure 13 | VCC/VEE can be enabled/disabled in software.                                             | Enable VCC/VEE from SPIGen.                                                                                                                                                                                                                     |

|                                                   | Check VCC for undervoltage                                       | Unpowered VCC prevents HV domain from updating data                                      | Tune VCC-GNDISO using R32 feedback                                                                                                                                                                                                              |

# 6 Schematics, board layout, and bill of materials

The board schematics, board layout, and bill of materials are available at  $\frac{http://}{www.nxp.com/FRDMGD3100HB8EVM.com} \, .$

#### 7 References

- [1] Tool summary page for FRDMGD3100HB8EVM http://www.nxp.com/FRDMGD3100HB8EVM.com

- [2] Tool summary page for FRDM-GD3100EVM <a href="http://www.nxp.com/FRDM-GD3100EVM">http://www.nxp.com/FRDM-GD3100EVM</a>

- [3] Product summary page for GD3100 device <a href="http://www.nxp.com/GD3100">http://www.nxp.com/GD3100</a>

# 8 Revision history

**Revision history**

| Revision | Date     | Description     |

|----------|----------|-----------------|

| v.1      | 20200804 | Initial version |

#### FRDMGD3100HB8EVM half-bridge evaluation board

# 9 Legal information

#### 9.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 9.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by

customer's third party customer(s). NXP does not accept any liability in this respect.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 9.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Kinetis — is a trademark of NXP B.V.

NXP — is a trademark of NXP B.V.

SafeAssure — is a trademark of NXP B.V.

# FRDMGD3100HB8EVM half-bridge evaluation board

# **Tables**

| Tab. 1.<br>Tab. 2. | Device features                                             |                    | Test point definition - high-side driver  Jumper definitions    | 11<br>12 |

|--------------------|-------------------------------------------------------------|--------------------|-----------------------------------------------------------------|----------|

| Tab. 3.            | Test point definitions-low voltage/low-side driver domains9 | Tab. 7.<br>Tab. 8. | LED interrupt indicators<br>Translator board jumper definitions |          |

| Figur              | res                                                         |                    |                                                                 |          |

| Fig. 1.            | Connecting FRDM-KL25Z,                                      | Fig. 8.            | LED interrupt indicators                                        | 13       |

|                    | FRDMGD3100HB8EVM and GD3100                                 | Fig. 9.            | Freedom development platform                                    | 14       |

|                    | translator board6                                           | Fig. 10.           | Translator board                                                |          |

| Fig. 2.            | FRDMGD3100HB8EVM board voltage and                          | Fig. 11.           | Evaluation board and system setup                               | 16       |

|                    | interface domains7                                          | Fig. 12.           | FRDM-KL25Z setup and interface                                  | 17       |

| Fig. 3.            | Key test point locations - Low voltage/low-                 | Fig. 13.           | SPIGen general view                                             | 19       |

|                    | side driver domains8                                        | Fig. 14.           | Mode registers and GPIO control view                            |          |

| Fig. 4.            | Test point definitions - high-side driver                   | Fig. 15.           | Configuration registers view                                    | 21       |

| Ū                  | domain10                                                    | Fig. 16.           | Status, mask, and REQADC registers view                         | 22       |

| Fig. 5.            | Power supply and jumper configuration 11                    | Fig. 17.           | Pulse test view                                                 | 22       |

| Fig. 6.            | FRDMGD3100HB8EVM bottom view12                              | Fig. 18.           | Single command view                                             |          |

| Fig. 7.            | Gate drive resistors13                                      | Fig. 19.           | Batch command view                                              |          |

#### FRDMGD3100HB8EVM half-bridge evaluation board

#### **Contents**

| 1     | FRDMGD3100HB8EVM                          | 1    |  |  |  |

|-------|-------------------------------------------|------|--|--|--|

| 2     | Getting started                           | 3    |  |  |  |

| 2.1   | Kit contents/packing list                 |      |  |  |  |

| 2.2   | Required equipment                        |      |  |  |  |

| 2.3   | System requirements                       |      |  |  |  |

| 3     | Getting to know the hardware              | 4    |  |  |  |

| 3.1   | Overview                                  |      |  |  |  |

| 3.2   | Board features                            | 4    |  |  |  |

| 3.3   | Device features                           |      |  |  |  |

| 3.4   | Board description                         |      |  |  |  |

| 3.4.1 | Low-voltage logic and control connector   |      |  |  |  |

| 3.4.2 | Test point definitions                    |      |  |  |  |

| 3.4.3 | Power supply and jumper configuration     | 11   |  |  |  |

| 3.4.4 | Bottom view                               |      |  |  |  |

| 3.4.5 | Gate drive resistors                      |      |  |  |  |

| 3.4.6 | LED interrupt indicators                  |      |  |  |  |

| 3.5   | Kinetis KL25Z Freedom board               | 14   |  |  |  |

| 3.6   | 3.3 V to 5.0 V translator board           | . 15 |  |  |  |

| 4     | Configuring the hardware                  |      |  |  |  |

| 5     | Installation and use of software tools    | .17  |  |  |  |

| 5.1   | Installing SPIGen on your computer        | . 17 |  |  |  |

| 5.2   | Configuring the FRDM-KL25Z microcode      | .17  |  |  |  |

| 5.3   | Using the SPIGen graphical user interface | .18  |  |  |  |

| 5.3.1 | Mode registers                            | 19   |  |  |  |

| 5.3.2 | Configuration register                    | . 20 |  |  |  |

| 5.3.3 | Status and mask register                  | 21   |  |  |  |

| 5.3.4 | Pulse test                                | 22   |  |  |  |

| 5.3.5 | Single command                            | .23  |  |  |  |

| 5.3.6 | Batch command                             | 23   |  |  |  |

| 5.4   | Troubleshooting                           | . 24 |  |  |  |

| 6     | Schematics, board layout, and bill of     |      |  |  |  |

|       | materials                                 | 26   |  |  |  |

| 7     | References                                | . 26 |  |  |  |

| 8     | Revision history                          | . 26 |  |  |  |

| 9     | Legal information                         | 27   |  |  |  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.